www.ti.com

System and Peripheral Control Registers

183

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Architecture

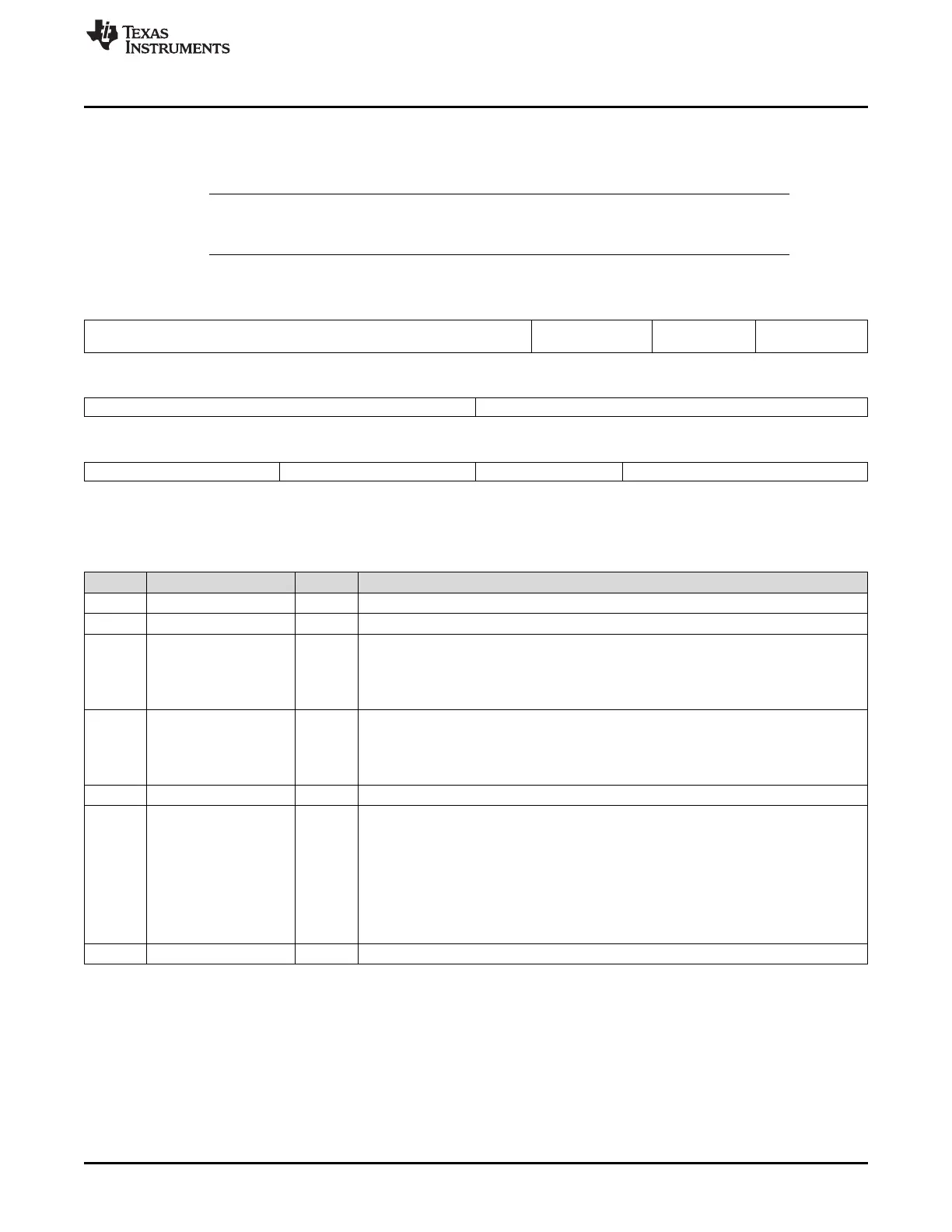

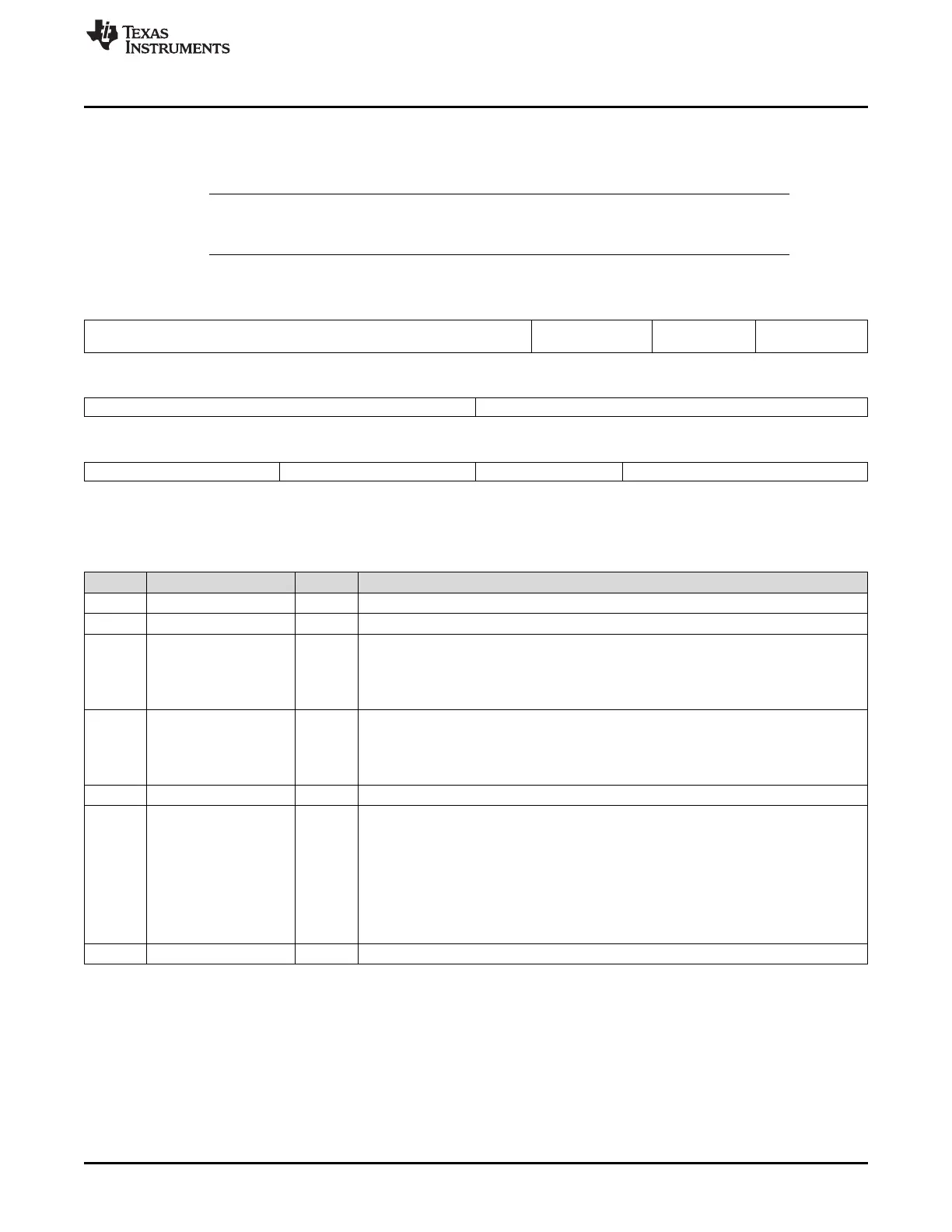

2.5.1.31 Clock Test Register (CLKTEST)

The CLKTEST register, shown in Figure 2-38 and described in Table 2-50, controls the clock signal that is

supplied to the ECLK pin for test and debug purposes.

NOTE: Clock Test Register Usage

This register should only be used for test and debug purposes.

Figure 2-38. Clock Test Register (CLKTEST) (offset = 8Ch)

31 27 26 25 24

Reserved TEST RANGEDET

CTRL

RANGEDET

ENASSEL

R-0 R/WP-0 R/WP-0 R/WP-0

23 20 19 16

Reserved CLK_TEST_EN

R-0 R/WP-Ah

15 12 11 8 7 5 4 0

Reserved SEL_GIO_PIN Reserved SEL_ECP_PIN

R-0 R/WP-0 R-0 R/WP-0

LEGEND: R/W = Read/Write; R = Read only; WP = Write in privileged mode only; -n = value after reset

Table 2-50. Clock Test Register (CLKTEST) Field Descriptions

Bit Field Value Description

31-27 Reserved 0 Reads return 0. Writes have no effect.

26 TEST 0 This bit is used for test purposes. It must be written to 0.

25 RANGEDETCTRL Range detection control. This bit's functionality is dependant on the state of the

RANGEDETENSSEL bit (Bit 24) of the CLKTEST register.

0 The clock monitor range detection circuitry (RANGEDETECTENABLE) is disabled.

1 The clock monitor range detection circuitry (RANGEDETECTENABLE) is enabled.

24 RANGEDETENASSEL Selects range detection enable. This bit resets asynchronously on power on reset.

0 The range detect enable is generated by the hardware in the clock monitor wrapper.

1 The range detect enable is controlled by the RANGEDETCTRL bit (Bit 25) of the

CLKTEST register.

23-20 Reserved 0 Reads return 0. Writes have no effect.

19-16 CLK_TEST_EN Clock test enable. This bit enables the clock going to the ECLK pin. This bit field enables

or disables clock going to device pins. Two pins in a device can get clock sources by

enabling CLK_TEST_EN bits. One pin is the ECP and second pin is a device specific GIO

pin. These bits need to asynchronously reset.

Note: The ECLK pin must also be placed into Functional mode by setting the

ECPCLKFUN bit to 1 in the SYSPC1 register.

5h Clock going to ECLK pin is enabled.

Others Clock going to ECLK pin is disabled.

15-12 Reserved 0 Reads return 0. Writes have no effect.

Loading...

Loading...