System and Peripheral Control Registers

www.ti.com

192

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Architecture

2.5.1.39 RAM Control Register (RAMGCR)

NOTE: The RAM_DFT_EN bits are for TI internal use only.

The contents of the RAM_DFT_EN field should not be changed.

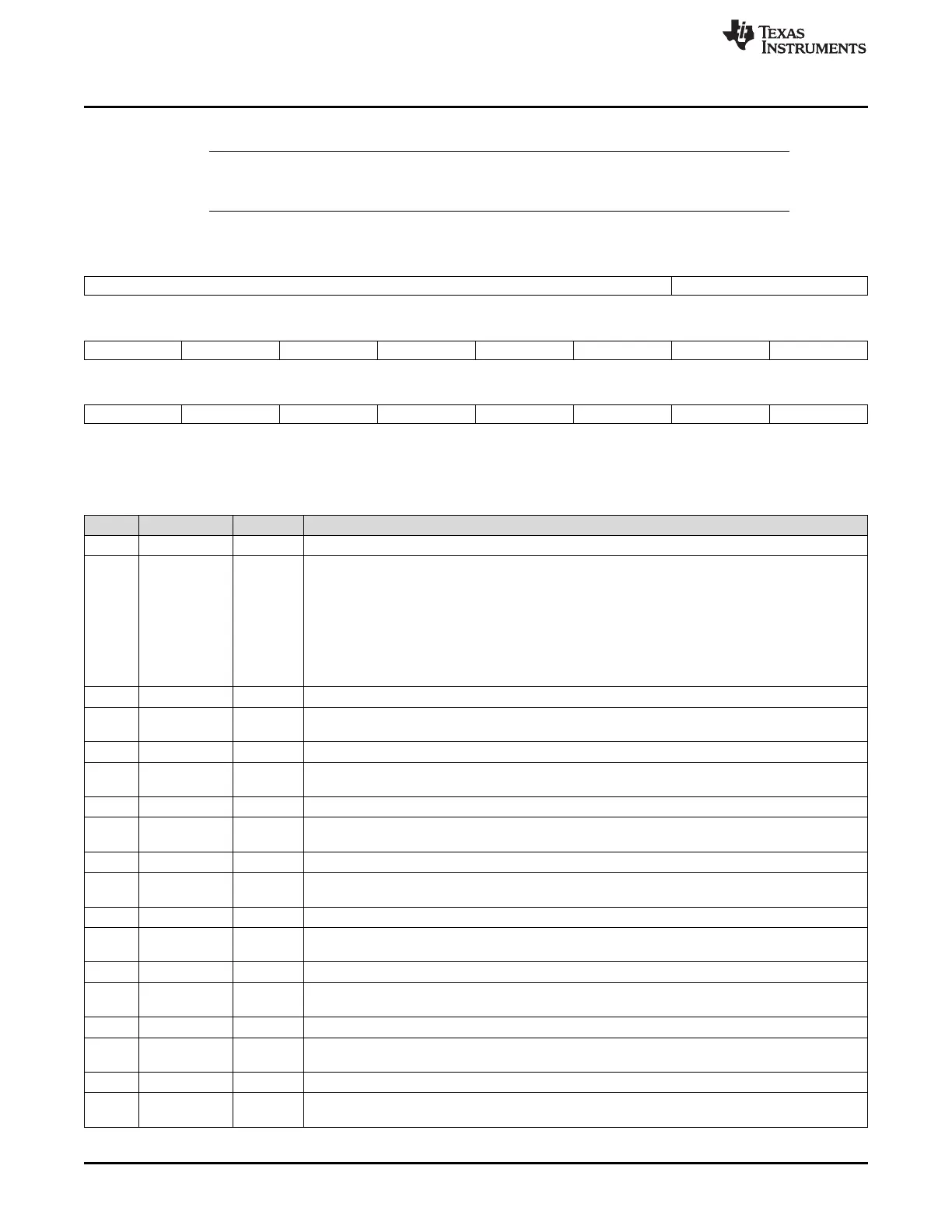

Figure 2-46. RAM Control Register (RAMGCR) (offset = C0h)

31 20 19 16

Reserved RAM_DFT_EN

R-0 R/WP-5h

15 14 13 12 11 10 9 8

Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved

R-0 R/WP-0 R-0 R/WP-0 R-0 R/WP-0 R-0 R/WP-0

7 6 5 4 3 2 1 0

Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved

R-0 R/WP-0 R-0 R/WP-0 R-0 R/WP-0 R-0 R/WP-0

LEGEND: R/W = Read/Write; R = Read only; WP = Write in privileged mode only; -n = value after reset

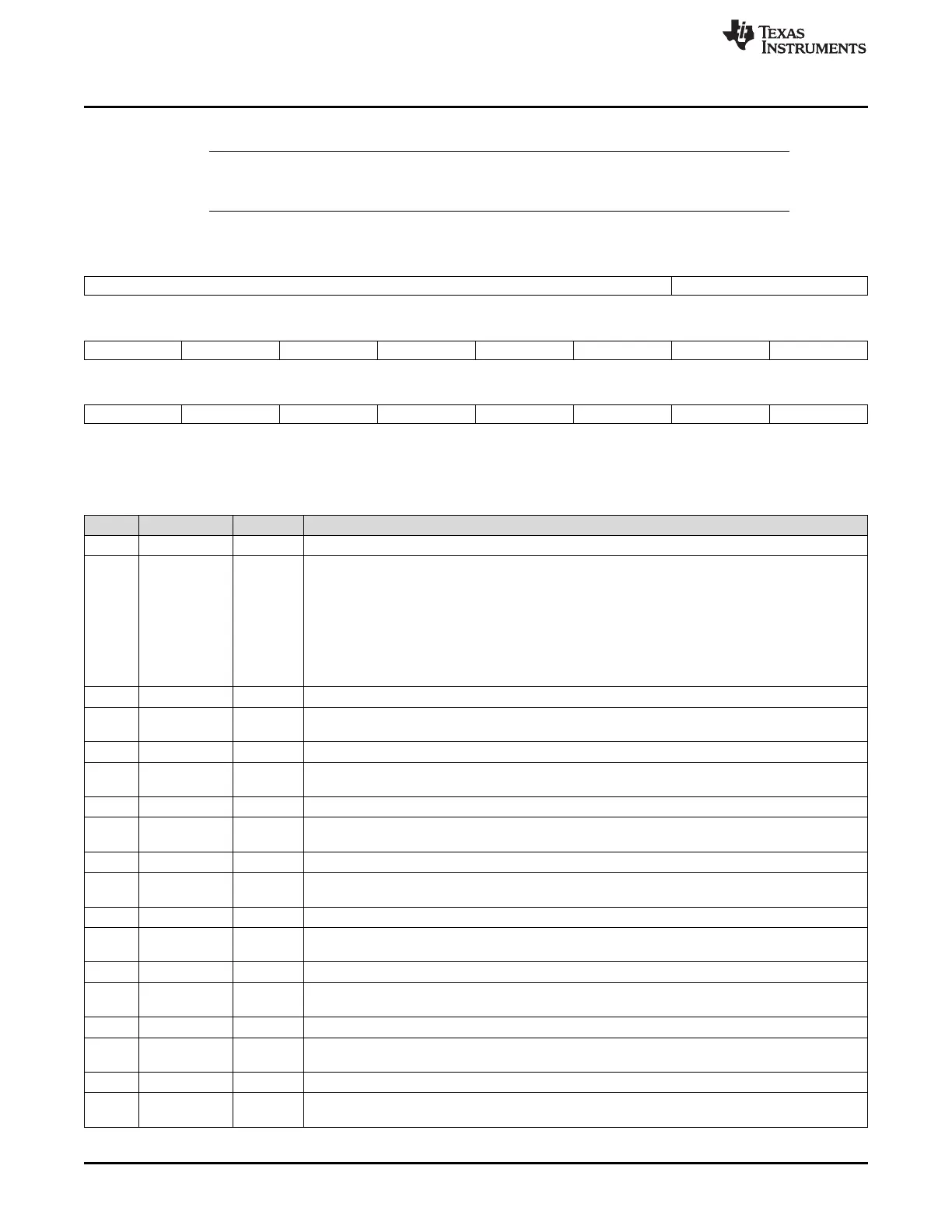

Table 2-58. RAM Control Register (RAMGCR) Field Descriptions

Bit Field Value Description

31-20 Reserved 0 Reads return 0. Writes have no effect.

19-16 RAM_DFT_EN Functional mode RAM DFT (Design For Test) port enable key.

Note: For TI internal use only.

Ah RAM DFT port is enabled.

Others RAM DFT port is disabled.

Note: It is recommended that a value of 5h be used to disable the RAM DFT port. This value

will give maximum protection from a bit-flip inducing event that would inadvertently enable

the controller.

15 Reserved 0 Reads return 0. Writes have no effect.

14 Reserved 0-1 Reads return 0 or 1 depends on what is written in privileged mode. The functionality of this bit is

unavailable in this device.

13 Reserved 0 Reads return 0. Writes have no effect.

12 Reserved 0-1 Reads return 0 or 1 depends on what is written in privileged mode. The functionality of this bit is

unavailable in this device.

11 Reserved 0 Reads return 0. Writes have no effect.

10 Reserved 0-1 Reads return 0 or 1 depends on what is written in privileged mode. The functionality of this bit is

unavailable in this device.

9 Reserved 0 Reads return 0. Writes have no effect.

8 Reserved 0-1 Reads return 0 or 1 depends on what is written in privileged mode. The functionality of this bit is

unavailable in this device.

7 Reserved 0 Reads return 0. Writes have no effect.

6 Reserved 0-1 Reads return 0 or 1 depends on what is written in privileged mode. The functionality of this bit is

unavailable in this device.

5 Reserved 0 Reads return 0. Writes have no effect.

4 Reserved 0-1 Reads return 0 or 1 depends on what is written in privileged mode. The functionality of this bit is

unavailable in this device.

3 Reserved 0 Reads return 0. Writes have no effect.

2 Reserved 0-1 Reads return 0 or 1 depends on what is written in privileged mode. The functionality of this bit is

unavailable in this device.

1 Reserved 0 Reads return 0. Writes have no effect.

0 Reserved 0-1 Reads return 0 or 1 depends on what is written in privileged mode. The functionality of this bit is

unavailable in this device.

Loading...

Loading...