www.ti.com

System and Peripheral Control Registers

193

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Architecture

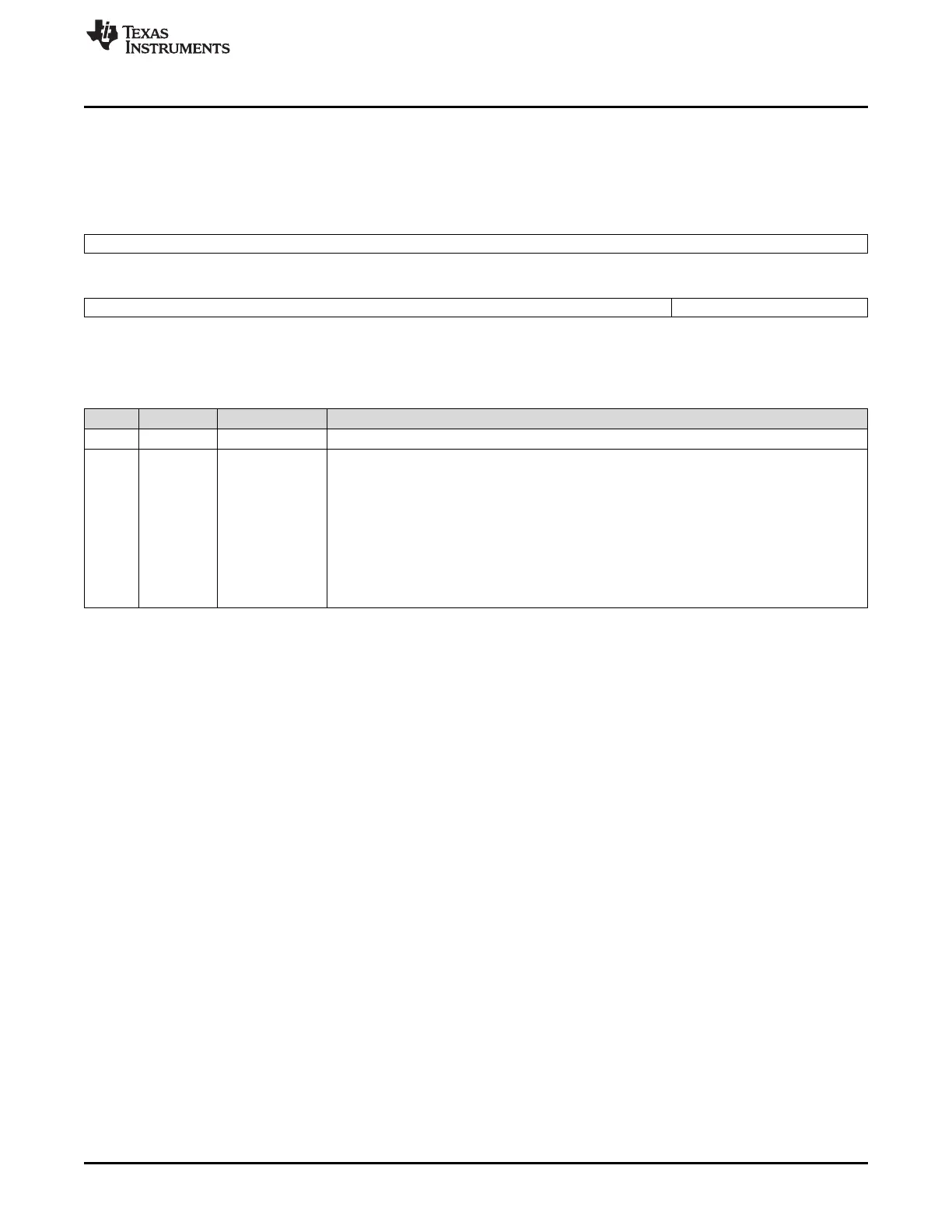

2.5.1.40 Bus Matrix Module Control Register 1 (BMMCR1)

The BMMCR1 register, shown in Figure 2-47 and described in Table 2-59, allows RAM and Program

(Flash) memory addresses to be swapped.

Figure 2-47. Bus Matrix Module Control Register 1 (BMMCR) (offset = C4h)

31 16

Reserved

R-0

15 4 3 0

Reserved MEMSW

R-0 R/WP-Ah

LEGEND: R/W = Read/Write; R = Read only; WP = Write in privileged mode only; -n = value after reset

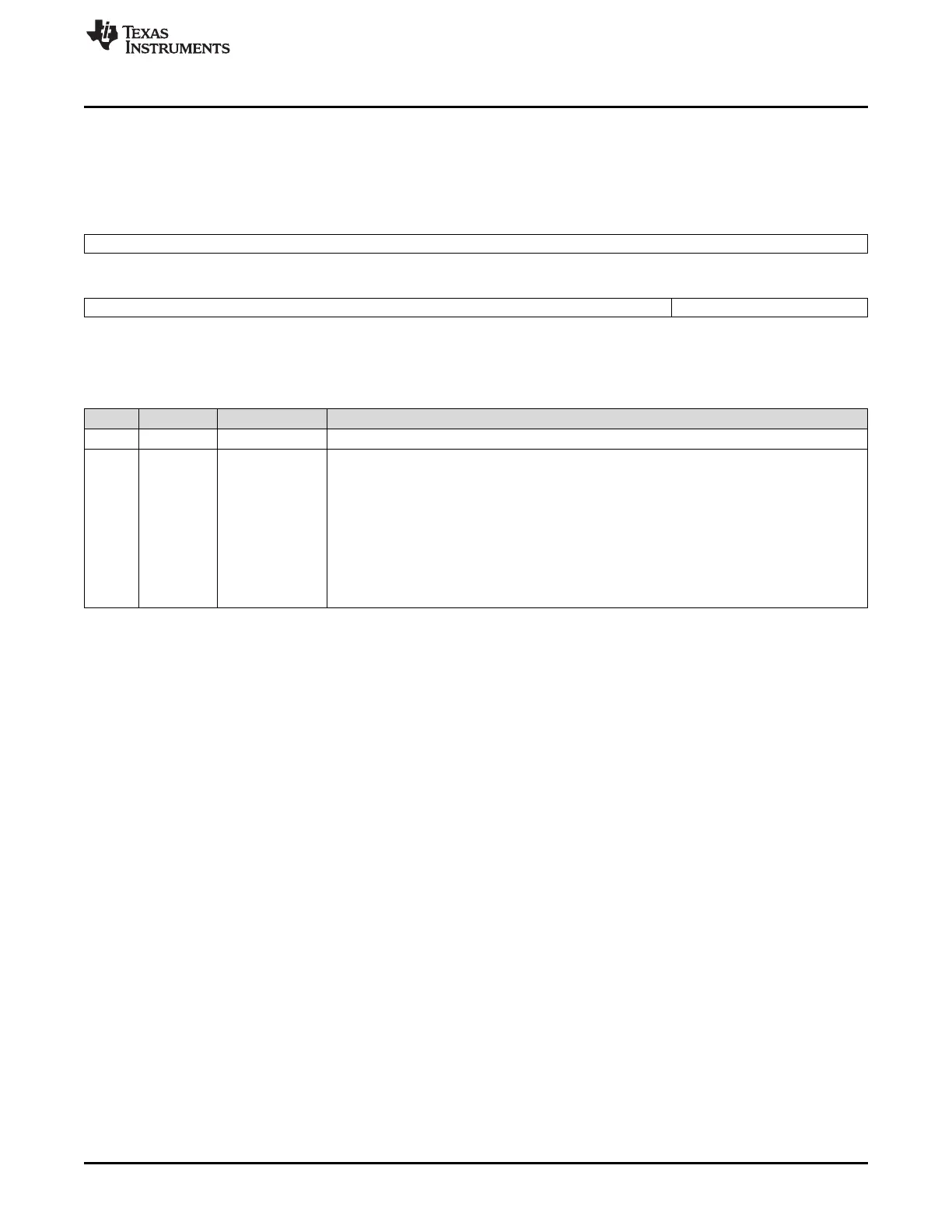

Table 2-59. Bus Matrix Module Control Register 1 (BMMCR) Field Descriptions

Bit Field Value Description

31-4 Reserved 0 Reads return 0. Writes have no effect.

3-0 MEMSW Memory swap key.

Note: A CPU reset must be issued after the memory swap key has been changed for the

memory swap to occur. A CPU reset can be initiated by changing the state of the CPU

RESET bit in the CPURSTCR register.

Ah Default memory-map:

Program memory (Flash) starts at address 0. eSRAM starts at address 800 0000h.

5h Swapped memory-map:

eSRAM starts at address 0. Program memory (Flash) starts at address 800 0000h.

Others The device memory-map is unchanged.

Loading...

Loading...