System and Peripheral Control Registers

www.ti.com

194

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Architecture

2.5.1.41 CPU Reset Control Register (CPURSTCR)

The CPURSTCR register shown in Figure 2-48 and described in Table 2-60 allows a reset to the Cortex-

R5F CPU to be generated.

NOTE: The register bits in CPURSTCR are designated as high-integrity bits and have been

implemented with error-correcting logic such that each bit, although read and written as a

single bit, is actually a multi-bit key with error correction capability. As such, single-bit flips

within the “key” can be corrected allowing protection of the system as a whole. An error

detected is signaled to the ESM module.

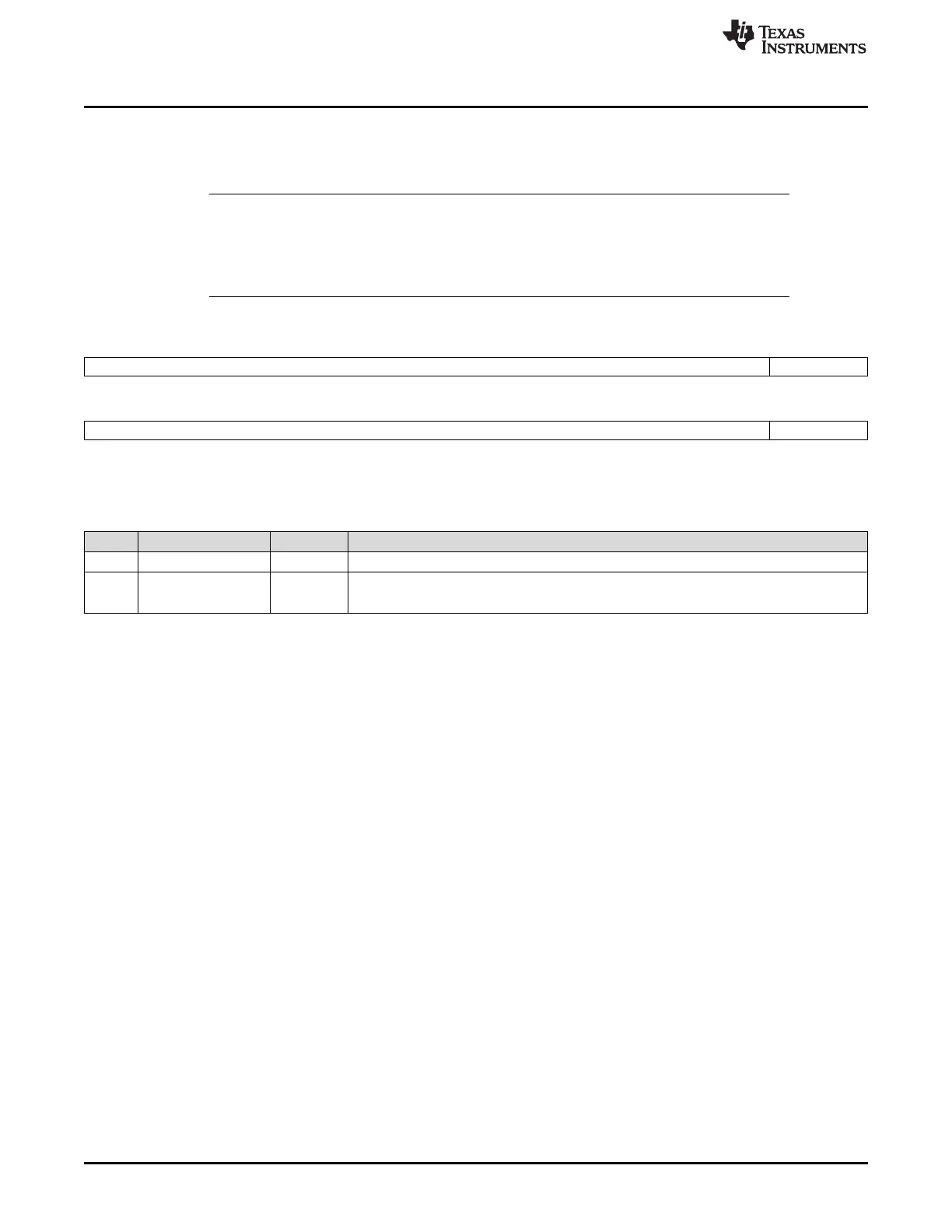

Figure 2-48. CPU Reset Control Register (CPURSTCR) (offset = CCh)

31 17 16

Reserved Reserved

R-0 R/WP-0

15 1 0

Reserved CPU RESET

R-0 R/WP-0

LEGEND: R/W = Read/Write; R = Read only; WP = Write in privileged mode only; -n = value after reset

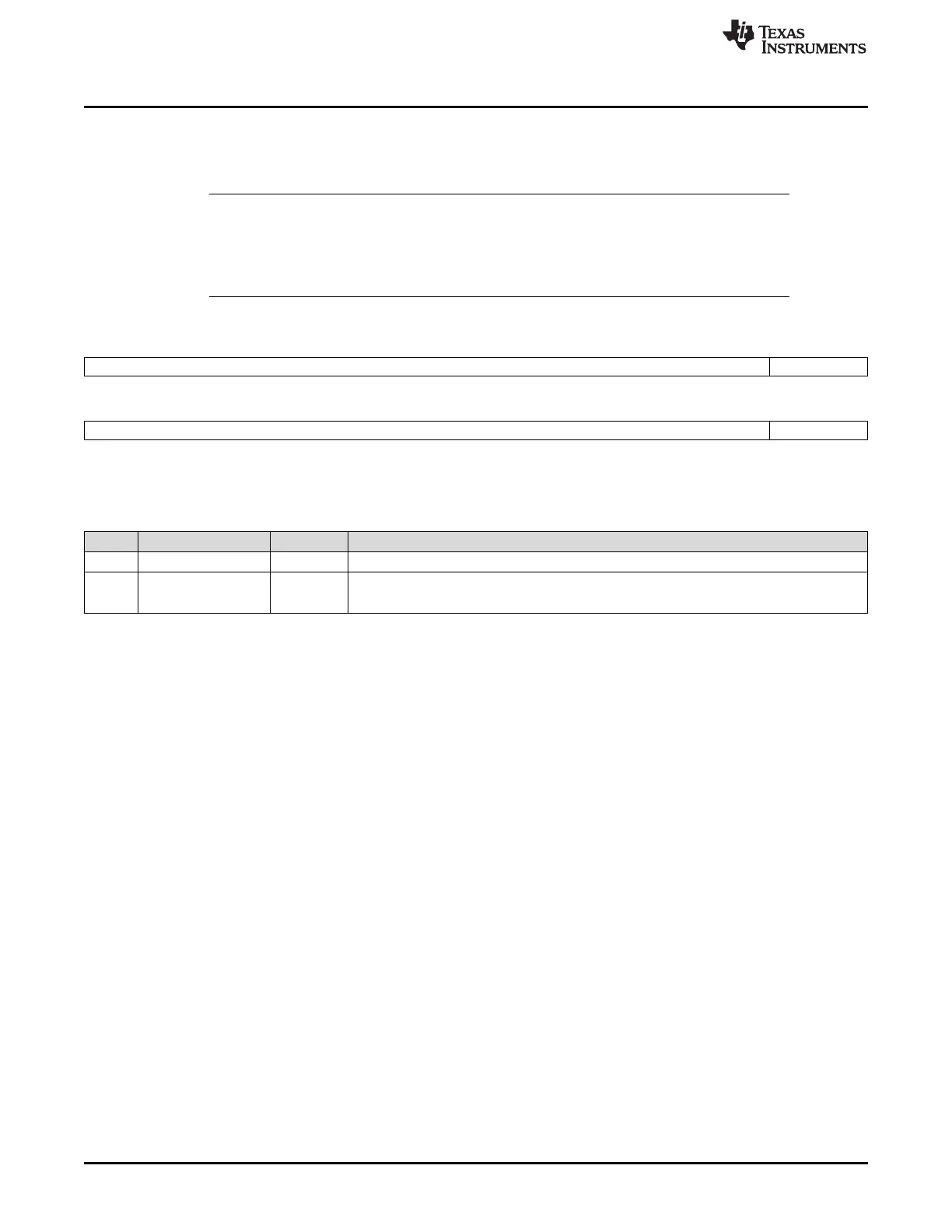

Table 2-60. CPU Reset Control Register (CPURSTGCR) Field Descriptions

Bit Field Value Description

31-1 Reserved 0 Reads return 0. Writes have no effect.

0 CPU RESET CPU RESET.

Only the CPU is reset whenever this bit is toggled. There is no system reset.

Loading...

Loading...