www.ti.com

System and Peripheral Control Registers

199

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Architecture

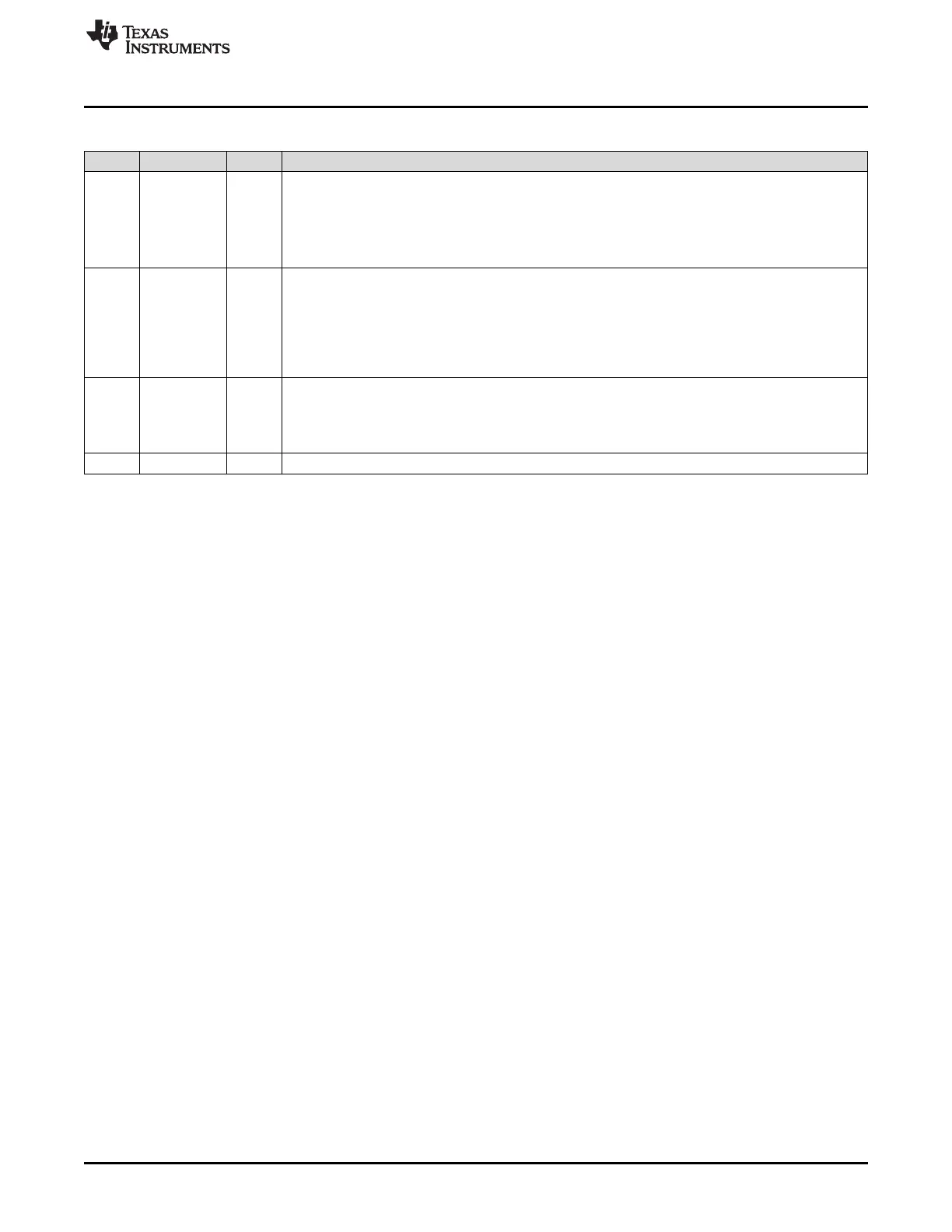

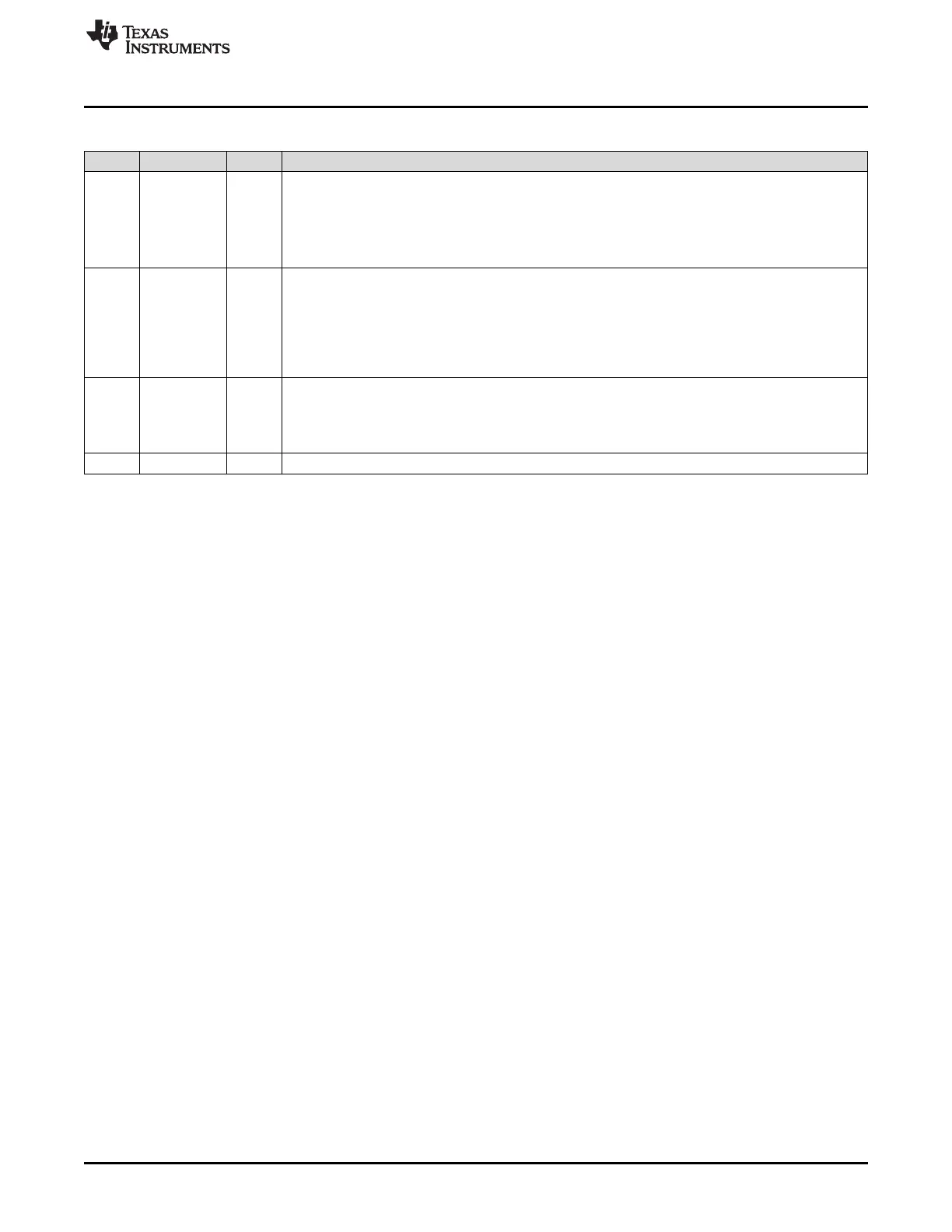

Table 2-65. System Exception Status Register (SYSESR) Field Descriptions (continued)

Bit Field Value Description

5 CPURST CPU reset flag. This bit is set when the CPU is reset. Write 1 will clear this bit. Write 0 has no effect.

Note: A CPU reset can be initiated by the CPU self-test controller (LBIST) or by toggling the CPU

RESET bit field in CPURSTCR register.

0 No CPU reset has occurred.

1 A CPU reset occurred.

4 SWRST Software reset flag. This bit is set when a software system reset has occurred. Write 1 will clear this bit.

Write 0 has no effect.

Note: A software system reset can be initiated by writing to the RESET bits in the SYSECR

register.

0 No software reset has occurred.

1 A software reset occurred.

3 EXTRST External reset flag. This bit is set when a reset is caused by the external reset pin nRST or by any reset

that also asserts the nRST pin (PORST, OSCRST, WDRST, WD2RST, and SWRST).

0 The external reset pin has not asserted a reset.

1 A reset has been caused by the external reset pin.

2-0 Reserved 0 Reads return 0. Writes have no effect.

Loading...

Loading...