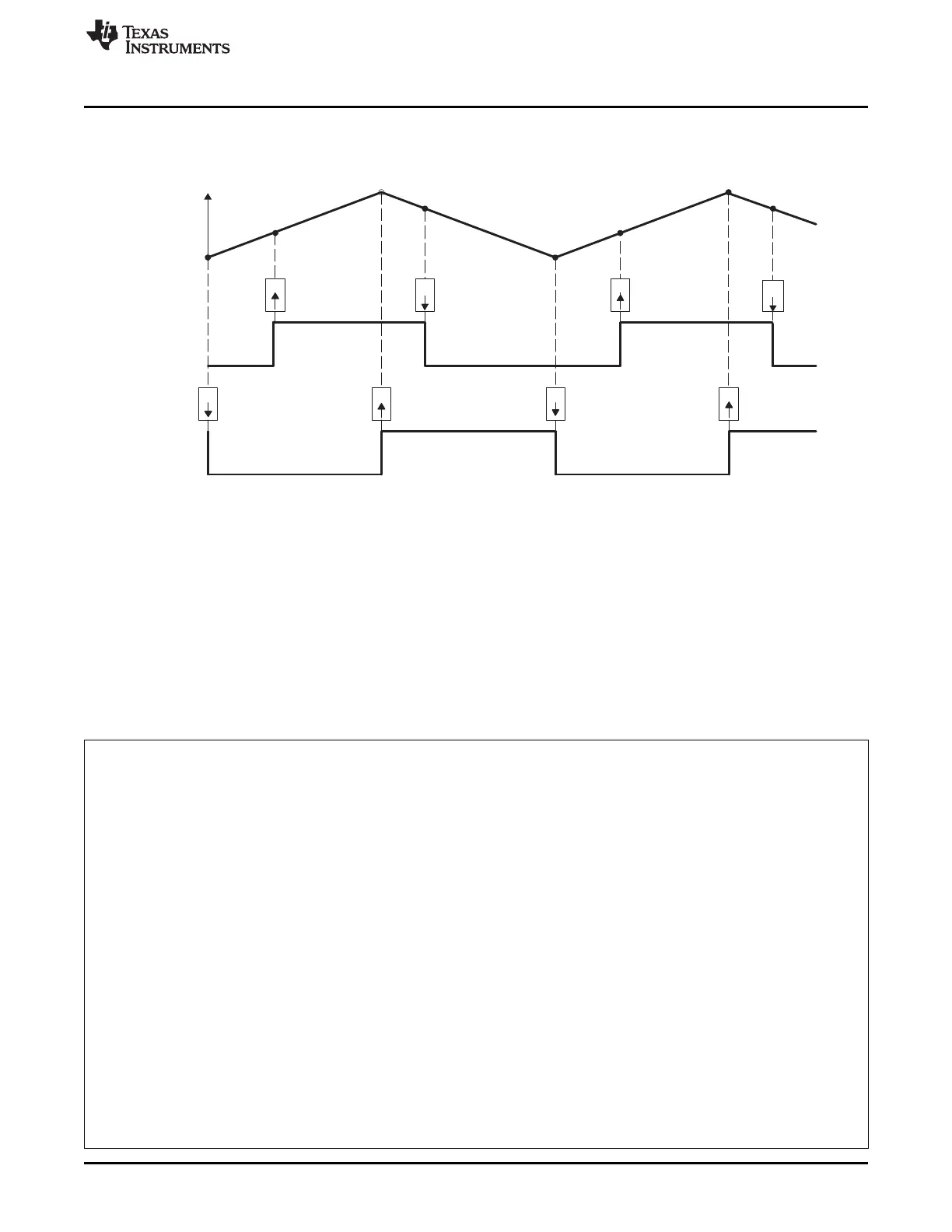

Z P Z P

TBCTR

EPWMxA

EPWMxB

CA CA

CB

CB

www.ti.com

ePWM Submodules

2027

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Enhanced Pulse Width Modulator (ePWM) Module

Figure 35-26. Up-Down-Count, Dual Edge Asymmetric Waveform, With Independent Modulation on

EPWMxA—Active Low

A PWM period = 2 × TBPRD × TBCLK

B Rising edge and falling edge can be asymmetrically positioned within a PWM cycle. This allows for pulse placement

techniques.

C Duty modulation for EPWMxA is set by CMPA and CMPB.

D Low time duty for EPWMxA is proportional to (CMPA + CMPB).

E To change this example to active high, CMPA and CMPB actions need to be inverted (i.e., Set ! Clear and Clear Set).

F Duty modulation for EPWMxB is fixed at 50% (utilizes spare action resources for EPWMxB)

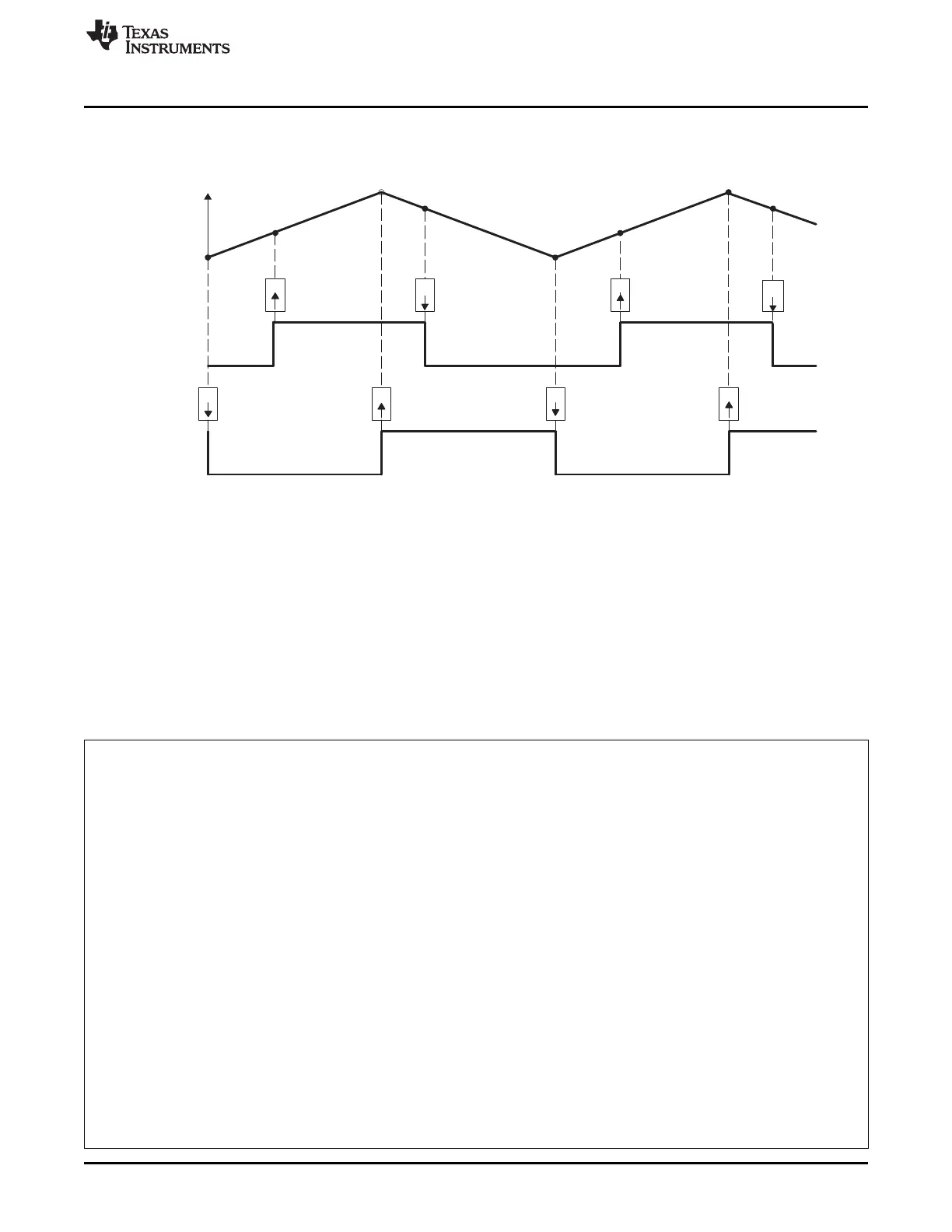

Example 35-6 contains a code sample showing initialization and run time for the waveforms in Figure 35-

26.

Example 35-6. Code Sample for Figure 35-26

// Initialization Time

// = = = = = = = = = = = = = = = = = = = = = = = =

EPwm1Regs.TBPRD = 600; // Period = 2 ´ 600 TBCLK counts

EPwm1Regs.CMPA.half.CMPA = 250; // Compare A = 250 TBCLK counts

EPwm1Regs.CMPB = 450; // Compare B = 450 TBCLK counts

EPwm1Regs.TBPHS = 0; // Set Phase register to zero

EPwm1Regs.TBCTR = 0; // clear TB counter

EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Symmetric

EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; // Phase loading disabled

EPwm1Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm1Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_DISABLE;

EPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // TBCLK = VCLK3

EPwm1Regs.TBCTL.bit.CLKDIV = TB_DIV1;

EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // load on CTR = Zero

EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO; // load on CTR = Zero

EPwm1Regs.AQCTLA.bit.CAU = AQ_SET;

EPwm1Regs.AQCTLA.bit.CBD = AQ_CLEAR;

EPwm1Regs.AQCTLB.bit.ZRO = AQ_CLEAR;

EPwm1Regs.AQCTLB.bit.PRD = AQ_SET;

// Run Time

// = = = = = = = = = = = = = = = = = = = = = = = =

EPwm1Regs.CMPA.half.CMPA = EdgePosA; // adjust duty for output EPWM1A only

EPwm1Regs.CMPB = EdgePosB;

Loading...

Loading...