www.ti.com

ePWM Registers

2103

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Enhanced Pulse Width Modulator (ePWM) Module

35.4.8.3 Digital Compare Filter Control Register (DCFCTL)

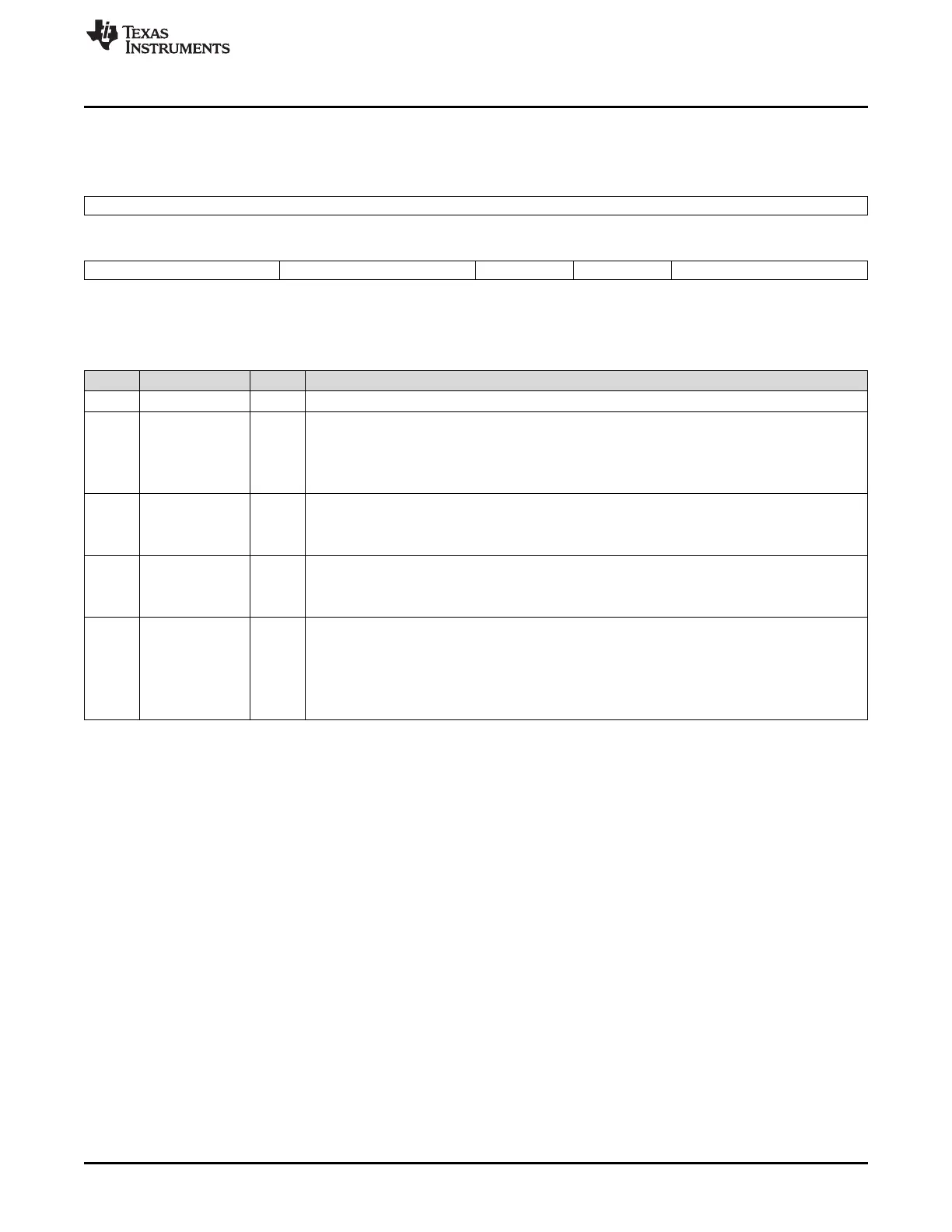

Figure 35-93. Digital Compare Filter Control Register (DCFCTL) [offset = 64h]

15 8

Reserved

R-0

7 6 5 4 3 2 1 0

Reserved PULSESEL BLANKINV BLANKE SRCSEL

R-0 R/W-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

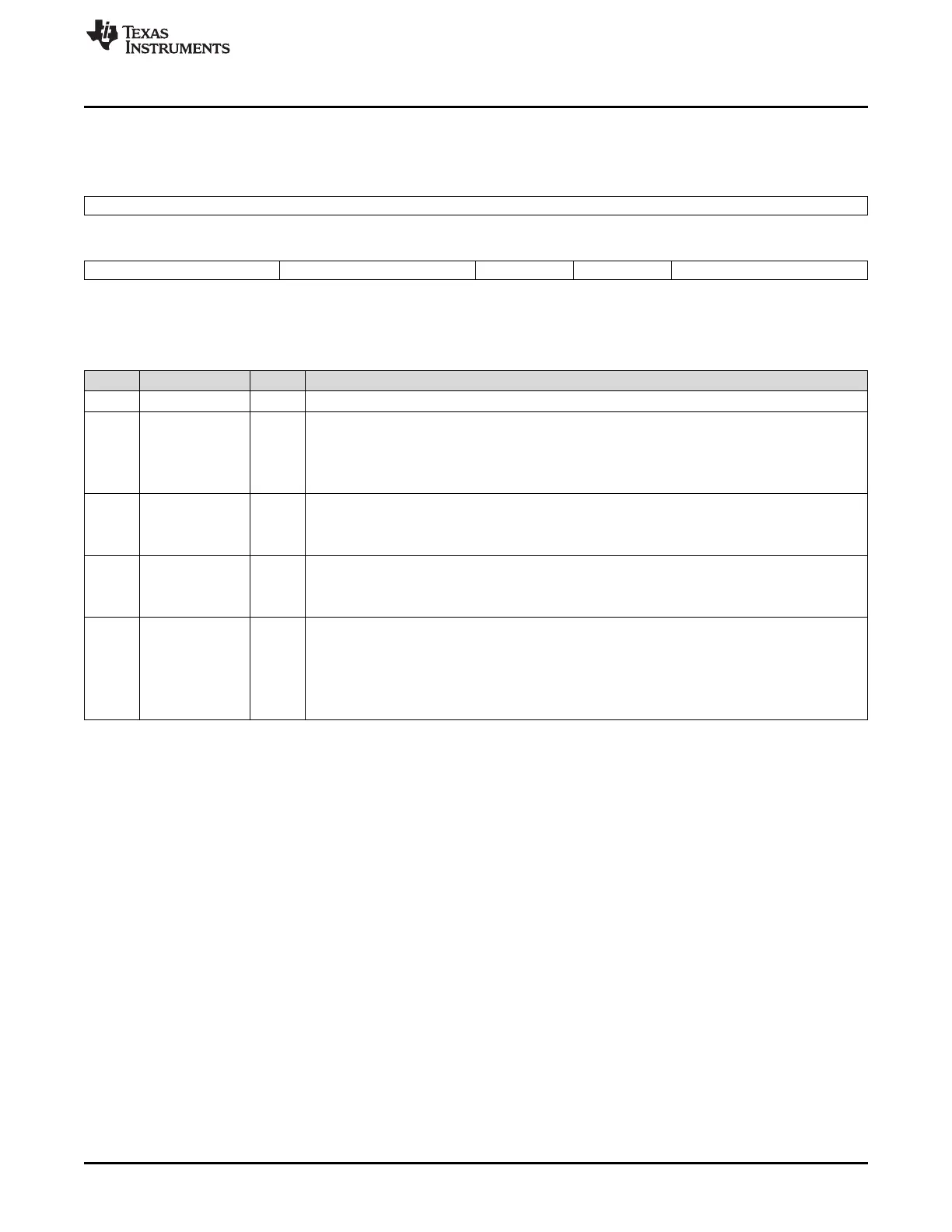

Table 35-53. Digital Compare Filter Control Register (DCFCTL) Field Descriptions

Bit Field Value Description

15-6 Reserved 0 Reserved

5-4 PULSESEL Pulse Select For Blanking & Capture Alignment.

0 Time-base counter equal to period (TBCTR = TBPRD)

1h Time-base counter equal to zero (TBCTR = 0x0000)

2h-3h Reserved

3 BLANKINV Blanking Window Inversion.

0 Blanking window is not inverted.

1 Blanking window is inverted.

2 BLANKE Blanking Window Enable.

0 Blanking window is disabled.

1 Blanking window is enabled.

1-0 SRCSEL Filter Block Signal Source Select.

0 Source Is DCAEVT1 Signal.

1h Source Is DCAEVT2 Signal.

2h Source Is DCBEVT1 Signal.

3h Source Is DCBEVT2 Signal.

Loading...

Loading...