Control Registers

www.ti.com

2116

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Data Modification Module (DMM)

36.3.1 DMM Global Control Register (DMMGLBCTRL)

With this register the basic operation of the module is selected.

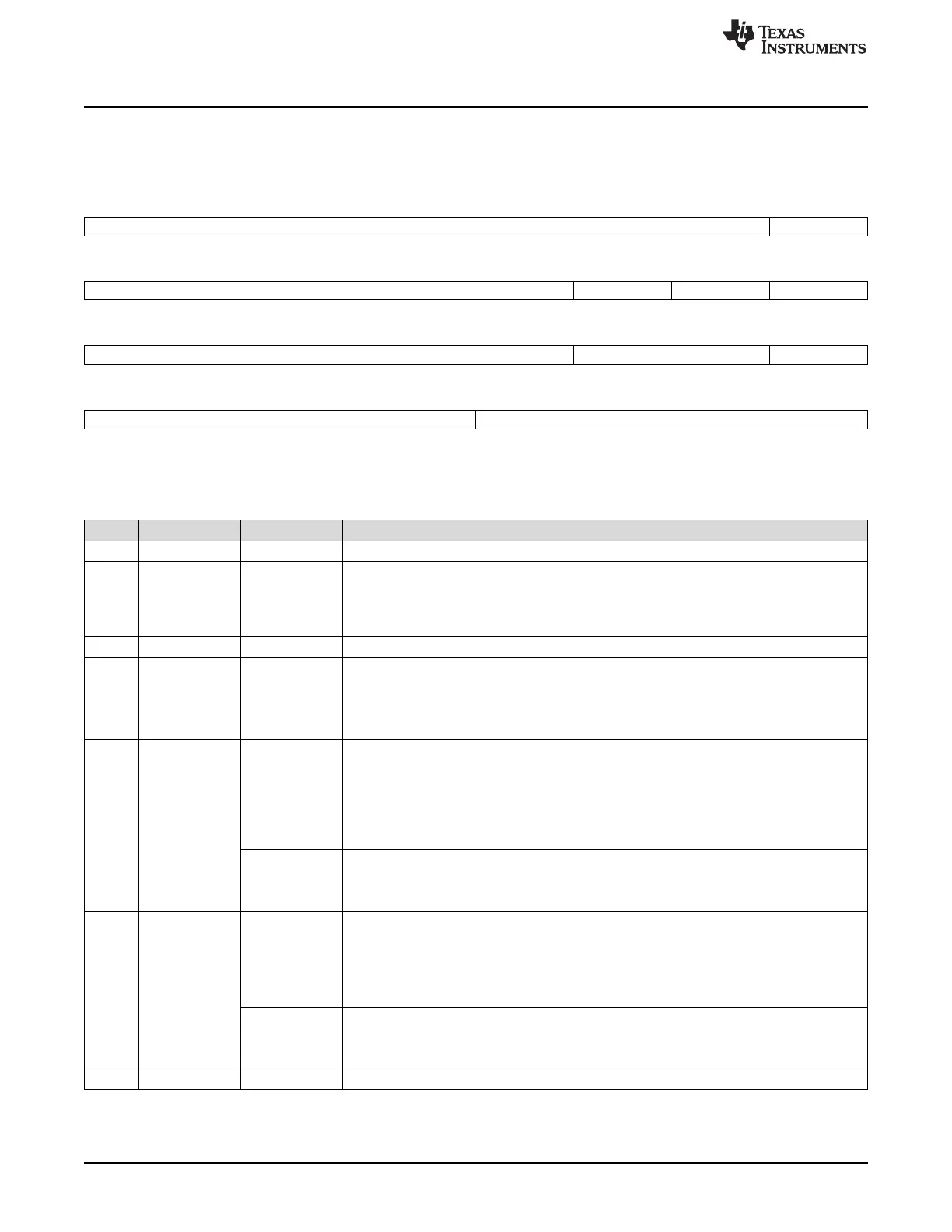

Figure 36-7. DMM Global Control Register (DMMGLBCTRL) [offset = 00h]

31 25 24

Reserved BUSY

R-0 R-0

23 19 18 17 16

Reserved CONTCLK COS RESET

R-0 R/WP-0 R/WP-0 R/WP-0

15 11 10 9 8

Reserved DDM_WIDTH TM_DDM

R-0 R/WP-0 R/WP-0

7 4 3 0

Reserved ON/OFF

R-0 R/WP-5h

LEGEND: R/W = Read/Write; R = Read only; WP = Write in privileged mode only; -n = value after reset

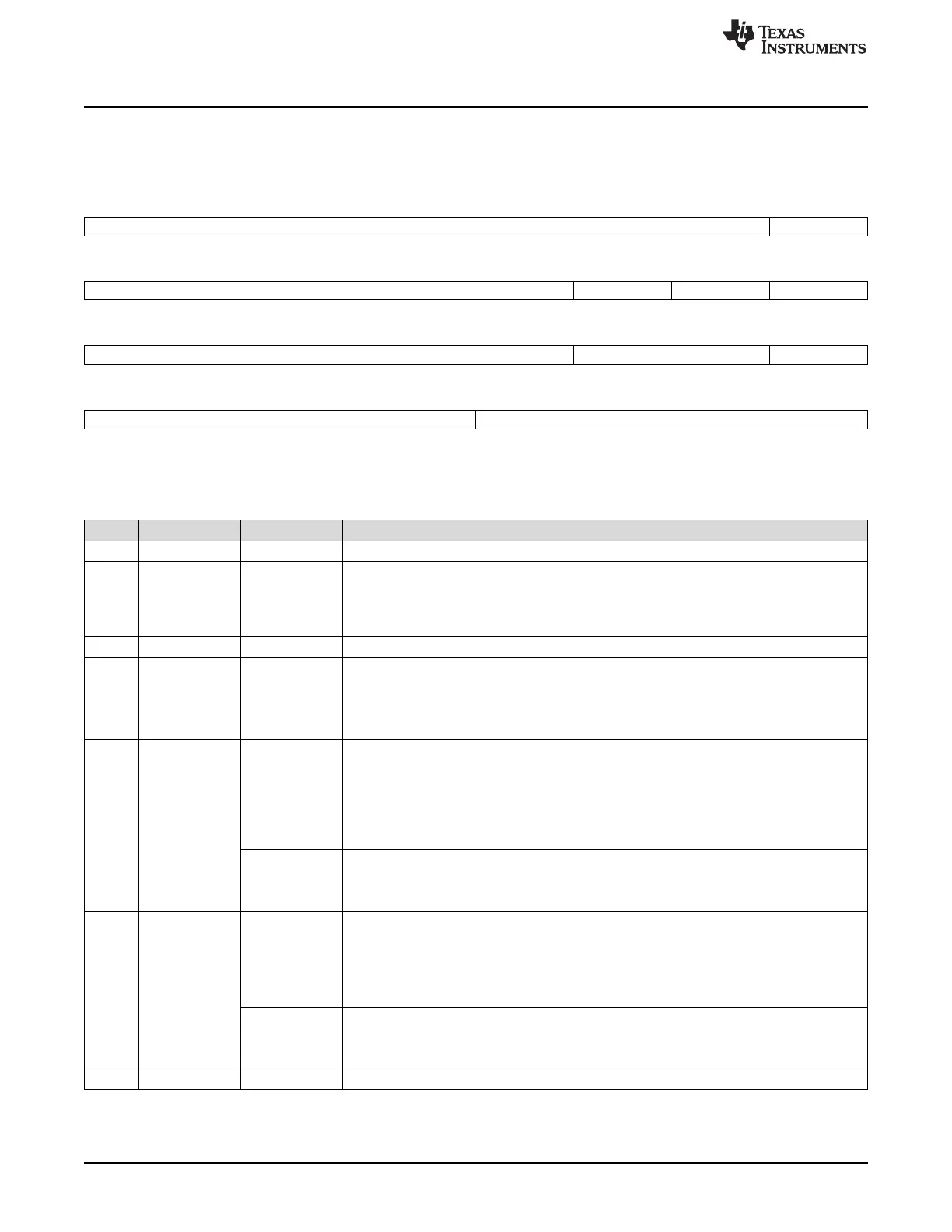

Table 36-7. DMM Global Control Register (DMMGLBCTRL) Field Descriptions

Bit Field Value Description

31-25 Reserved 0 Reads returns 0. Writes have no effect.

24 BUSY Busy indicator.

0 The DMM does not currently receive data and has no data in its internal buffers, which

needs to be transferred.

1 The module is currently receiving data, or has data in its internal buffers.

23-19 Reserved 0 Reads returns 0. Writes have no effect.

18 CONTCLK Continuous DMMCLK input.

User and privilege mode read, privilege mode write:

0 DMMCLK is expected to be suspended between two packets.

1 DMMCLK is expected to be free running between packets.

17 COS Continue on suspend. Influences behavior of module while in debug mode. In all cases the

corresponding interrupt will be set.

User and privilege mode (read):

0 Packets will not be received during debug mode. Before entering debug mode, the ongoing

reception of a packet will be finished and the value will be written to the destination.

1 Continue receiving packets and update destination, while in debug mode.

Privilege mode (write):

0 Disable data reception while in debug mode.

1 Enable data reception while in debug mode.

16 RESET Reset. This bit resets the state machine and the registers to its reset value, except the

RESET bit itself. It must be cleared by writing to it.

User and privilege mode (read):

0 No reset of DMM module.

1 Reset of DMM module.

Privilege mode (write):

0 No reset of DMM module.

1 Reset DMM module to its reset state.

15-11 Reserved 0 Reads returns 0. Writes have no effect.

Loading...

Loading...