www.ti.com

Control Registers

2117

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Data Modification Module (DMM)

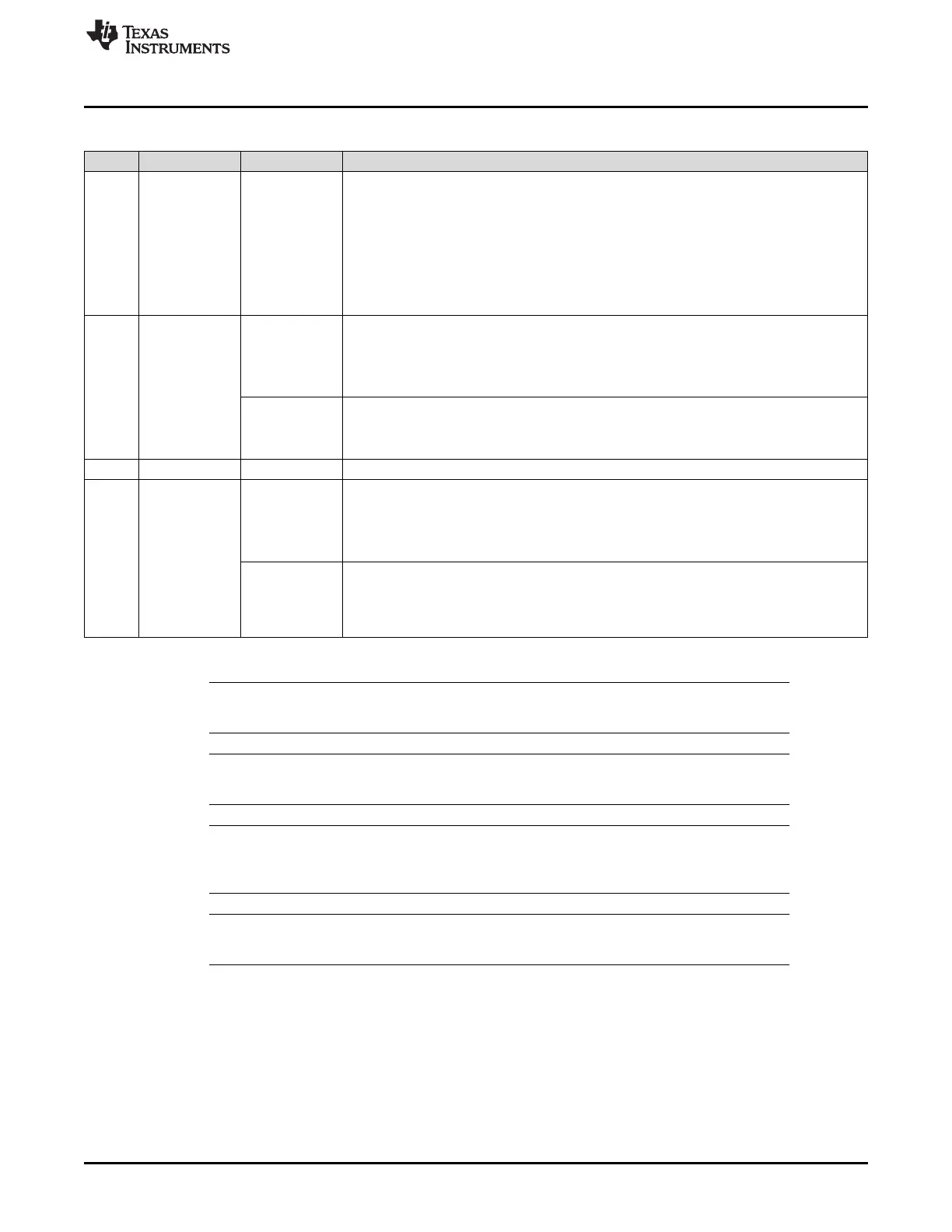

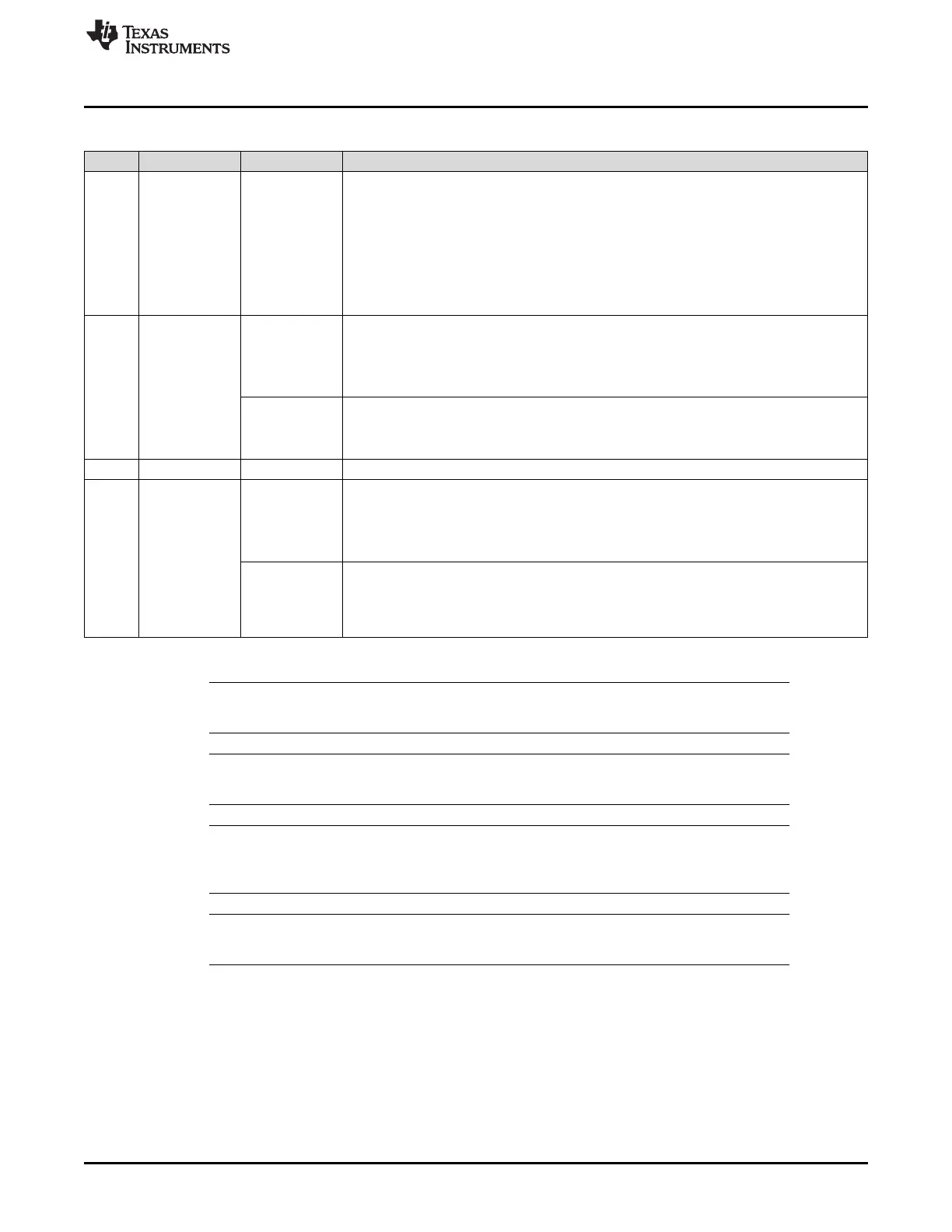

Table 36-7. DMM Global Control Register (DMMGLBCTRL) Field Descriptions (continued)

Bit Field Value Description

10-9 DDM_WIDTH Packet Width in direct data mode.

User and privilege mode read and privilege mode write operation:

Bit Encoding Transfer Size

0 8 bit

1h 16 bit

2h 32 bit

3h Reserved

8 TM_DMM Packet Format.

User and privilege mode (read):

0 The DMM module assumes packets in trace mode definition.

1 The DMM module assumes packets in direct data mode definition.

Privilege mode (write):

0 Enable trace mode.

1 Enable direct data mode.

7-4 Reserved 0 Reads returns 0. Writes have no effect.

3-0 ON/OFF Switch module on or off

User and privilege mode (read):

All other The DMM module does not receive data.

Ah The DMM module receives data and writes it to the buffer.

Privilege mode (write):

All other Disable receive/write operations. Packets in reception, will still be finished.

Ah Enable receive/write operations. Packets will be received 1 HCLK cycle after enabling the

module.

NOTE: It is recommended to write 5h to ON/OFF to avoid having a soft error inadvertently enabling

the module when a single bit flips.

NOTE: Registers that affect the operation of the module, should be only programmed when the

BUSY bit is 0 and the ON/OFF bits are not Ah.

NOTE: If the module was in operation, turned off (ON/OFF = all other than Ah) and then turned on

(ON/OFF = Ah) again, it is recommended to perform a reset (RESET = 1) of the module

before switching it on. This avoids that the state machine is held in an unrecoverable state.

NOTE: A write to these register bits while receiving a packet will not have any effect on the received

packet. The mode change will be performed after the packet is received

Loading...

Loading...