www.ti.com

RTP Control Registers

2165

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

RAM Trace Port (RTP)

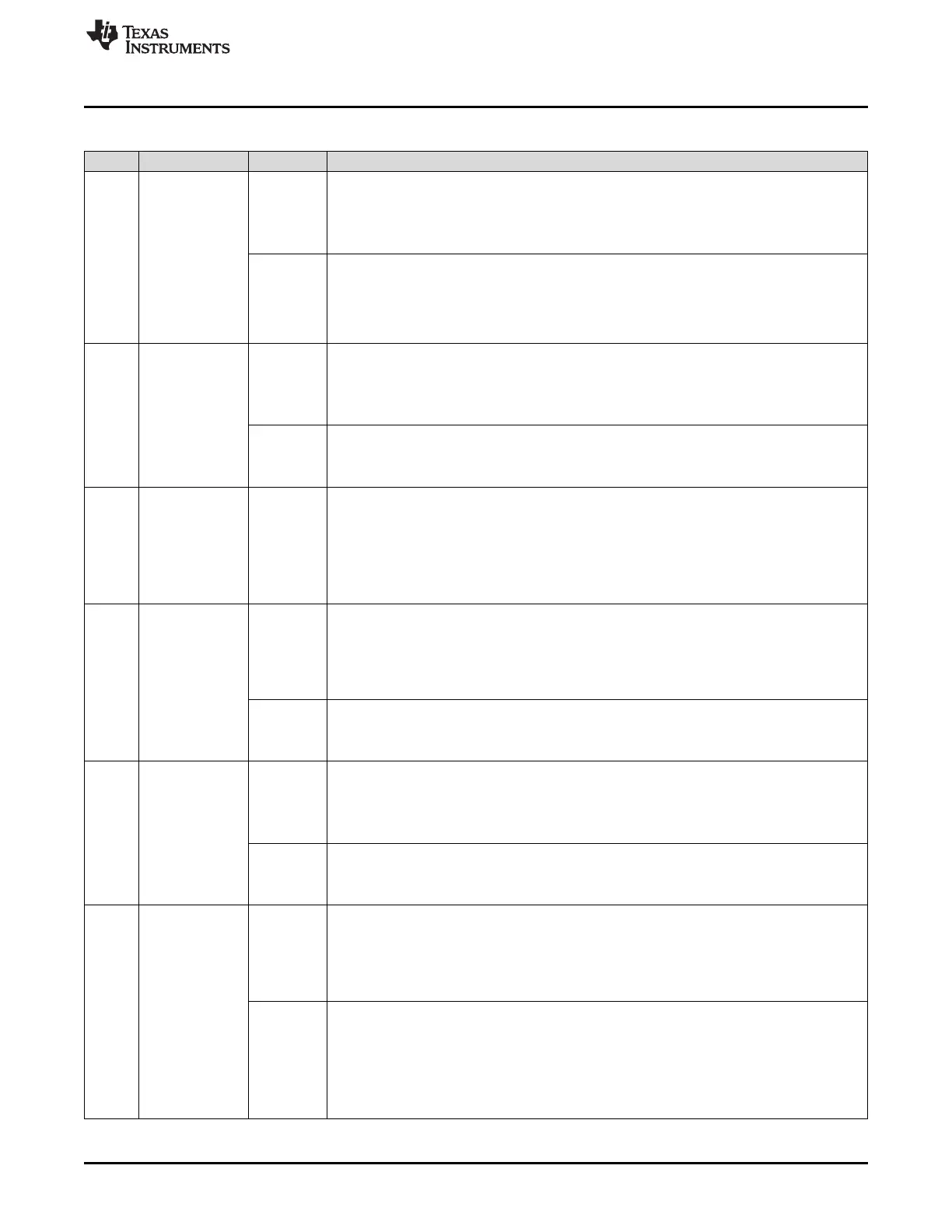

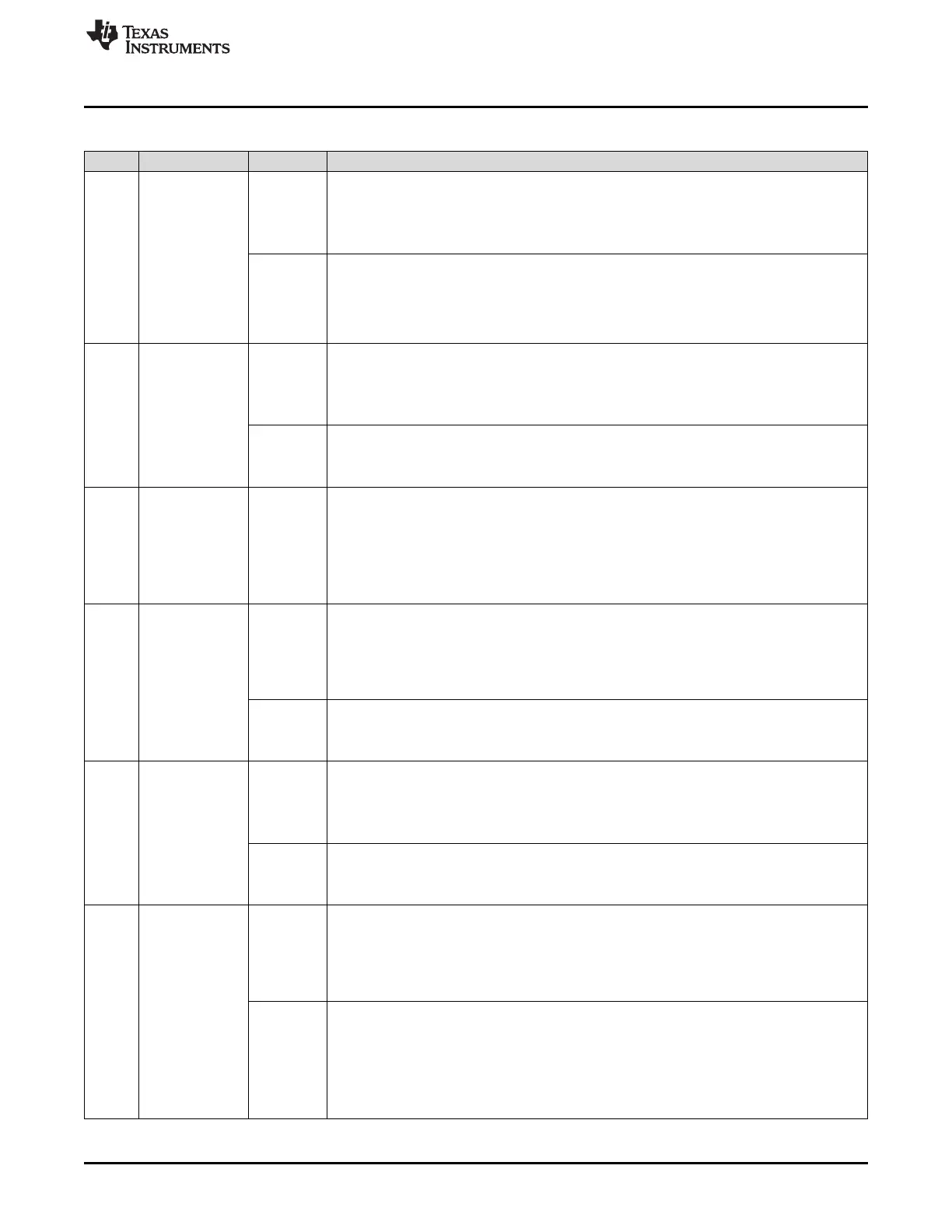

Table 37-8. RTP Global Control Register (RTPGLBCTRL) Field Descriptions (continued)

Bit Field Value Description

11 DDM_RW Direct data mode.

Read:

0 Read tracing in Direct Data Mode is enabled.

1 Write tracing in Direct Data Mode to DDMW register is enabled.

Write in Privilege:

0 Enable read tracing in Direct Data Mode. The RW bits in the RTPRAMxREGy registers to be

ignored.

1 Write tracing in Direct Data Mode to DDMW register is enabled. The RW bits in the

RTPRAMxREGy registers are to be ignored.

10 TM_DDM Trace Mode or Direct Data Mode.

Read:

0 Module is configured in Trace Mode.

1 Module is configured in Direct Data Mode.

Write in Privilege:

0 Configure module to Trace Mode.

1 Configure module to Direct Data Mode.

9-8 PW Port width. This bit field configures the RTP to the desired port width. Pins that are not used for

functional mode can be used as GIO pins. See Table 37-10 for which pins are used for the port.

0 RTP is 2 pins wide.

1h RTP is 4 pins wide.

2h RTP is 8 pins wide.

3h RTP is 16 pins wide.

7 RESET This bit resets the state machine and the registers to their reset value. This reset ensures that

no data left in the FIFOs is shifted out after switching on the module with the ON/OFF bit.

Read:

0 RTP module is out of reset.

1 RTP module is in reset.

Write in Privilege:

0 Do not reset the module.

1 Reset the module.

6 CONTCLK Continuous RTPCLK enable.

Read:

0 RTPCLK is stopped between transmissions.

1 RTPCLK is free running.

Write in Privilege:

0 Stop RTPCLK between transmissions.

1 Configure RTPCLK as free running.

5 HOVF Halt on overflow. This bit indicates whether the CPU or DMA is halted while only one location in

the FIFO is empty in Trace Mode or Direct Data Mode (read).

Read:

0 Current data transfer to the FIFO will not be suspended in case of a full FIFO.

1 Current data transfer to the FIFO will be suspended in case of a full FIFO.

Write in Privilege:

0 The halt on FIFO overflow will be disabled. The data transfer will not be suspended and will be

discarded. Data written to the RTPDDMW register will overwrite the RTPDDMW register.

1 The halt on FIFO overflow will be enabled. Data written to the already full FIFO will be written

once the FIFO is emptied again. The data transfer to the FIFO will be suspended and signaled

to the CPU or other master while there is still data to be shifted out. When there is an empty

FIFO location again, the transfer of the data to the FIFO will be finished.

Loading...

Loading...