RTP Control Registers

www.ti.com

2164

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

RAM Trace Port (RTP)

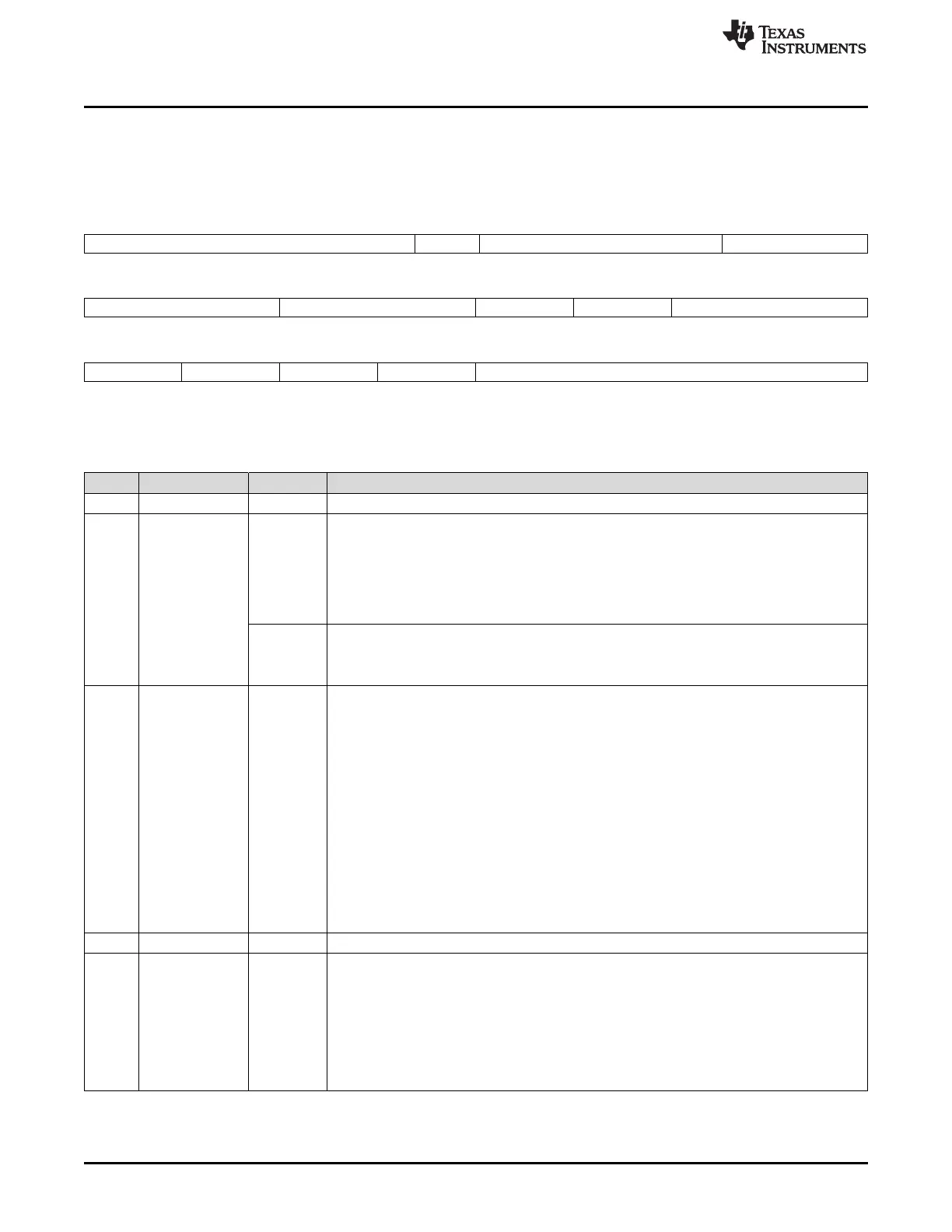

37.3.1 RTP Global Control Register (RTPGLBCTRL)

The configuration of the module can be changed with this register. Figure 37-9 and Table 37-8 describe

this register.

Figure 37-9. RTP Global Control Register (RTPGLBCTRL) (offset = 00h)

31 25 24 23 19 18 16

Reserved TEST Reserved PRESCALER

R-0 R/WP-0 R-0 R/WP-7h

15 14 13 12 11 10 9 8

Reserved DDM_WIDTH DDM_RW TM_DDM PW

R-0 R/WP-0 R/WP-0 R/WP-0 R/WP-0

7 6 5 4 3 0

RESET CONTCLK HOVF INV_RGN ON/OFF

R/WP-0 R/WP-0 R/WP-0 R/WP-0 R/WP-5h

LEGEND: R/W = Read/Write; R = Read only; WP = Write in privileged mode only; -n = value after reset

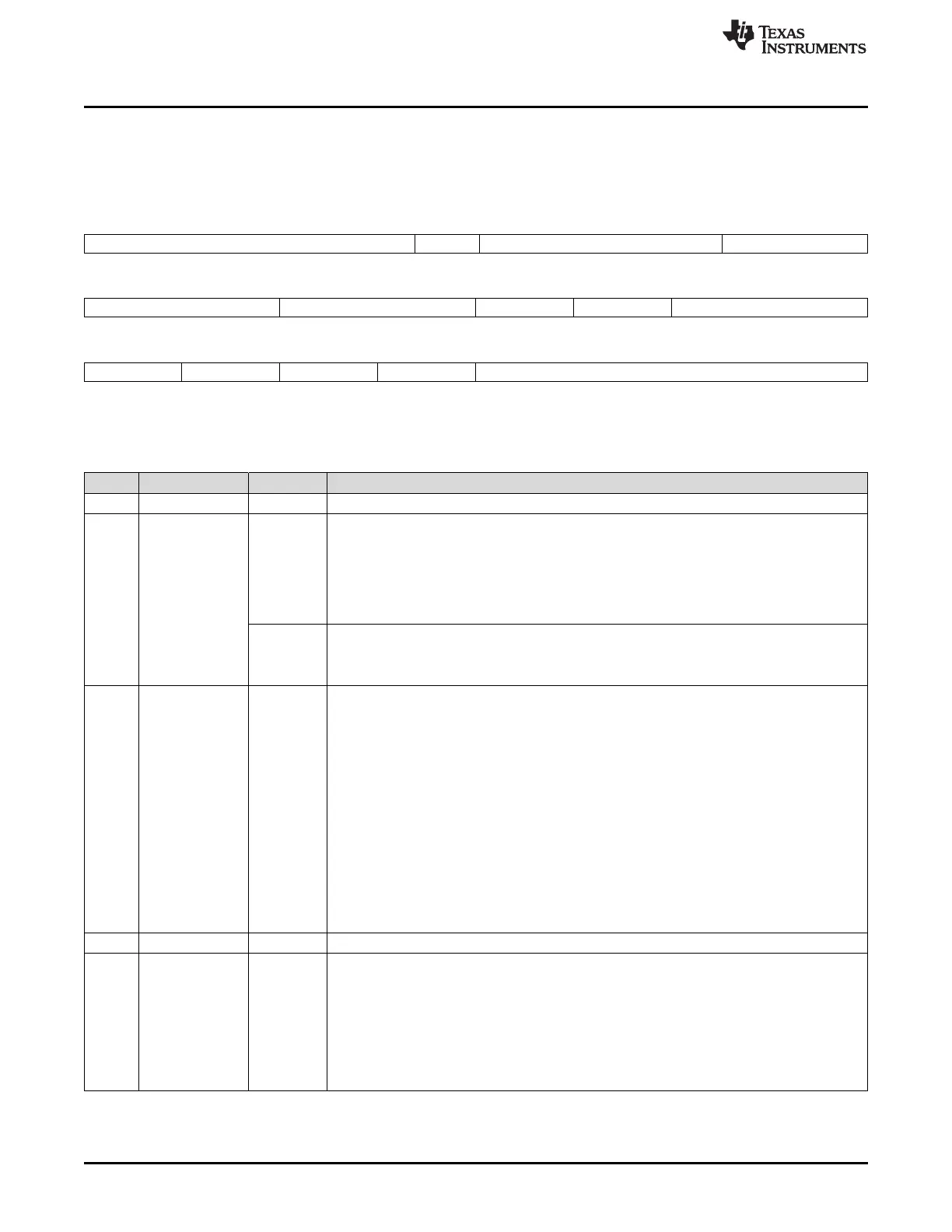

Table 37-8. RTP Global Control Register (RTPGLBCTRL) Field Descriptions

Bit Field Value Description

31-25 Reserved 0 Reads return 0. Writes have no effect.

24 TEST By setting the bit, the FIFO RAM will be mapped into the SYSTEM Peripheral frame starting at

address 0xFFF83000. Each FIFO starts at a 1-k boundary. Each FIFO entry is aligned to a 128-

bit boundary. See Table 37-9 for a listing of the FIFOs and their corresponding addresses.

Read:

0 FIFO RAM is not accessible in the memory-map.

1 FIFO RAM is mapped to address FFF8 3000h.

Write in Privilege:

0 Disables mapping of the FIFO RAM.

1 Enables mapping of the FIFO RAM into address FFF8 3000h.

18-16 PRESCALER The prescaler divides HCLK down to the desired RTPCLK frequency. The maximum RTPCLK

frequency specified in the device datasheet must not be exceeded. No dynamic change of

RTPCLK is supported. The module should be switched off by the ON/OFF bits in this register

before changing the prescaler.

User and privilege mode read, privilege mode write:

0 Prescaler is HCLK/1.

1h Prescaler is HCLK/2.

2h Prescaler is HCLK/3.

3h Prescaler is HCLK/4.

4h Prescaler is HCLK/5.

5h Prescaler is HCLK/6.

6h Prescaler is HCLK/7.

7h Prescaler is HCLK/8.

15-14 Reserved 0 Reads return 0. Writes have no effect.

13-12 DDM_WIDTH Direct data mode word size width. This bit field configures the number of bits that will be

transmitted in Direct Data Mode.

User and privilege mode read, privilege mode write:

0 Word size width is 8 bits.

1h Word size width is 16 bits.

2h Word size width is 32 bits.

3h Reserved

Loading...

Loading...