www.ti.com

STC2 (nHET) Test Coverage and Duration

445

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Self-Test Controller (STC) Module

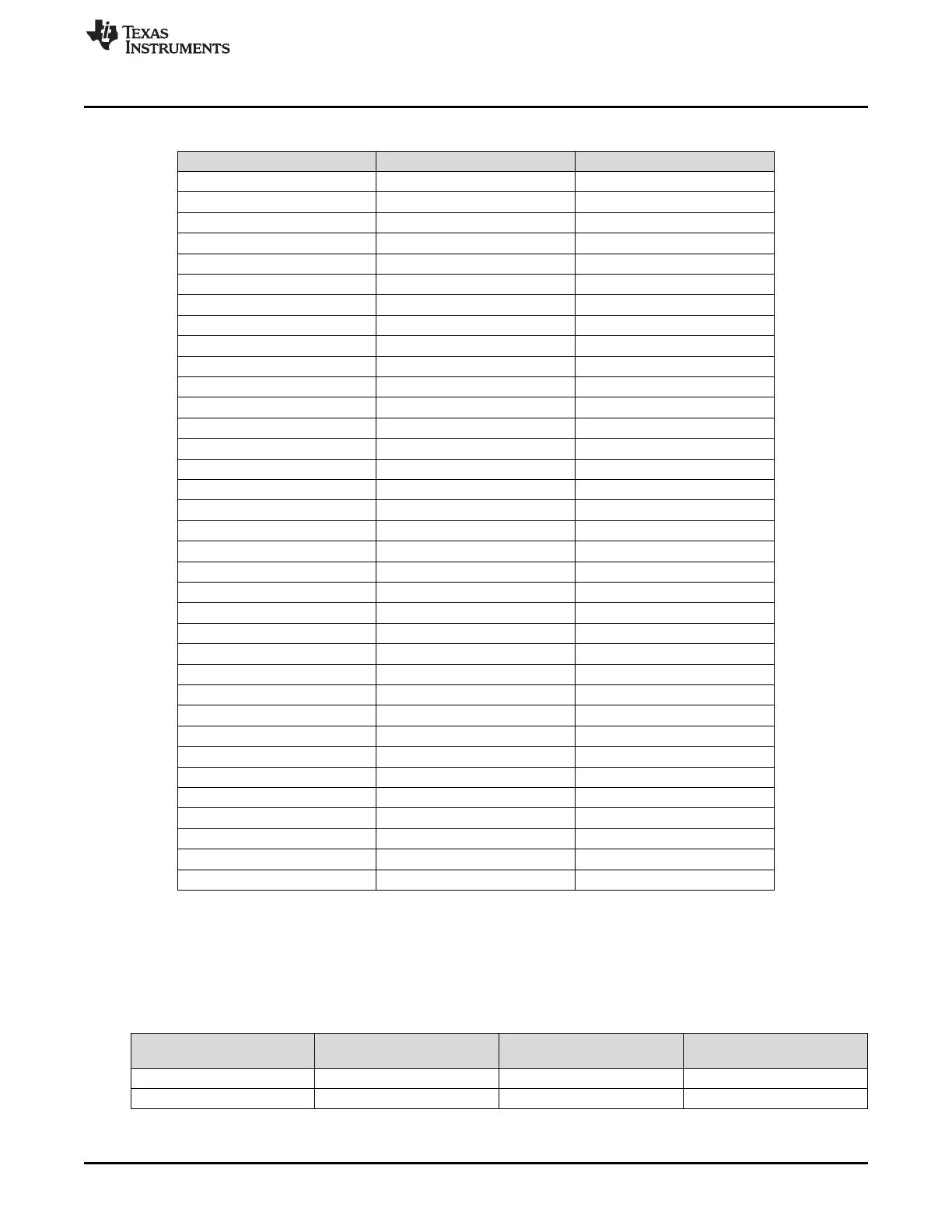

Table 10-6. STC2 Test Coverage and Duration (continued)

Intervals Test Coverage (%) Test Time (Cycles)

23 94.24 31395

24 94.38 32760

25 94.50 34125

26 94.72 35490

27 94.80 36855

28 94.90 38220

29 94.97 39585

30 95.03 40950

31 95.10 42315

32 95.16 43680

33 95.22 45045

34 95.27 46410

35 95.33 47775

36 95.42 49140

37 95.49 50505

38 95.54 51870

39 95.66 53235

40 95.69 54600

41 95.75 55965

42 95.79 57330

43 95.82 58695

44 95.85 60060

45 95.91 61425

46 95.95 62790

47 95.99 64155

48 96.01 65520

49 96.04 66885

50 96.07 68250

51 96.09 69615

52 96.12 70980

53 96.15 72345

54 96.19 73710

55 96.24 75075

56 96.29 76440

57 96.41 77805

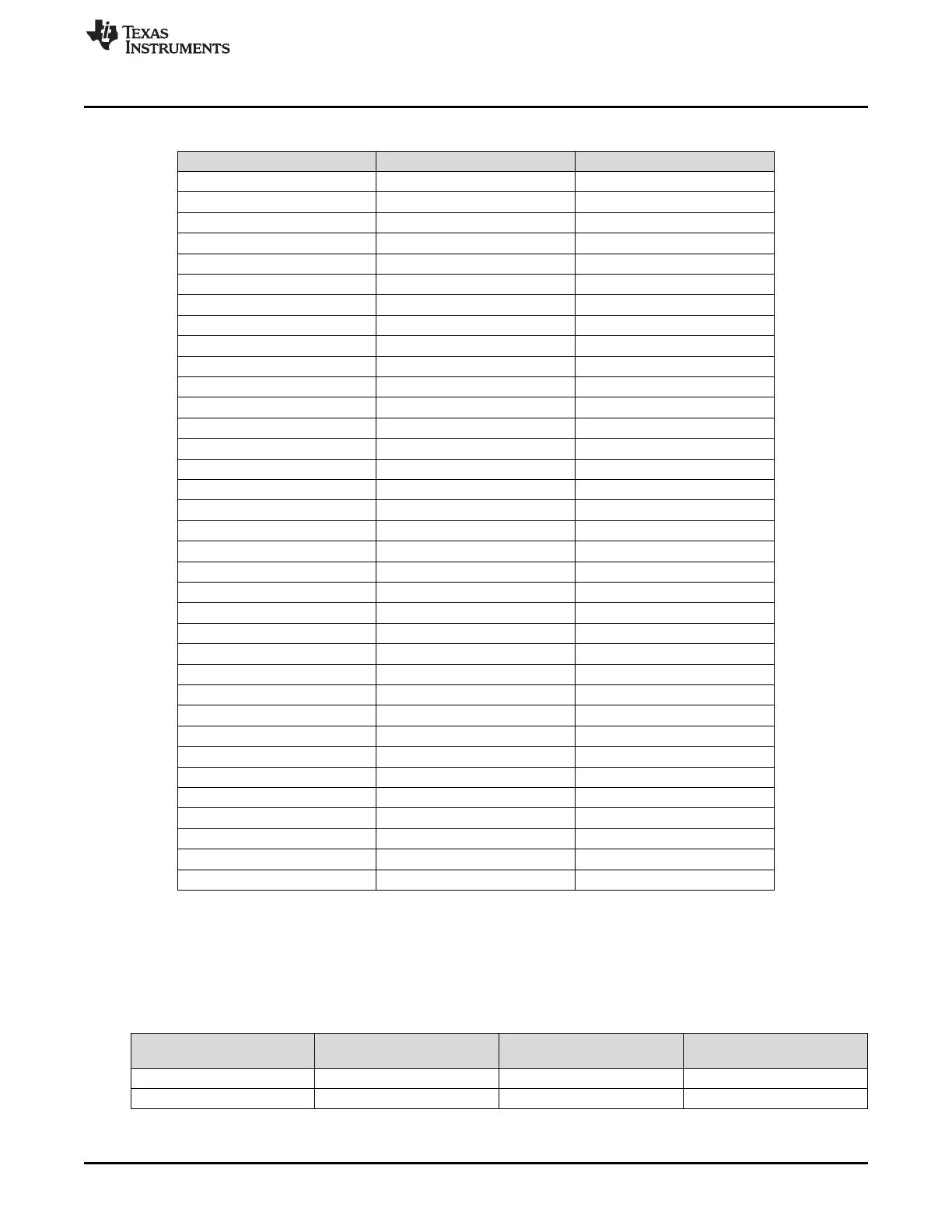

Table 10-7 gives the typical STC execution times for 9 intervals and 57 intervals at different clock rates.

You can choose the number of intervals to be run based on the coverage needed and allowed time for

STC execution.

Table 10-7. Typical Execution Times for STC2

Number of Intervals Coverage

@ VCLK = 110 MHz

STCCLK = 110 MHz

@ VCLK = 150 MHz

STCCLK = 75 MHz

9 >90% 111.68 µS 163.8 µS

57 >96% 707.3 µS 1.038 mS

Loading...

Loading...