Control Registers and Control Packets

www.ti.com

758

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Direct Memory Access Controller (DMA) Module

20.3.1.49 HBCB Interrupt Channel Offset Register (HBCBOFFSET)

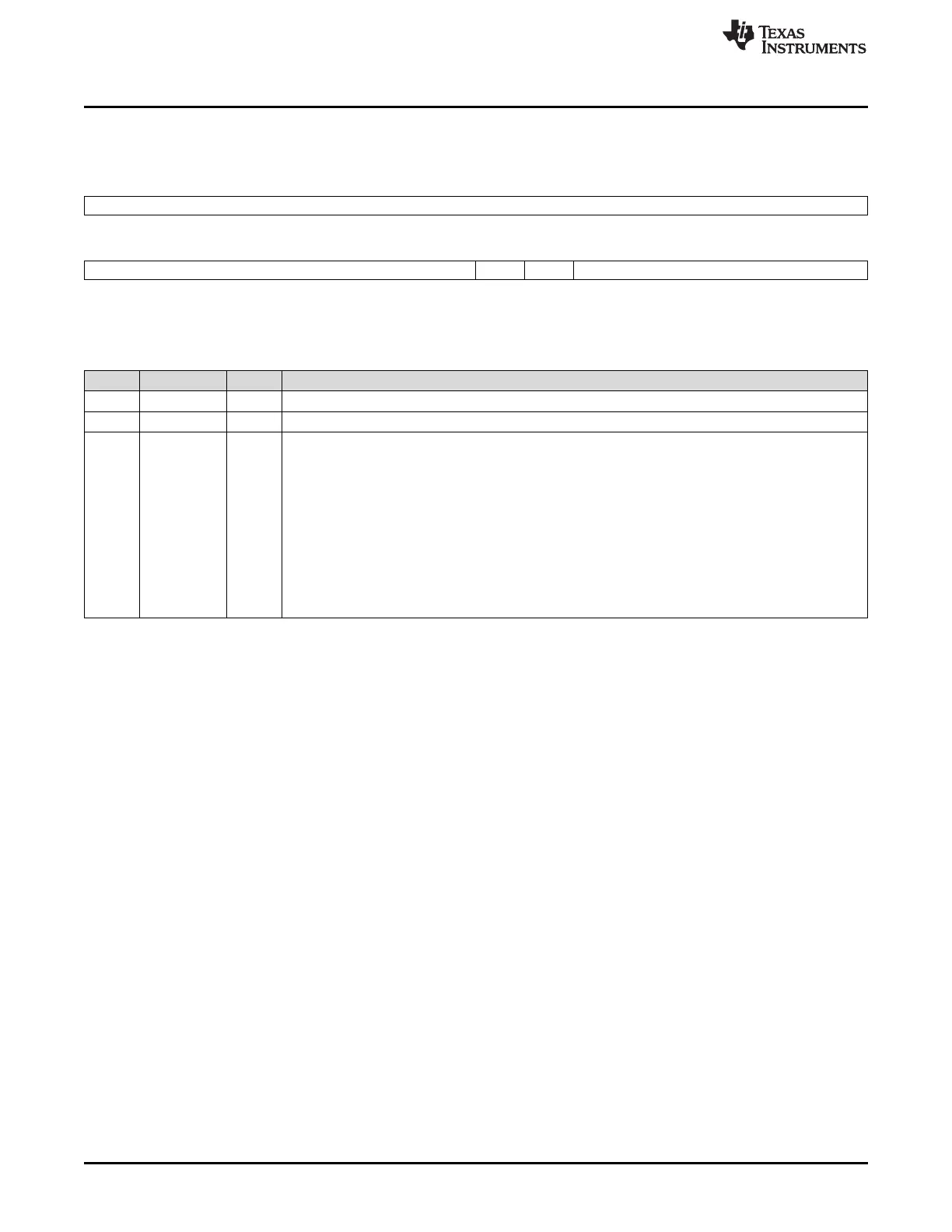

Figure 20-66. HBCB Interrupt Channel Offset Register (HBCBOFFSET) [offset = 168h]

31 16

Reserved

R-0

15 8 7 6 5 0

Reserved sbz sbz HBCB

R-0 R-0 R-0 R-0

LEGEND: R = Read only; -n = value after reset

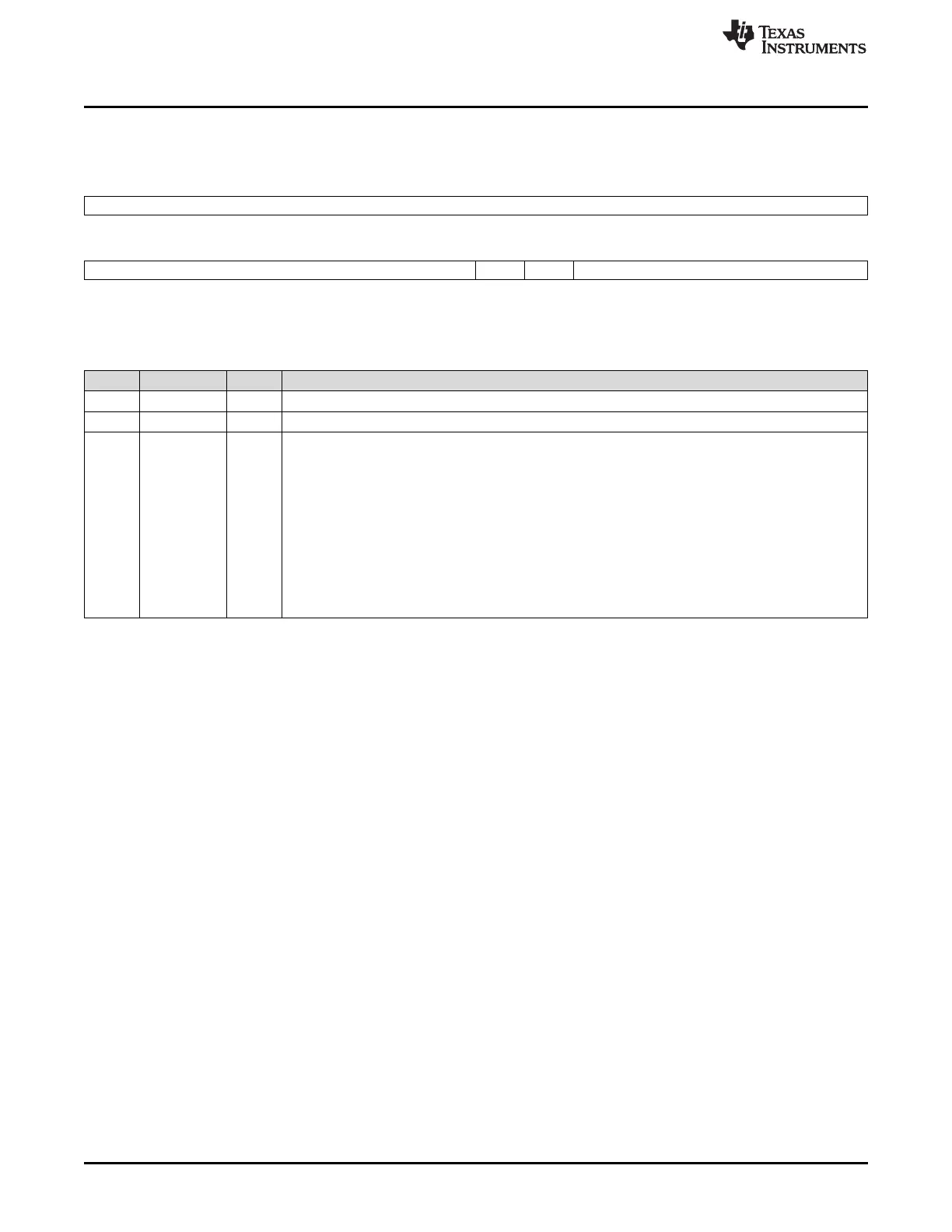

Table 20-56. HBCB Interrupt Channel Offset Register (HBCBOFFSET) Field Descriptions

Bit Field Value Description

31-16 Reserved 0 Reads return 0. Writes have no effect.

7-6 sbz 0 These bits should always be programmed as zero.

5-0 HBCB Channel causing HBC interrupt Group B. These bits contain the channel number of the pending

interrupt for Group B if the corresponding interrupt enable is set.

Note: Reading this location clears the corresponding interrupt pending flag (see

Section 20.3.1.40) with the highest priority.

0 No interrupt is pending.

1h Channel 0 is causing the pending interrupt Group B.

: :

20h Channel 31 is causing the pending interrupt Group B.

21h-

3Fh

Reserved

Loading...

Loading...