Control Registers and Control Packets

www.ti.com

760

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Direct Memory Access Controller (DMA) Module

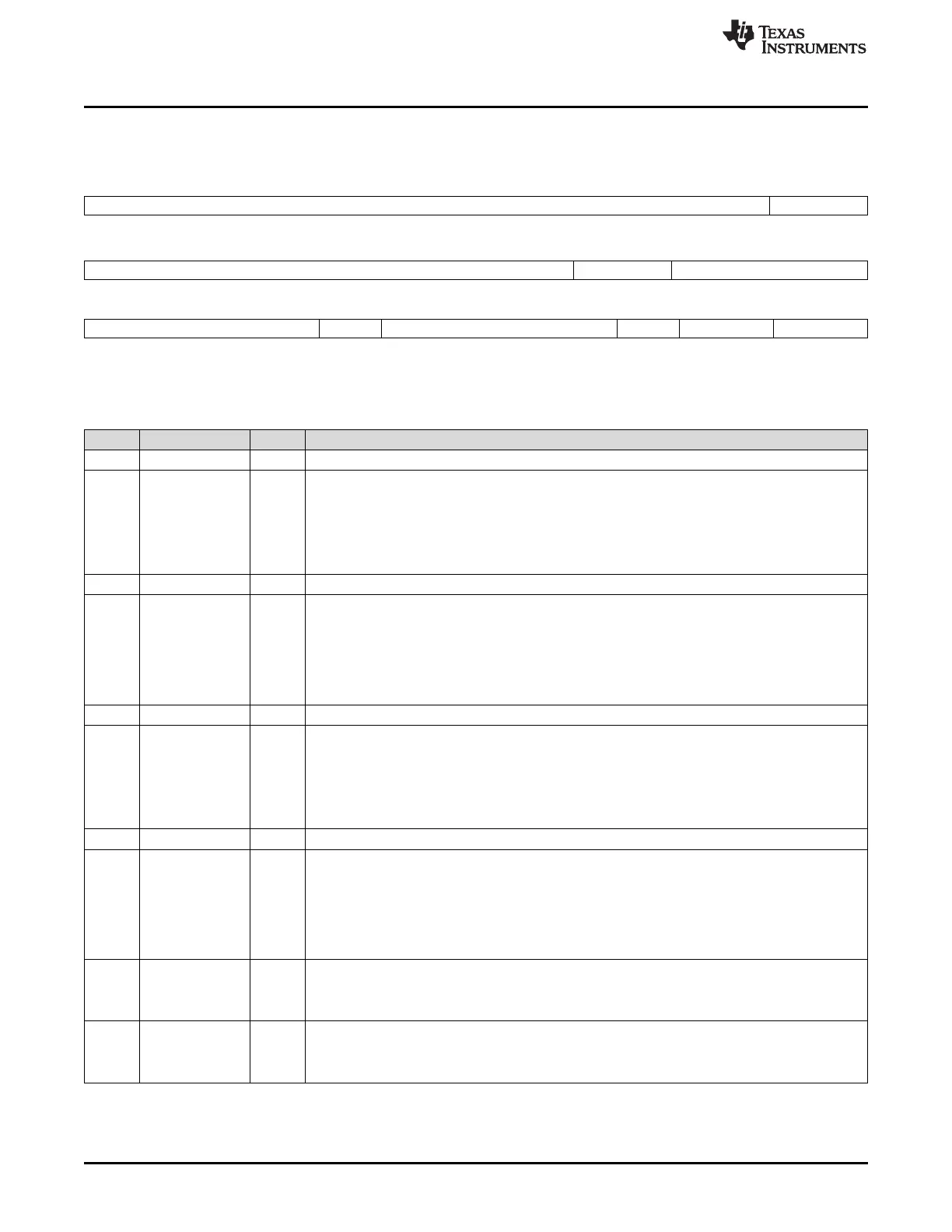

20.3.1.51 Port Control Register (PTCRL)

Figure 20-68. Port Control Register (PTCRL) [offset = 178h]

31 25 24

Reserved PENDB

R-0 R-0

23 19 18 17 16

Reserved BYB Reserved

R-0 R/WP-0 R-0

15 9 8 7 3 2 1 0

Reserved PENDA Reserved BYA PSFRHQ PSFRLQ

R-0 R-0 R-0 R/WP-0 R/WP-0 R/WP-0

LEGEND: R/W = Read/Write; R = Read only; WP = Write in privilege mode only; -n = value after reset

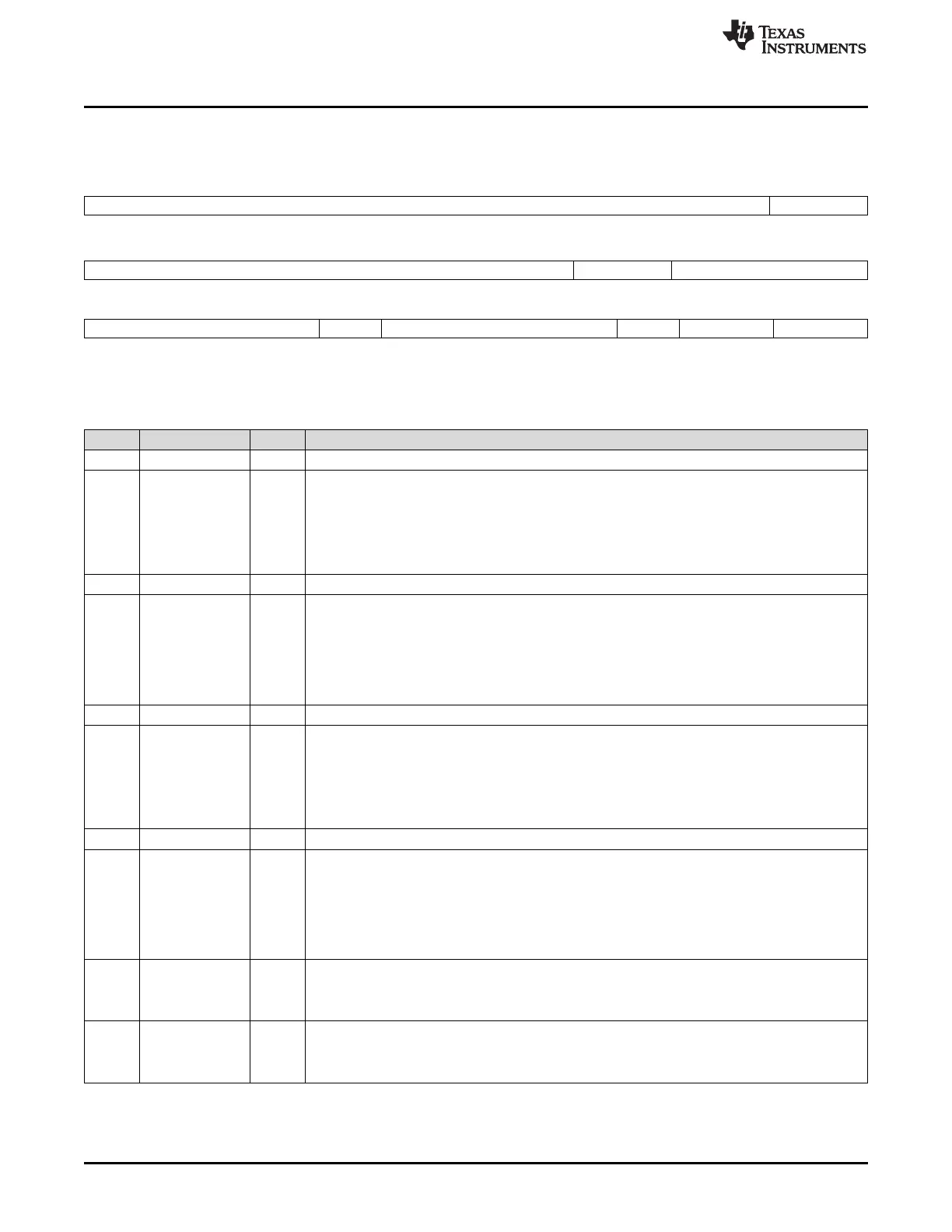

Table 20-58. Port Control Register (PTCRL) Field Descriptions

Bit Field Value Description

31-25 Reserved 0 Reads return 0. Writes have no effect.

24 PENDB Transfers pending for Port B. This flag determines if transfers are ongoing on port B. The flag will

be cleared if no transfers are performed. It can be used to determine if there is still data transferred

while DMA_EN is cleared to 0 in GCTCRL. In this case, once all transfers are finished, the flag will

be cleared to 0.

0 No transfers are pending.

1 Transfers are pending.

23-19 Reserved 0 Reads return 0. Writes have no effect.

18 BYB Bypass FIFO B.

0 FIFO B is not bypassed.

1 FIFO B is bypassed. Writing 1 to this bit limits the FIFO depth to the size of one element. That

means that after one element is read, the write-out to the destination will begin. This feature is

particularly useful to minimize switching latency between channels.

Note: This feature does not make optimal use of bus bandwidth.

17-9 Reserved 0 Reads return 0. Writes have no effect.

8 PENDA Transfers pending for Port A. This flag determines if transfers are ongoing on port A. The flag will

be cleared if no transfers are performed. It can be used to determine if there is still data transferred

while DMA_EN is cleared to 0 in GCTCRL. In this case, once all transfers are finished, the flag will

be cleared to 0.

0 No transfers are pending.

1 Transfers are pending.

7-3 Reserved 0 Reads return 0. Writes have no effect.

2 BYA Bypass FIFO A.

0 FIFO A is not bypassed.

1 FIFO A is bypassed. Writing 1 to this bit limits the FIFO depth to the size of one element. That

means that after one element is read, the write-out to the destination will begin. This feature is

particularly useful to minimize switching latency between channels.

Note: This feature does not make optimal use of bus bandwidth.

1 PSFRHQ Priority scheme fix or rotate for high priority queue.

0 Fixed priority is used.

1 Rotation priority is used.

0 PSFRLQ Priority scheme fix or rotate for low priority queue.

0 The fixed priority scheme is used.

1 The rotation priority scheme is used.

Loading...

Loading...