www.ti.com

Control Registers and Control Packets

787

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Direct Memory Access Controller (DMA) Module

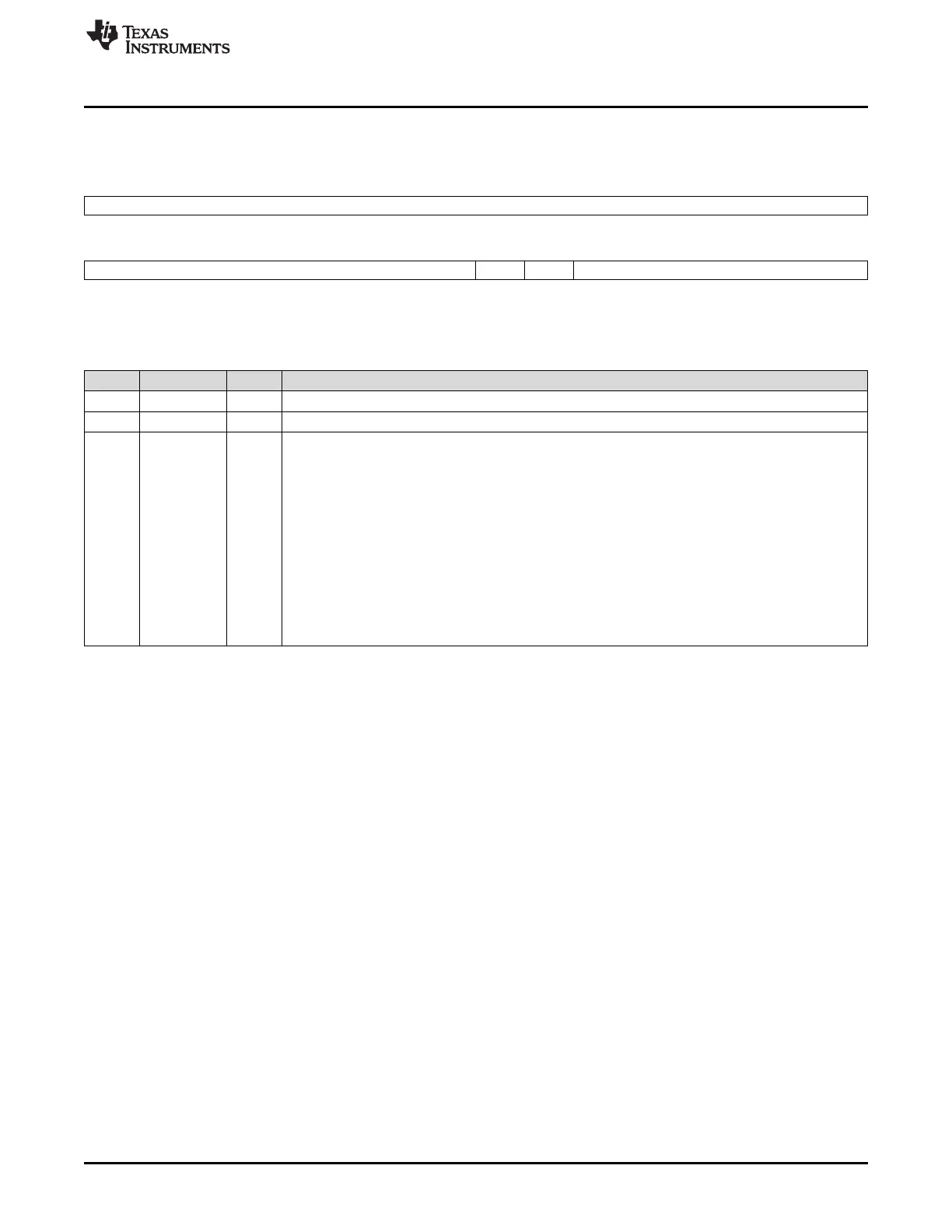

20.3.1.92 TER Event Channel Offset Register (TERROFFSET)

Figure 20-109. TER Event Channel Offset Register (TERROFFSET) [offset = 348h]

31 16

Reserved

R-0

15 8 7 6 5 0

Reserved sbz sbz TER_OFF

R-0 R-0 R-0 R-x

LEGEND: R = Read only; -n = value after reset

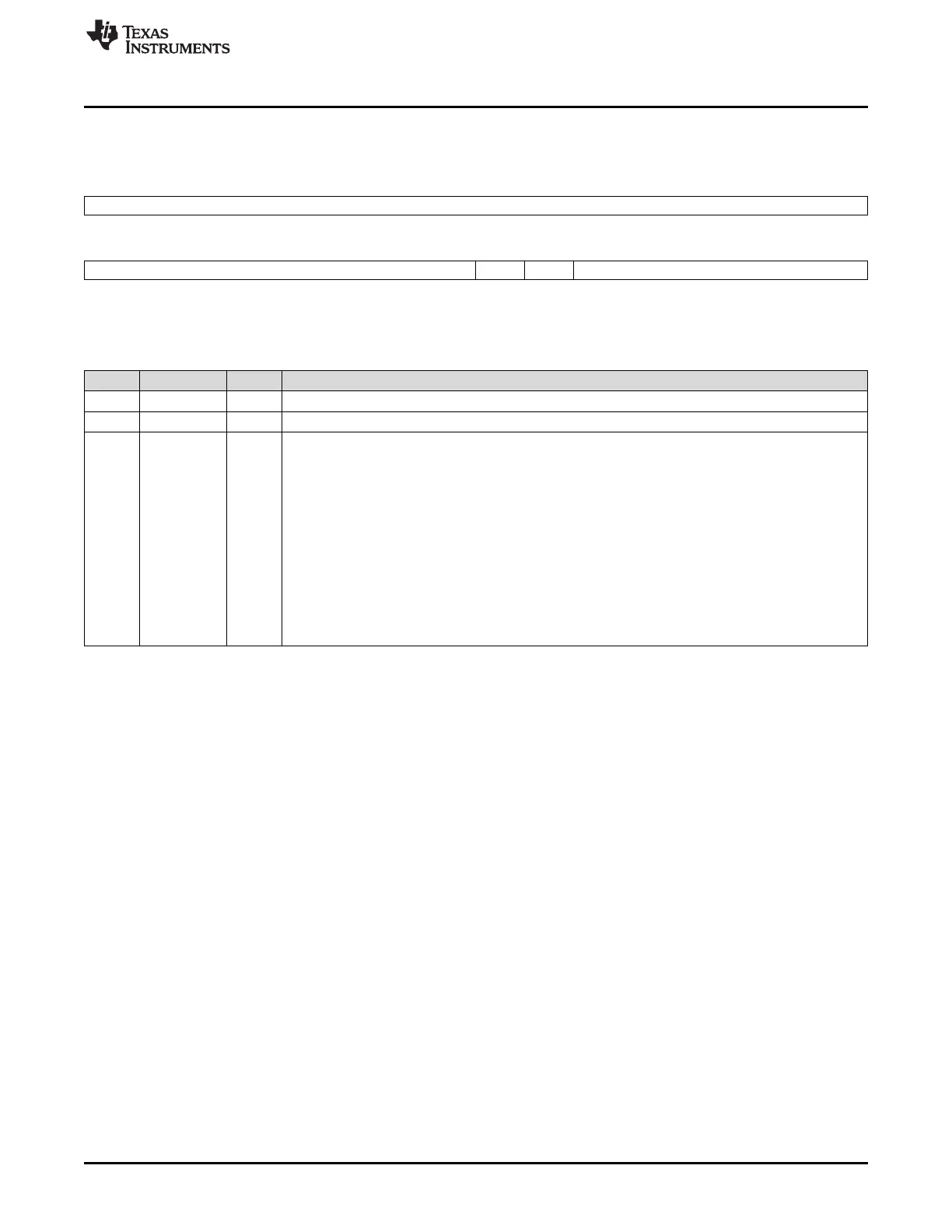

Table 20-99. TER Event Channel Offset Register (TERROFFSET) Field Descriptions

Bit Field Value Description

31-8 Reserved 0 Reads return 0. Writes have no effect.

7-6 sbz 0 These bits should always be programmed as zero.

5-0 TER_OFF This register provides the offset of the first channel number that encountered bus parity failure on either

port of DMA. Once this register is updated, it will not be changed by subsequent bus parity failures until

TER_ERR flag is cleared. Writes have no effect.

0 No interrupt is pending.

1h Channel 0 is causing the pending interrupt. (Read clears the register to 0 except when issued by a

debugger).

: :

20h Channel 31 is causing the pending interrupt.

21h-

3Fh

Reserved

Note: If both DMA ports encounter bus parity failure at the same time than lower channel number

(assuming higher priority) will be stored and the other one will be ignored.

Loading...

Loading...