www.ti.com

Control Registers and Control Packets

789

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Direct Memory Access Controller (DMA) Module

20.3.2.3 Initial Transfer Count Register (ITCOUNT)

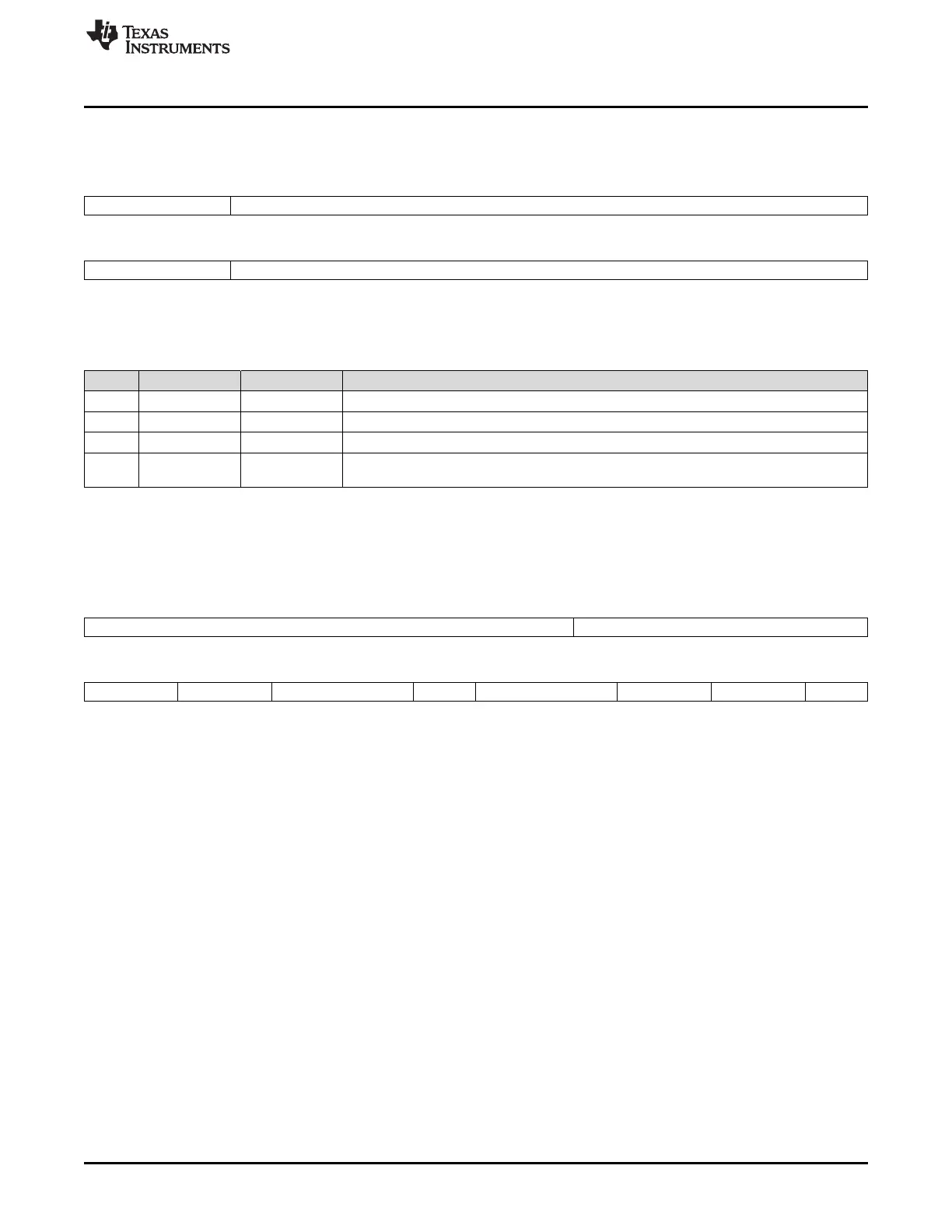

Figure 20-112. Initial Transfer Count Register (ITCOUNT) [offset = 08h]

31 29 28 16

Reserved IFTCOUNT

R-X R/WP-X

15 13 12 0

Reserved IETCOUNT

R-X R/WP-X

LEGEND: R/W = Read/Write; R = Read only; WP = Write in privilege mode only; X = value is unknown; -n = value after reset

Table 20-102. Initial Transfer Count Register (ITCOUNT) Field Descriptions

Bit Field Value Description

31-29 Reserved 0 Reads are undefined. Writes have no effect.

28-16 IFTCOUNT 0-1FFFh Initial frame transfer count. These bits define the number of frame transfers.

15-13 Reserved 0 Reads are undefined. Writes have no effect.

12-0 IETCOUNT 0-1FFFh Initial element transfer count. These bits define the number of element transfers. The block

transfer size will be IETCOUNT x IFTCOUNT.

20.3.2.4 Channel Control Register (CHCTRL)

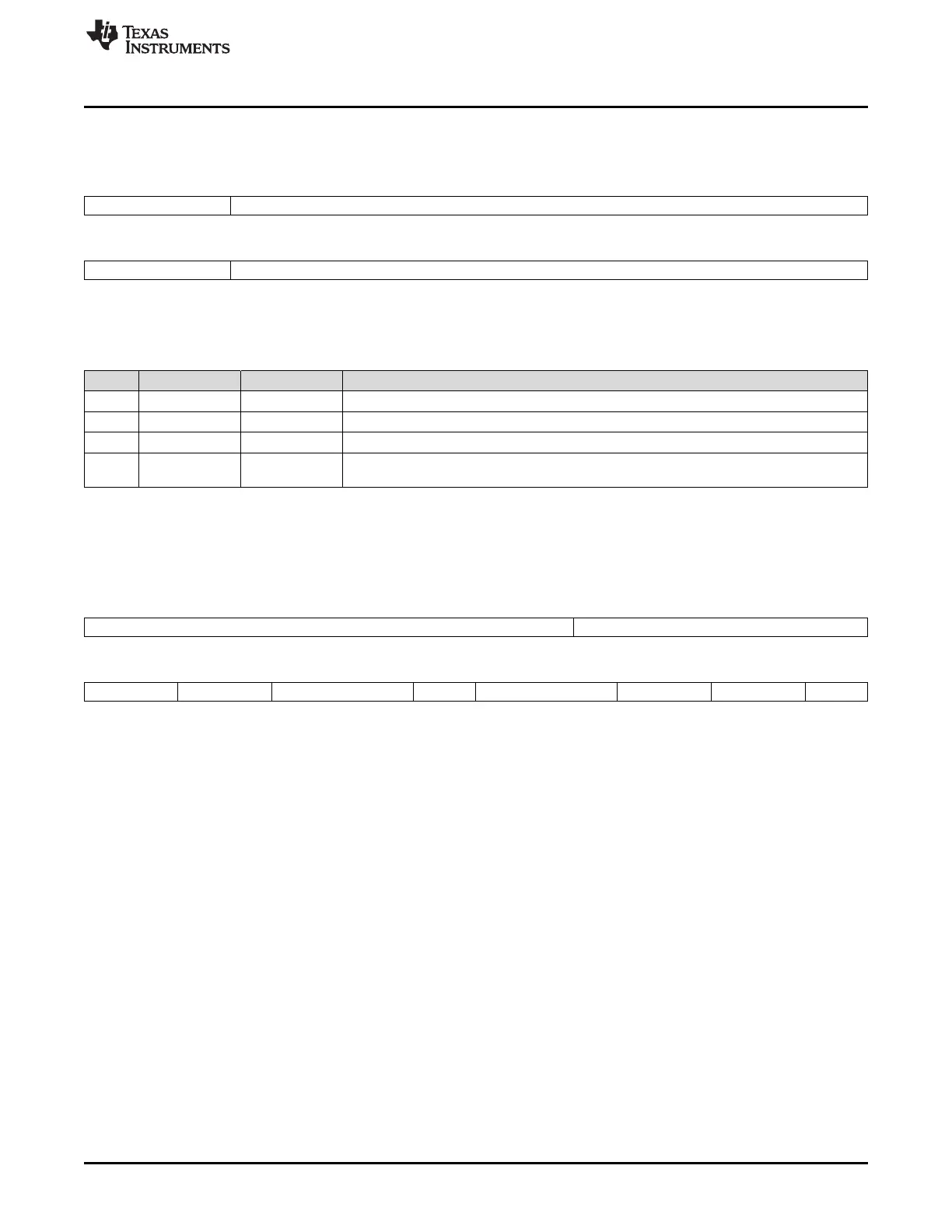

Figure 20-113. Channel Control Register (CHCTRL) [offset = 10h]

31 22 21 16

Reserved CHAIN

R-X R/WP-X

15 14 13 12 11 9 8 7 5 4 3 2 1 0

RES WES Reserved TTYPE Reserved ADDMR ADDMW AIM

R/WP-X R/WP-X R-X R/WP-X R-X R/WP-X R/WP-X R/WP-X

LEGEND: R/W = Read/Write; R = Read only; WP = Write in privilege mode only; X = value is unknown; -n = value after reset

Loading...

Loading...