Control Registers and Control Packets

www.ti.com

790

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Direct Memory Access Controller (DMA) Module

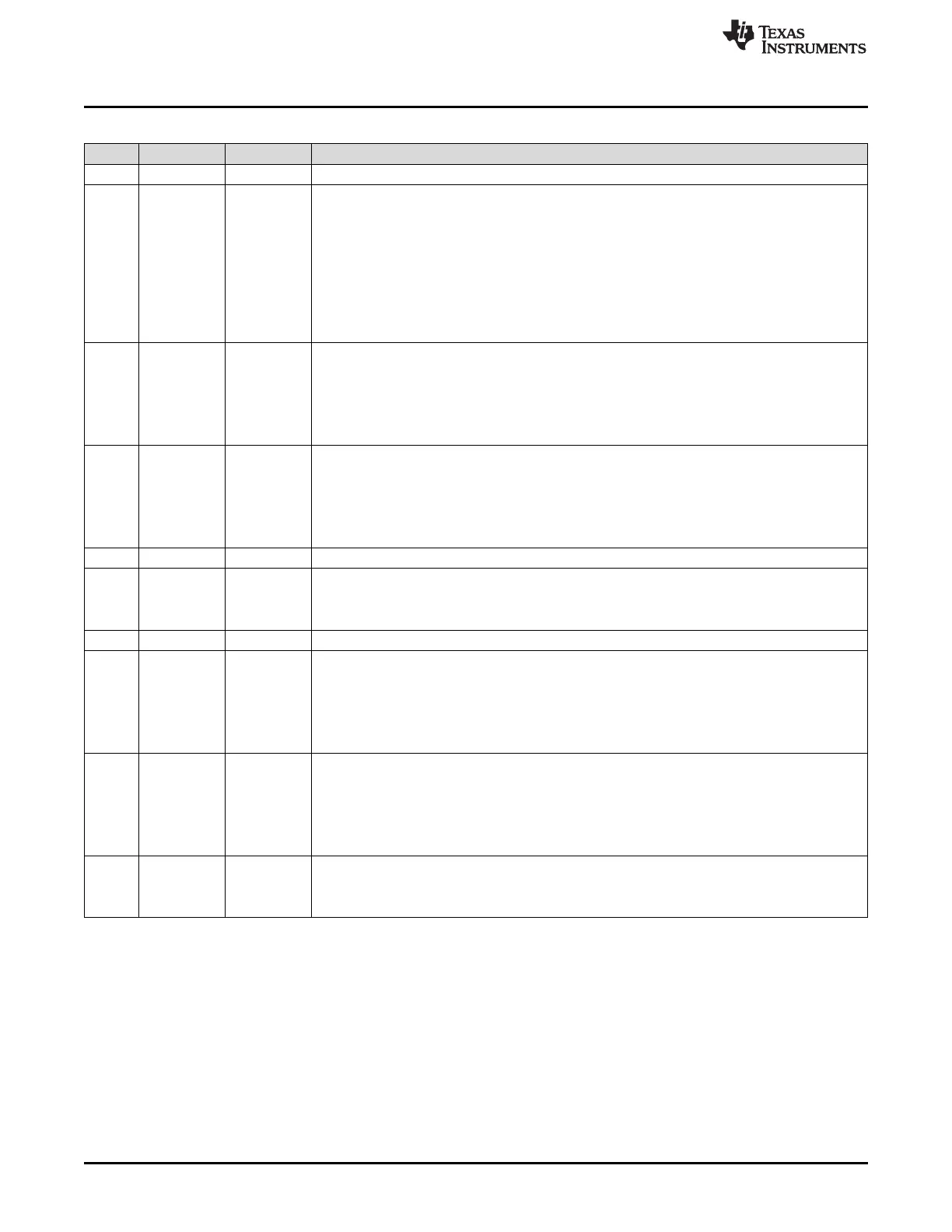

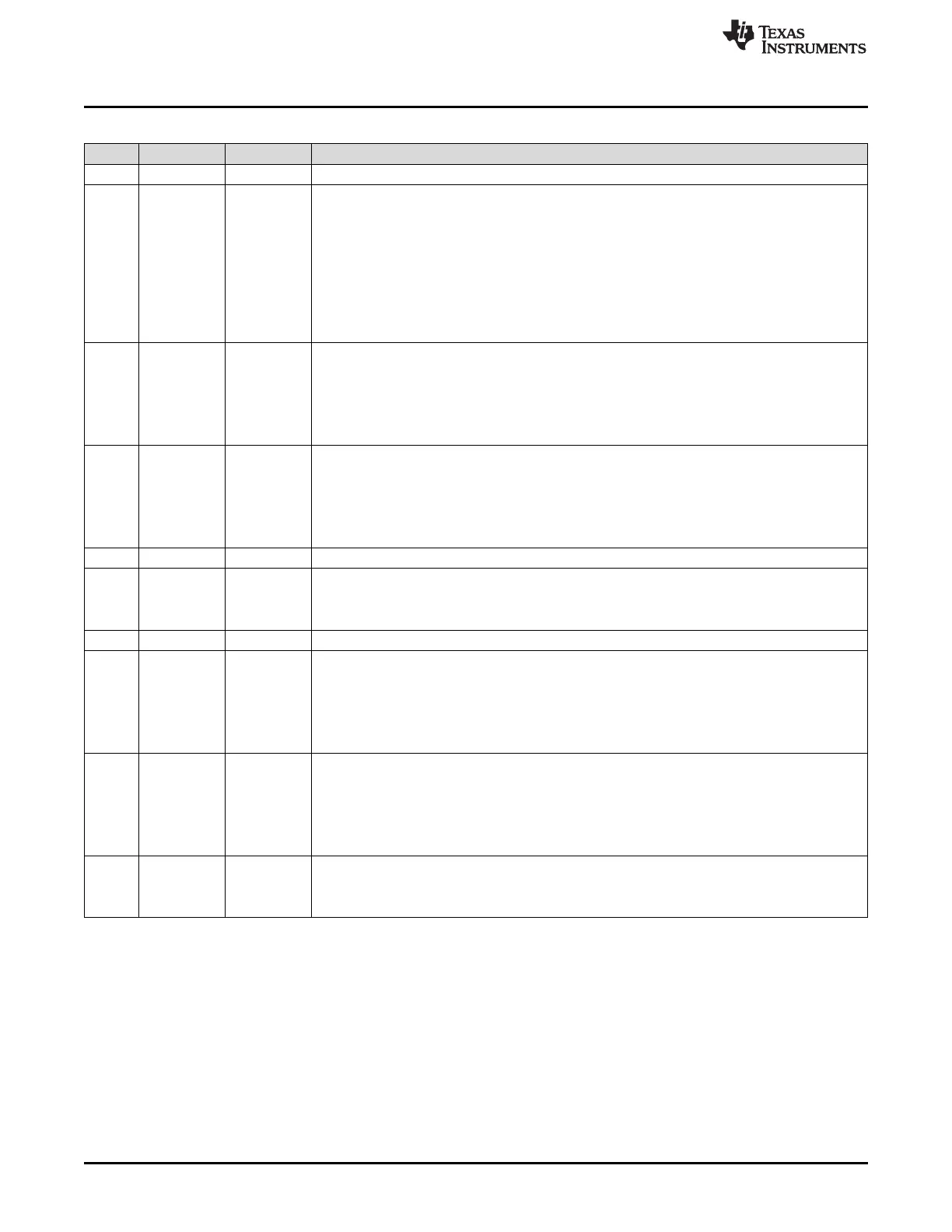

Table 20-103. Channel Control Register (CHCTRL) Field Descriptions

Bit Field Value Description

31-22 Reserved 0 Reads are undefined. Writes have no effect.

21-16 CHAIN Next channel to be triggered. At the end of the programmed number of frames, the specified

channel will be triggered.

Note: The programmer must program the CHAIN bits before initiating a DMA transfer.

0 No channel is selected.

1h Channel 0 is selected.

: :

20h Channel 31 is selected.

21h-3Fh Reserved

15-14 RES Read element size.

0 The element is byte, 8-bit.

1h The element is half-word, 16-bit.

2h The element is word, 32-bit.

3h The element is double-word, 64-bit.

13-12 WES Write element size.

0 The element is byte, 8-bit.

1h The element is half-word, 16-bit.

2h The element is word, 32-bit.

3h The element is double-word, 64-bit.

11-9 Reserved 0 Reads are undefined. Writes have no effect.

8 TTYPE Transfer type.

0 A request triggers one frame transfer.

1 A request triggers one block transfer.

7-5 Reserved 0 Reads are undefined. Writes have no effect.

4-3 ADDMR Addressing mode read.

0 Constant

1h Post-increment

2h Reserved

3h Indexed

2-1 ADDMW Addressing mode write.

0 Constant

1h Post-increment

2h Reserved

3h Indexed

0 AIM Auto-initiation mode.

0 Auto-initiation mode is disabled.

1 Auto-initiation mode is enabled.

Loading...

Loading...