www.ti.com

ADC Registers

883

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Analog To Digital Converter (ADC) Module

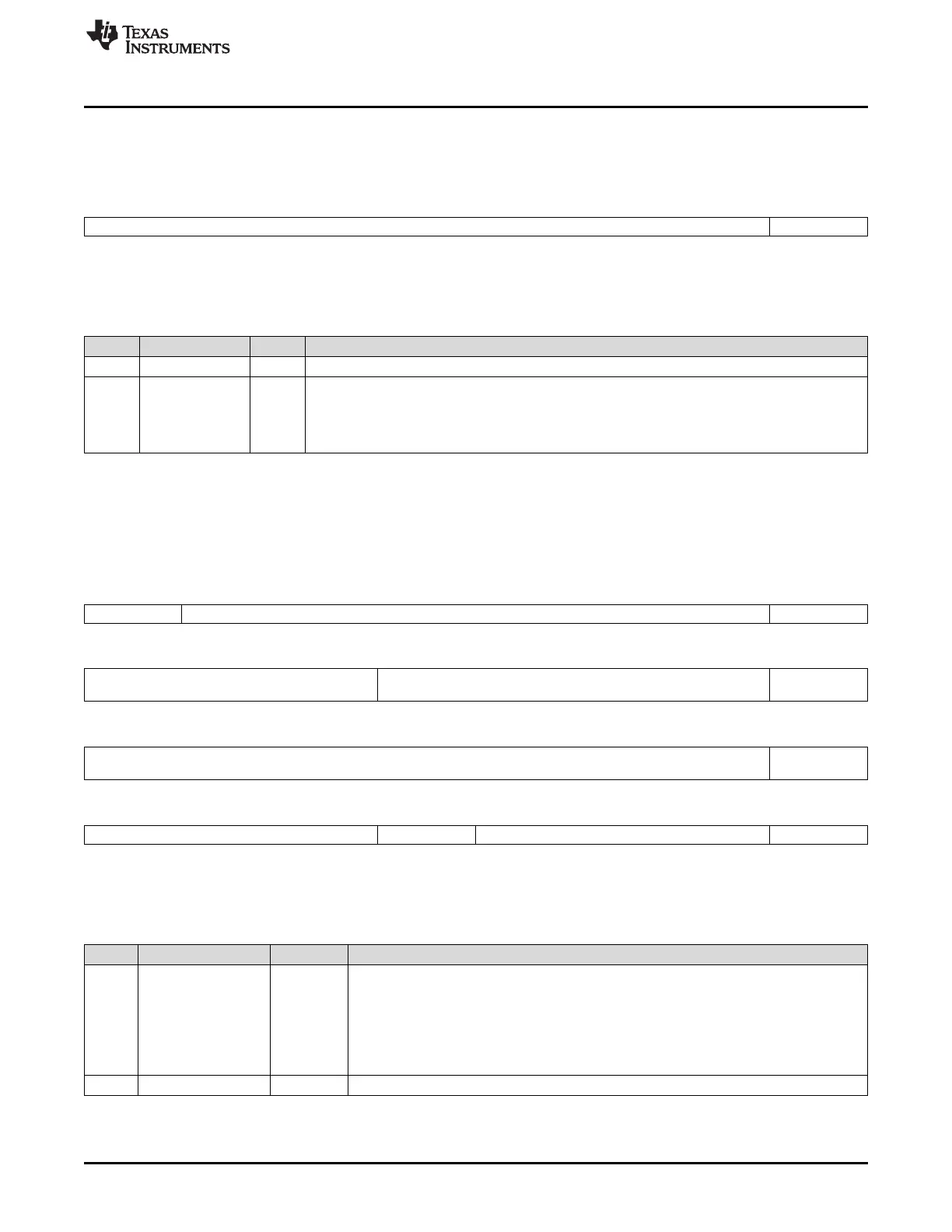

22.3.1 ADC Reset Control Register (ADRSTCR)

Figure 22-20 and Table 22-7 describe the ADRSTCR register.

Figure 22-20. ADC Reset Control Register (ADRSTCR) [offset = 00]

31 1 0

Reserved RESET

R-0 R/WP-0

LEGEND: R/W = Read/Write; R = Read only; WP = Write in privileged mode only; -n = value after reset

Table 22-7. ADC Reset Control Register (ADRSTCR) Field Descriptions

Bit Field Value Description

31-1 Reserved 0 Reads return 0. Writes have no effect.

0 RESET This bit is used to reset the ADC internal state machines and control/status registers. This reset

state is held until this bit is cleared. Read in all modes, write in privileged mode.

0 Module is released from the reset state.

1 All the module's internal state machines and the control/status registers are reset.

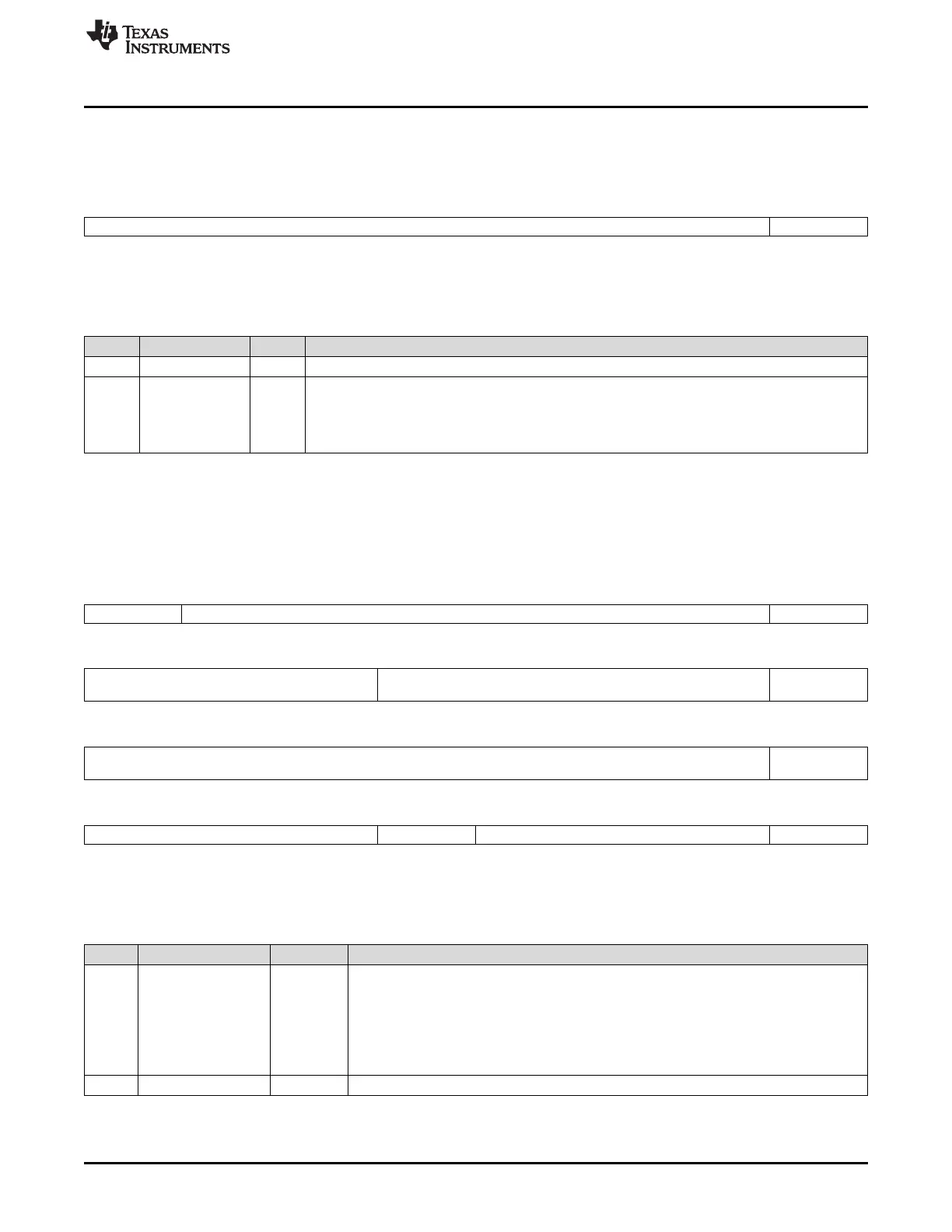

22.3.2 ADC Operating Mode Control Register (ADOPMODECR)

Figure 22-21 and Table 22-8 describe the ADOPMODECR register.

Figure 22-21. ADC Operating Mode Control Register (ADOPMODECR) [offset = 04]

31 30 25 24

10_12_BIT Reserved COS

R/W-0 R-0 R/W-0

23 21 20 17 16

Reserved CHN_TEST_EN RAM_TEST_

EN

R-0 R/W-Ah R/W-0

15 9 8

Reserved POWER

DOWN

R-0 R/W-0

7 5 4 3 1 0

Reserved IDLE_PWRDN Reserved ADC_EN

R-0 R/W-0 R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 22-8. ADC Operating Mode Control Register (ADOPMODECR) Field Descriptions

Bit Field Value Description

31 10_12_BIT This bit controls the resolution of the ADC core. It also affects the size of the conversion

results stored in the results’ RAM.

Any operation mode read/write:

0 The ADC core and digital logic are configured to be in 10-bit resolution. This is the default

mode of operation.

1 The ADC core and digital logic are configured to be in 12-bit resolution.

30-25 Reserved 0 Reads return 0. Writes have no effect.

Loading...

Loading...