www.ti.com

ADC Registers

907

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Analog To Digital Converter (ADC) Module

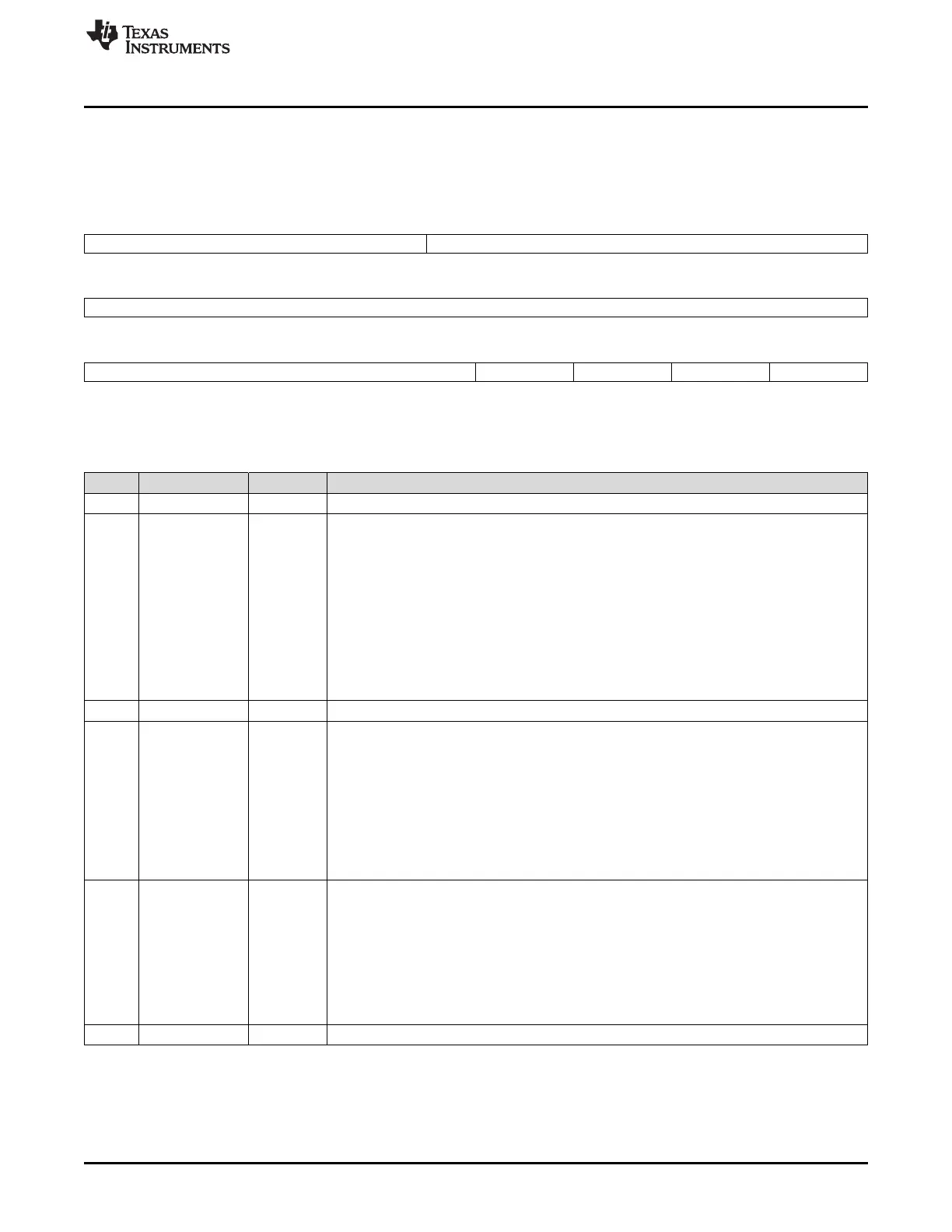

22.3.20 ADC Event Group DMA Control Register (ADEVDMACR)

ADC Event Group DMA Control Register (ADEVDMACR) is shown in Figure 22-42 and described in

Table 22-26.

Figure 22-42. ADC Event Group DMA Control Register (ADEVDMACR) [offset = 4Ch]

31 25 24 16

Reserved EV_BLOCKS

R-0 R/W-0

15 8

Reserved

R-0

7 4 3 2 1 0

Reserved DMA_EV_END EV_BLK_XFER Reserved EV_DMA_EN

R-0 R/W-0 R/W-0 R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

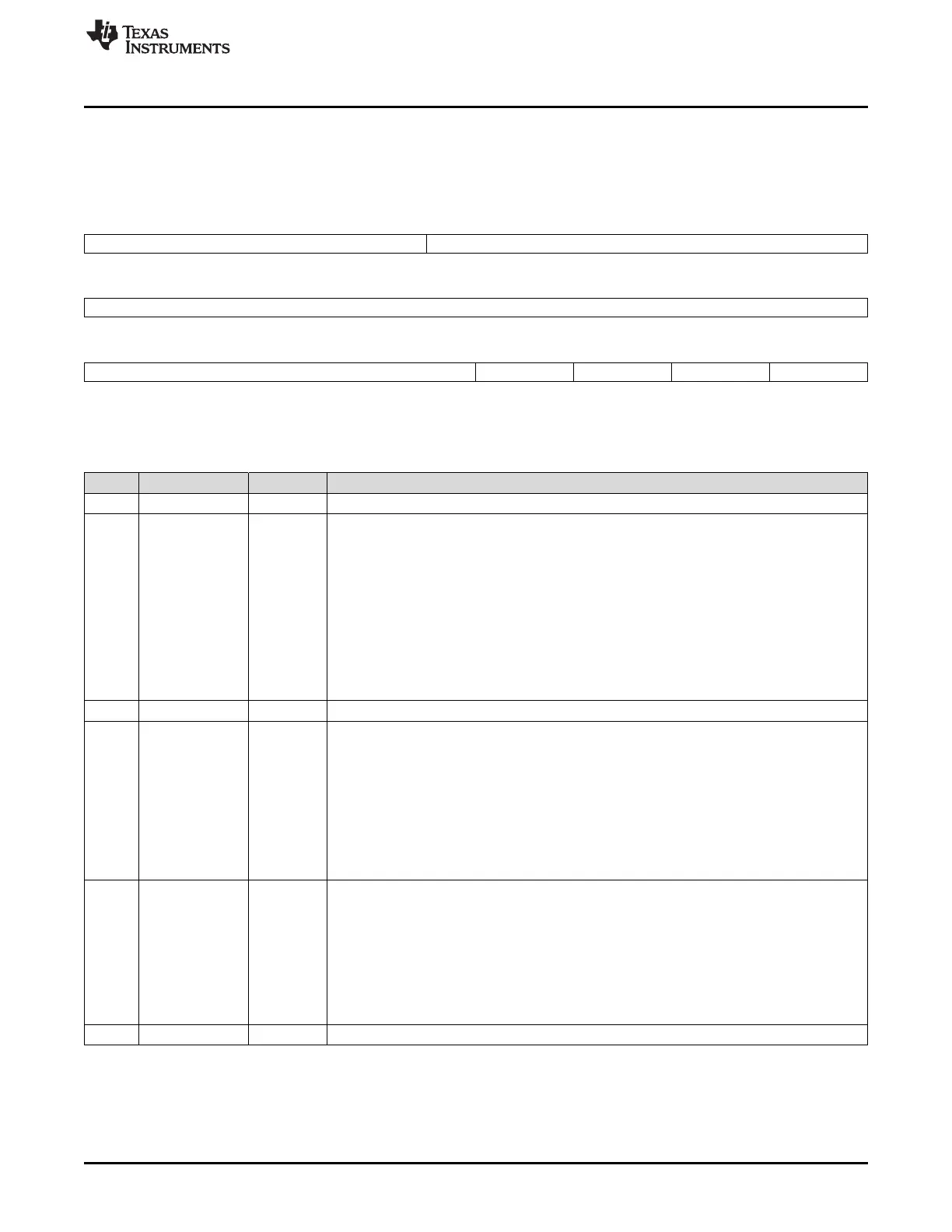

Table 22-26. ADC Event Group DMA Control Register (ADEVDMACR) Field Descriptions

Bit Field Value Description

31-25 Reserved 0 Reads return 0. Writes have no effect.

24-16 EV_BLOCKS Number of Event Group Result buffers to be transferred using DMA if the ADC module is

configured to generate a DMA request. If the Event Group is configured to use the block

transfer mode of the DMA module, then the ADC module generates a DMA request after the

Event Group results’ memory accumulates EV_BLOCKS number of conversion results.

This feature is designed to be used in place of the threshold interrupt for the Event Group. As a

result, the EV_THR field of the Event Group Interrupt Threshold Control Register and the

EV_BLOCKS field of the Event Group DMA Control Register are the same.

Any operation mode read/write:

0 No DMA transfer occurs even if EV_BLK_XFER is set to 1.

1h-1FFh One DMA request is generated if the EV_BLK_XFER is set to 1 and the specified number of

Event Group conversion results have been accumulated.

15-4 Reserved 0 Reads return 0. Writes have no effect.

3 DMA_EV_END Event Group Conversion End DMA Transfer Enable.

Any operation mode read:

0 ADC module generates a DMA request for each write to the Event group results RAM if

EV_DMA_EN is set.

1 ADC module generates a DMA request when the ADC has completed the conversions for all

channels selected for conversion in the event group.

If DMA_EV_END bit is set to 1, EV_DMA_EN bit is ignored and DMA requests will be

generated every time the DMA_EV_END flag in the event group status register is set. The

DMA_EV_END bit must be set before enabling conversions for the event group.

2 EV_BLK_XFER Event Group Block DMA Transfer Enable.

Any operation mode read:

0 ADC module generates a DMA request for each write to the Event Group memory if

EV_DMA_EN is set.

1 ADC module generates a DMA request when the ADC has written EV_BLOCKS number of

buffers into the Event Group memory.

If EV_BLK_XFER bit is set to 1, EV_DMA_EN bit is ignored and DMA requests will be

generated every time the Threshold Counter reaches 0 from a count value of 1.

1 Reserved 0 Reads return 0. Writes have no effect.

Loading...

Loading...