Buffer Addr

TSO

TBA NTBA

=

+

communication

cycle start

www.ti.com

Module Operation

1223

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

FlexRay Module

26.2.1.1.1.9 Transfer Data Package

Table 26-4 shows the data of a transfer data package. Independent of whether the header gets

transferred or not, the buffer address always points to element Header1.

(1)

Transferred only from Communication Controller to System Memory

Table 26-4. Mirroring Address Mapping

Address Register

0x0000 Header1

0x0004 Header2

0x0008 Header3

0x000C Buffer Status

(1)

0x0010 Payload1

0x0014 Payload2

: :

0x010C Payload64

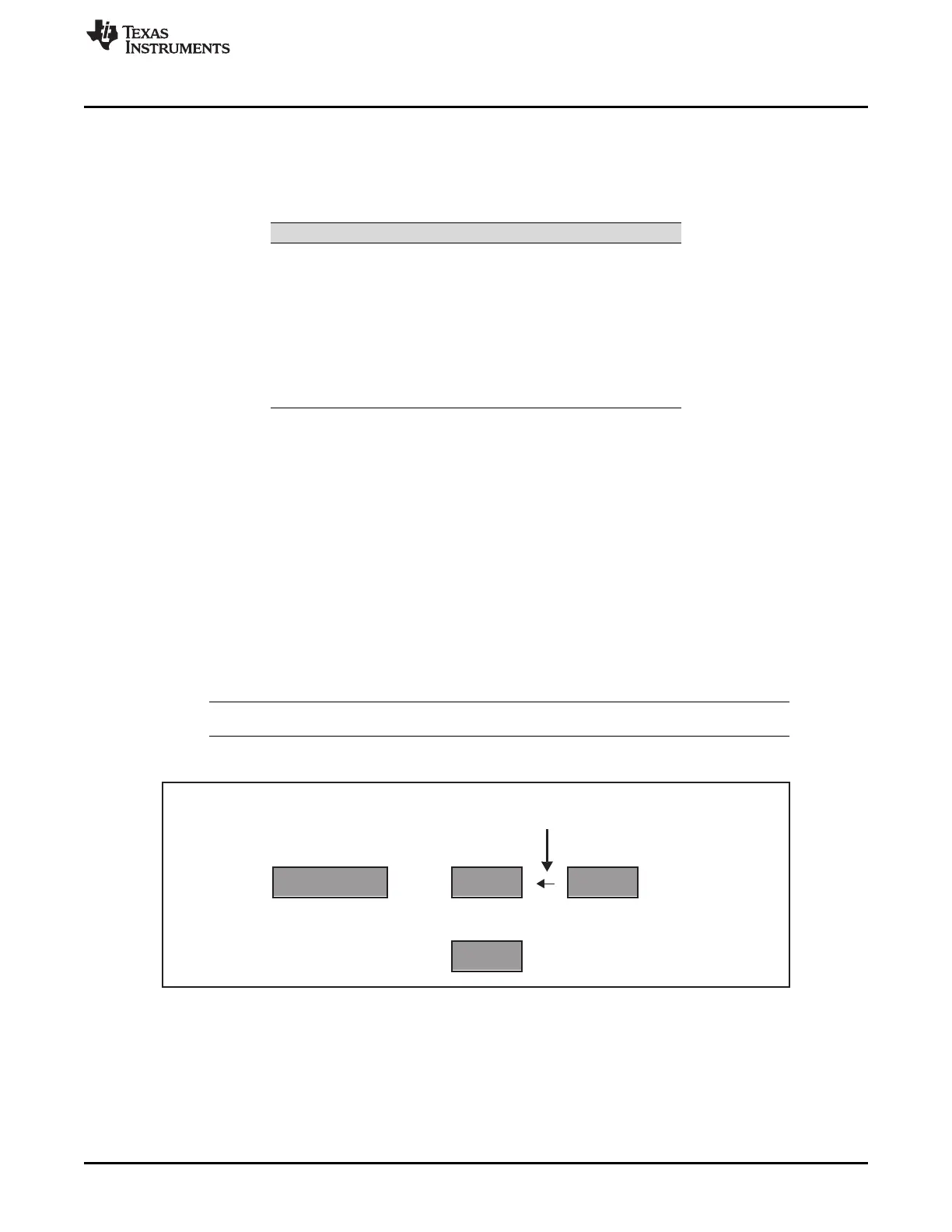

26.2.1.1.1.10 Transfer Start Address to Message Buffer Number Assignment

The assignment of a FlexRay message buffer number to the transfer location in system memory is done

by the combination of:

• the Transfer Start Offset (TSO) field in a Transfer Configuration RAM (TCR) entry

• the Transfer Base Address (TBA) register

Each entry of the TCR holds a 14 bit offset value (TSO). The TSO offset will be added to the content of

the TBA register. The TBA register holds the 32bit base address-pointer to a location of the data RAM.

A value written to Next Transfer Base Address (NTBA) will be loaded in the TBA at the next

communication cycle start. This allows efficient multi-buffering of the message buffers in the system

memory. The Transfer Not Ready (NTR) flag in the Transfer Error Interrupt Flag (TEIF) register can be

used to determine, if NTBA can be reloaded by the CPU.

NOTE: If a value is written to TBA, NTBA is set to the same value.

Figure 26-9. Transfer Start Address to Message Buffer Number Assignment

26.2.1.1.1.11 Transfer Priority

The Transfer Unit will transfer the message buffers from low to high message buffer numbers.

In case the same buffer is pending in both the Trigger Transfer to Communication (TTCC) register and the

Trigger Transfer to System Memory (TTSM) register, the priority between TTCC and TTSM is determined

by the Transfer Priority bit (GC.PRIO) in the Transfer Unit Global Control Set/Reset Register (GCS/R).

Loading...

Loading...