FlexRay Module Registers

www.ti.com

1300

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

FlexRay Module

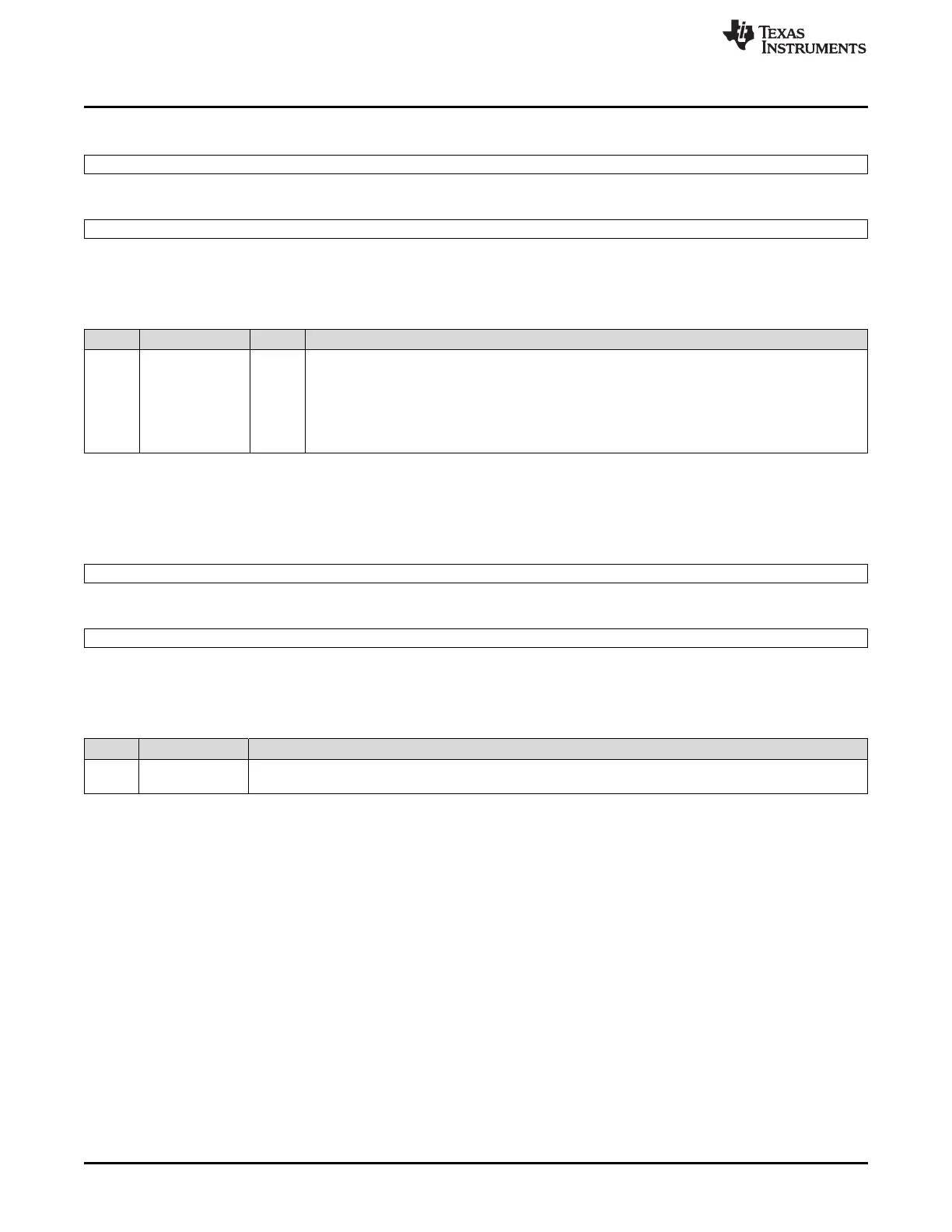

Figure 26-60. Trigger Transfer to System Memory Set 2 (TTSMS2) [offset_TU = 88h]

31 16

TTSMS2[63-48]

R/WS-0

15 0

TTSMS2[47-32]

R/WS-0

LEGEND: R/W = Read/Write; R = Read only; S = Set; -n = value after reset

Table 26-40. Trigger Transfer to System Memory Set 2 (TTSMS2) Field Descriptions

Bit Field Value Description

31-0 TTSMS2[n] Trigger Transfer to System Memory Set 2. The register bits 0 to 31 correspond to message buffers

32 to 63. Each bit of the register controls the message buffer transfer to the system memory in the

following manner (note that only the least-significant bit of all four combined TTSM registers will be

currently scheduled for transmission).

0 No transfer request.

1 Transfer based on address defined in TBA

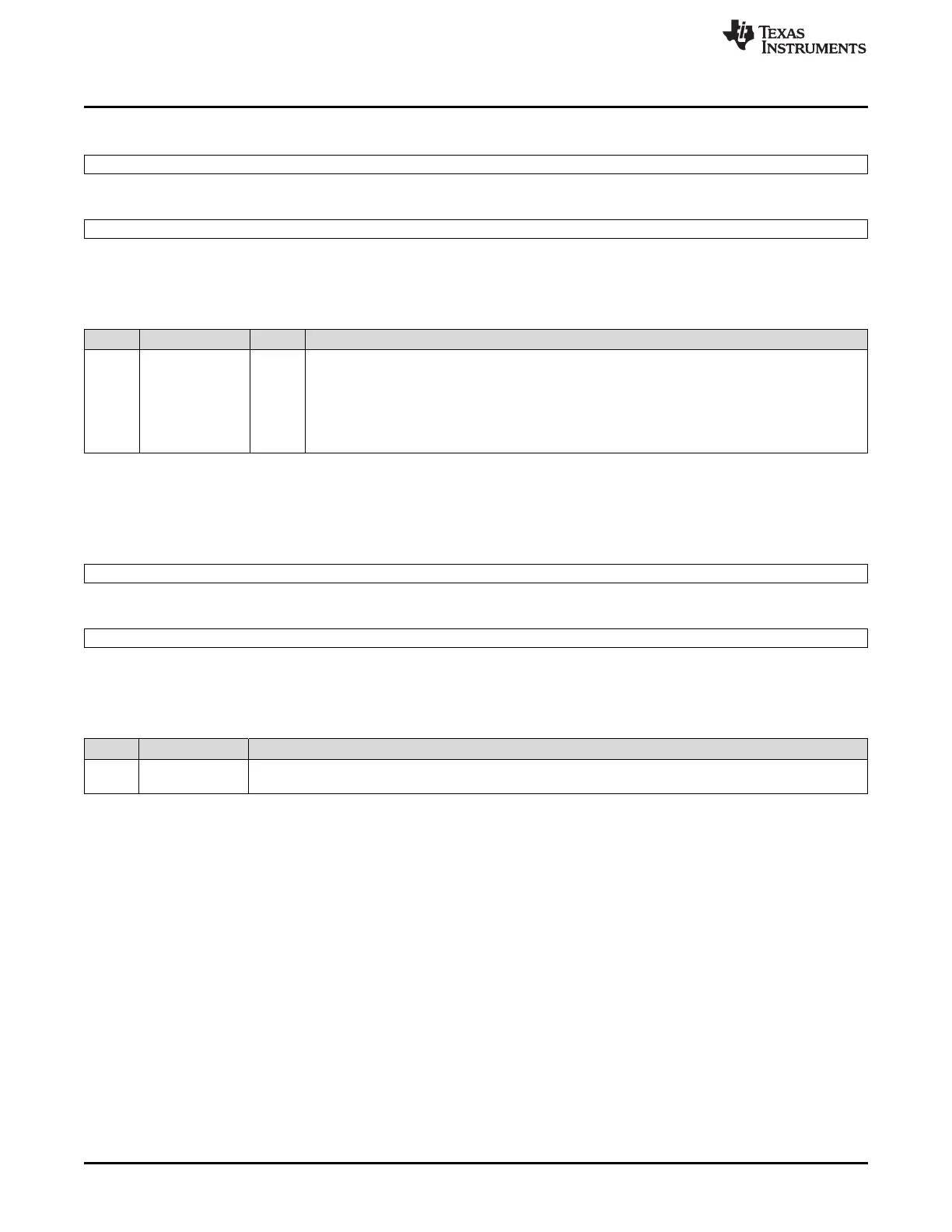

Figure 26-61. Trigger Transfer to System Memory Reset 2 (TTSMR2) [offset_TU = 8Ch]

31 16

TTSMR2

R/WC-0

15 0

TTSMR2

R/WC-0

LEGEND: R/W = Read/Write; R = Read only; C = Clear; -n = value after reset

Table 26-41. Trigger Transfer to System Memory Reset 2 (TTSMR2) Field Descriptions

Bit Field Description

31-0 TTSMR2 Trigger Transfer to System Memory Reset 2. The TTSMR2 register shows the identical values to TTSMS2 if

read.

Loading...

Loading...