FlexRay Module Registers

www.ti.com

1334

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

FlexRay Module

26.3.2.1.5 Test Register 1 (TEST1)

Test register 1 holds the control bits to configure the test modes of the FlexRay module. Write access to

these bits is only possible if the WRTEN bit is set. Figure 26-113 and Table 26-93 illustrate this register.

When the FlexRay module is operated in one of its test modes that requires WRTEN to be set (RAM Test

Mode, I/O Test Mode, Asynchronous Transmit Mode, and Loop Back Mode) only the selected test mode

functionality is available.

NOTE: To return from test mode operation to regular FlexRay operation we strongly recommend to

apply a hardware reset (Power on Reset or nReset) to reset all FlexRay internal state

machines to their initial state.

The test functions are not available in addition to the normal operational mode functions, they change the

functions of parts of the FlexRay module. Therefore, normal operation as specified outside this chapter

and as required by the FlexRay protocol specification and the FlexRay conformance test is not possible.

Test mode functions may not be combined with each other or with FlexRay protocol functions.

NOTE: The FlexRay module should be kept in CONFIG state, while RAM Test Mode TMC = 01 is

enabled.

The test mode features are intended for hardware testing or for FlexRay bus analyzer tools. They are not

intended to be used in FlexRay applications.

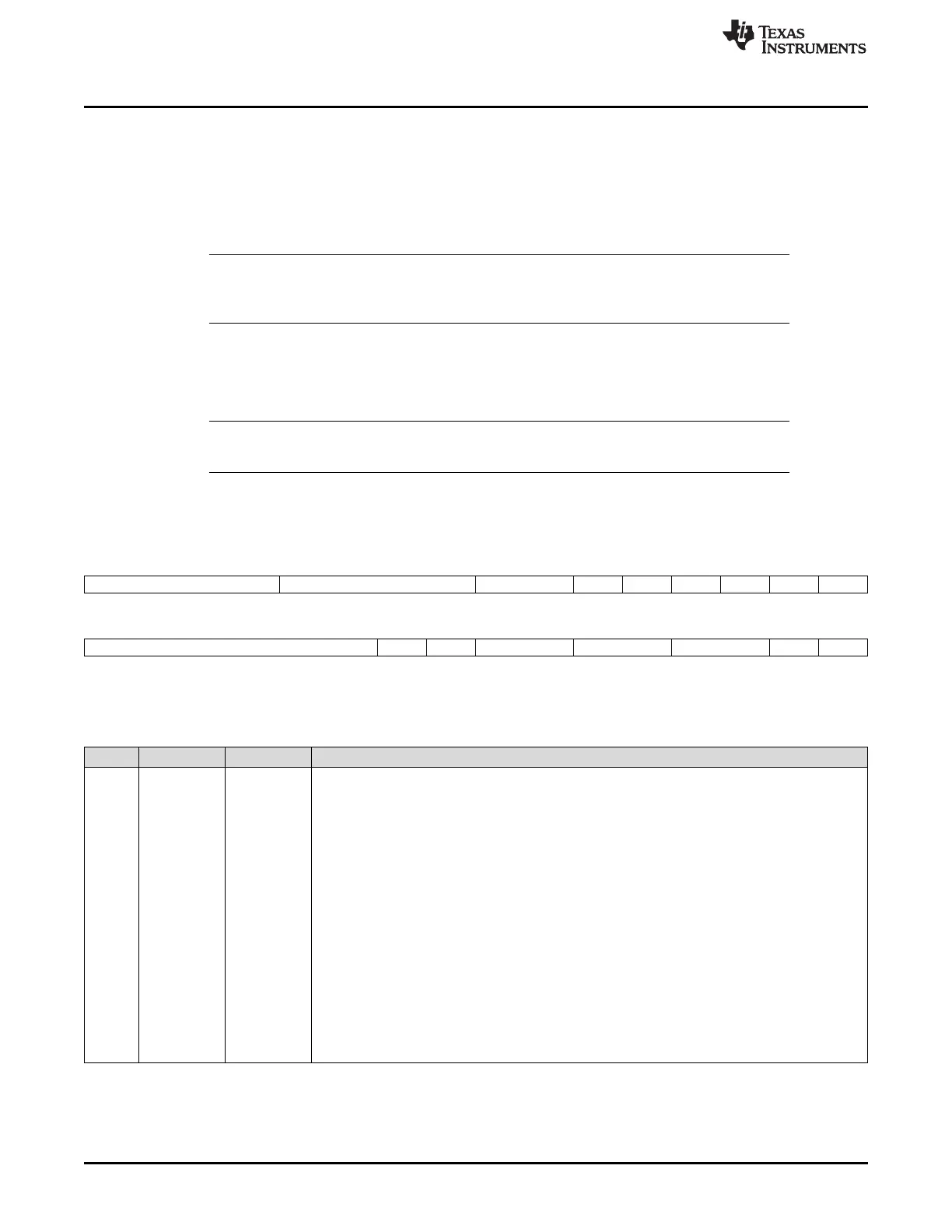

Figure 26-113. Test Register 1 (TEST1) [offset_CC = 10h]

31 28 27 24 23 22 21 20 19 18 17 16

CERB CERA Reserved TXENB TXENA TXB TXA RXB RXA

R-0 R-0 R-0 R/W-0 R/W-0 R/W-0 R/W-0 R-0 R-0

15 10 9 8 7 6 5 4 3 2 1 0

Reserved AOB AOA Reserved TMC Reserved ELBE WRTEN

R-0 R/W-1 R-0 R/W-0 R-0 R/W-0 R/W-0

LEGEND: R = Read only; R/W = Read/Write; -n = value after reset

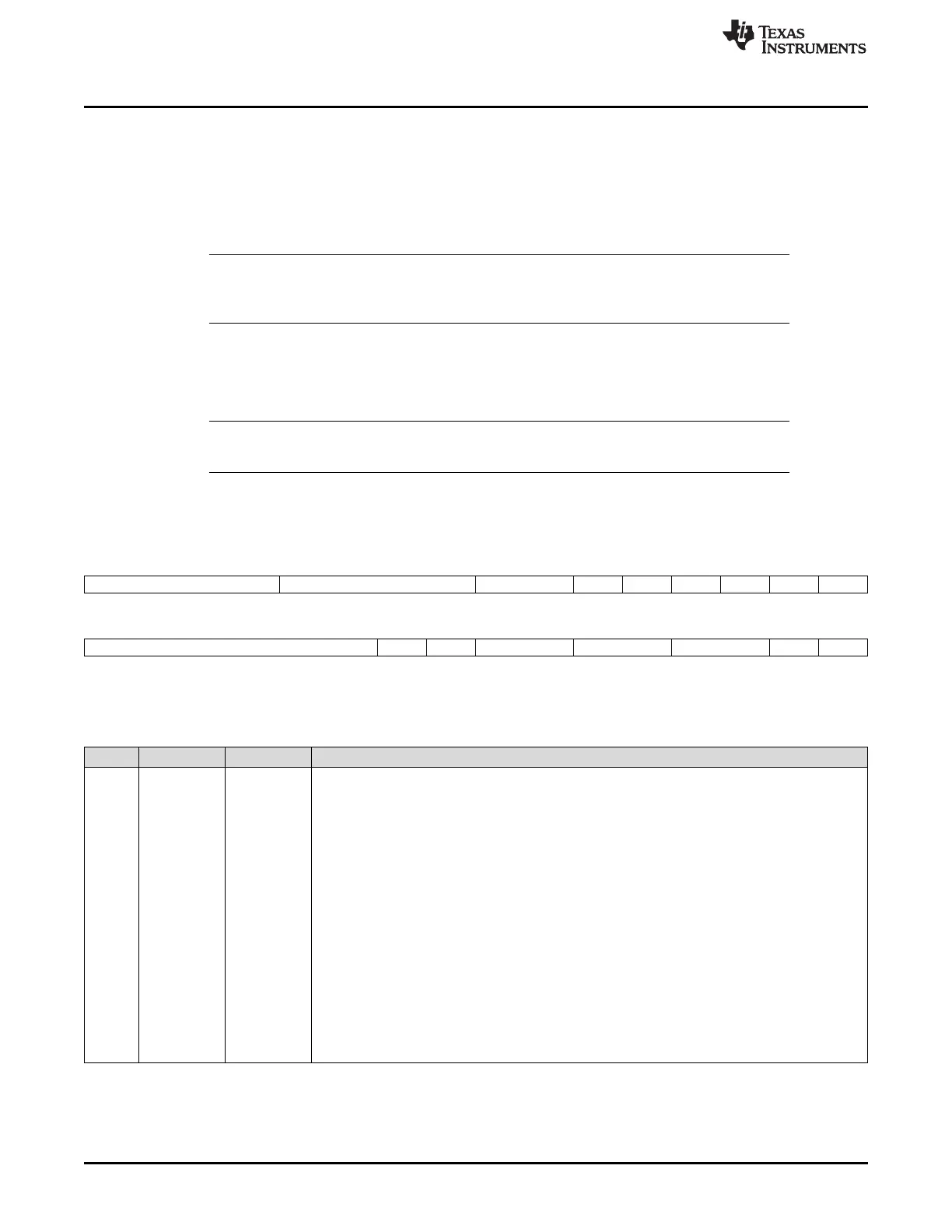

Table 26-93. Test Register 1 (TEST1) Field Descriptions

Bit Field Value Description

31-28 CERB Coding Error Report Channel B.

Set when a coding error is detected on channel B. Reset to 0 when register TEST1 is read or

written. Once the CERB is set it will remain unchanged until the Host accesses the TEST1

register.

0 No coding error is detected.

1h Header CRC error is detected.

2h Frame CRC error is detected.

3h Frame Start Sequence FSS too long.

4h First bit of Byte Start Sequence BSS seen LOW.

5h Second bit of Byte Start Sequence BSS seen HIGH.

6h First bit of Frame End Sequence FES seen HIGH.

7h Second bit of Frame End Sequence FES seen LOW.

8h CAS / MTS symbol seen too short.

9h CAS / MTS symbol seen too long.

Ah-Fh Reserved

Loading...

Loading...