FlexRay Module Registers

www.ti.com

1344

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

FlexRay Module

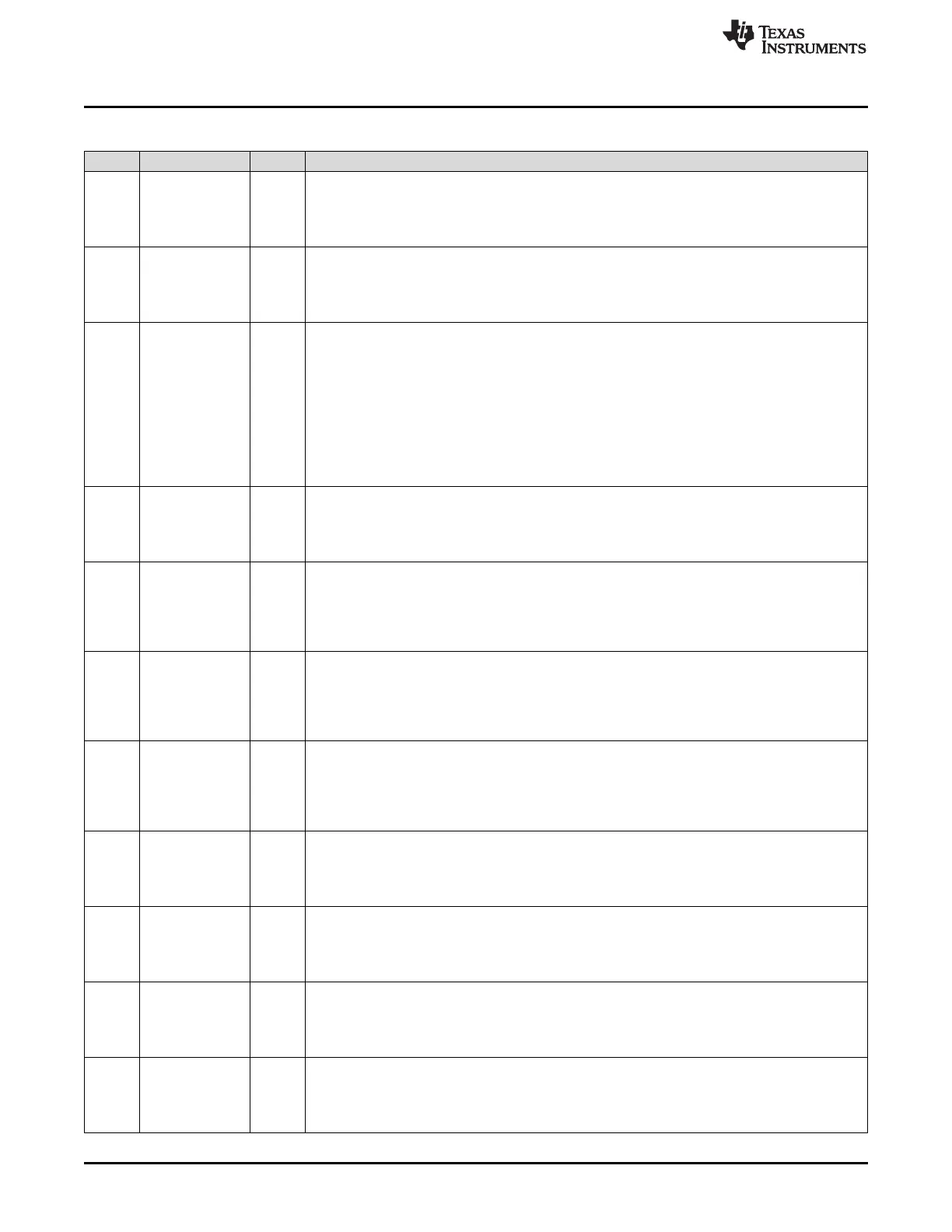

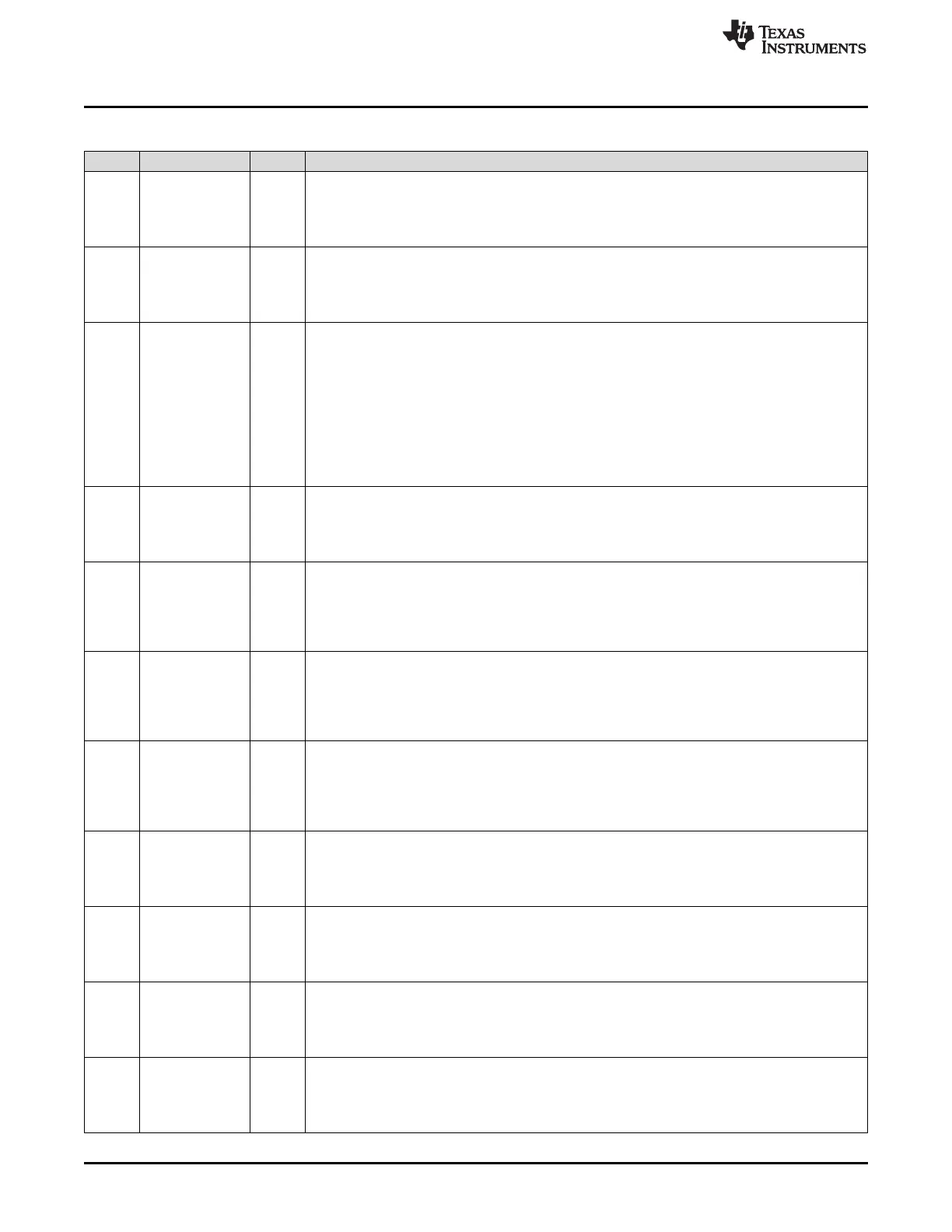

Table 26-97. Status Interrupt Register (SIR) Field Descriptions (continued)

Bit Field Value Description

16 WUPA Wakeup pattern channel A. This flag is set by the communication controller when a wakeup pattern

was received on channel A.

0 No wakeup pattern is on channel A.

1 Wakeup pattern is on channel A.

15 SDS Start of Dynamic Segment. This flag is set by the communication controller when the dynamic

segment starts.

0 Dynamic segment is not yet started.

1 Dynamic segment is started.

14 MBSI Message buffer status interrupt. This flag is set by the communication controller if bit MBI of a

dedicated receive buffer is set to 1 and when the status of that message buffer has been updated

due to reception of a:

• valid frame with payload

• valid frame with payload zero

• null frame

• corrupted frame or an empty slot

0 No message buffer status has been updated.

1 Message buffer status of at least one receive buffer has been updated.

13 SUCS Startup completed successfully. This flag is set whenever a startup completed successfully and the

communication controller entered NORMAL_ACTIVE state.

0 No startup is completed successfully.

1 Startup is completed successfully.

12 SWE Stop watch event. If enabled by the respective control bits located in the Stop watch register, a

detected edge on external stop watch pin or a software trigger event will generate a stop watch

event.

0 No stop watch event.

1 Stop watch event occurred.

11 TOBC Transfer output buffer completed. This flag is set whenever a transfer from the message RAM to

the output buffer has completed and bit OBSYS in the output buffer command request register has

been reset by the message handler.

0 No transfer is completed since bit was reset.

1 Transfer between message RAM and output buffer is completed.

10 TIBC Transfer input buffer completed. This flag is set whenever a transfer from input buffer to the

message RAM has completed and bit IBSYS in the input buffer command request register has

been reset by the message handler.

0 No transfer is completed since bit was reset.

1 Transfer between input buffer and message RAM is completed.

9 TI1 Timer interrupt 1. This flag is set whenever the conditions programmed in the timer interrupt 1

configuration register are met. A timer interrupt 1 is also signaled on pin CC_tint1.

0 No timer interrupt 1.

1 Timer interrupt 1 occurred.

8 TI0 Timer interrupt 0. This flag is set whenever the conditions programmed in the timer interrupt 0

configuration register are met. A timer interrupt 0 is also signaled on pin CC_tint0.

0 No timer interrupt 0.

1 Timer interrupt 0 occurred.

7 NMVC Network management vector changed. This interrupt flag signals a change in the Network

management vector visible to the host.

0 No change in the network management vector.

1 Network management vector is changed.

6 RFCL Receive FIFO critical level. This flag is set when the receive FIFO fill level FSR.RFFL is equal or

greater than the critical level as configured by FCL.CL.

0 Receive FIFO is below critical level.

1 Receive FIFO critical level is reached.

Loading...

Loading...