www.ti.com

FlexRay Module Registers

1345

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

FlexRay Module

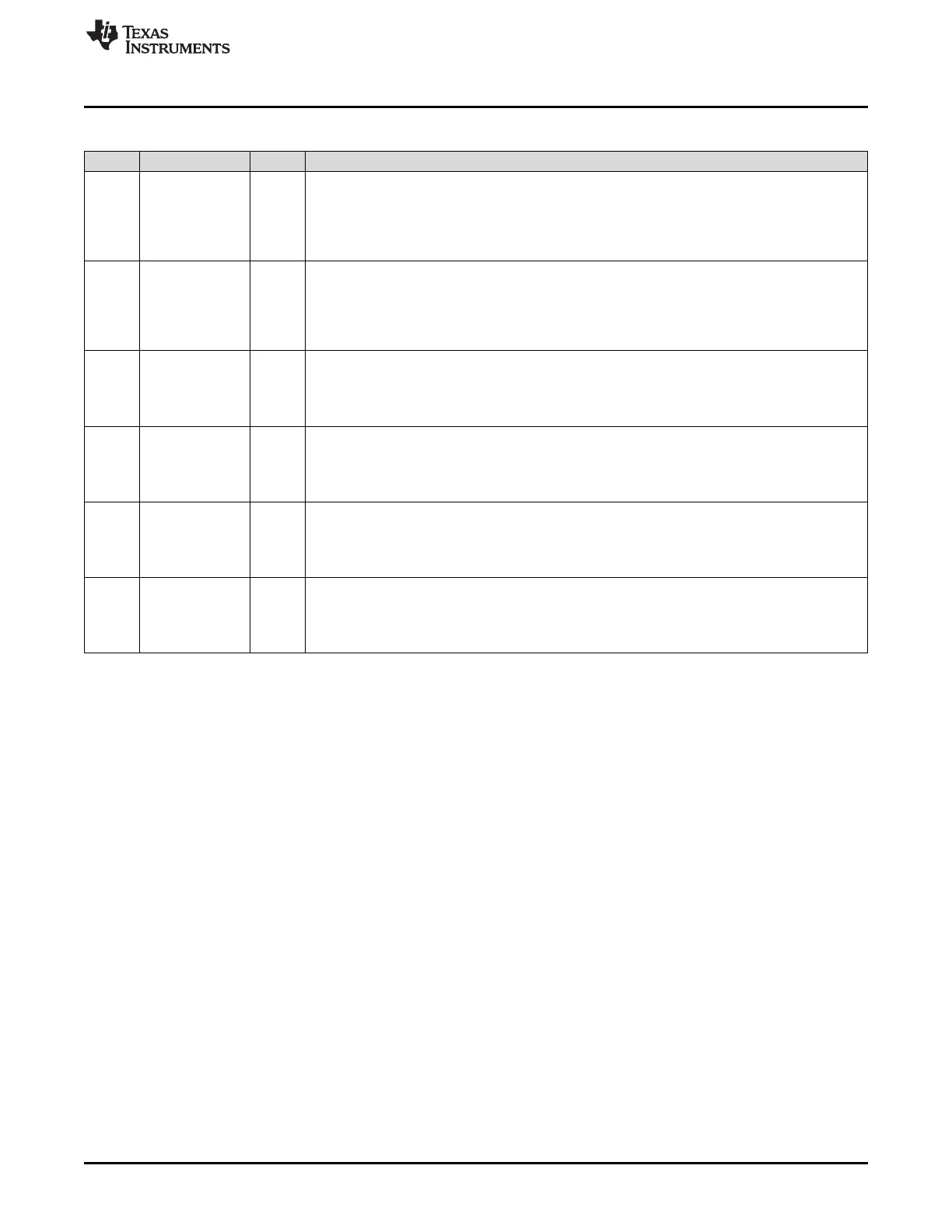

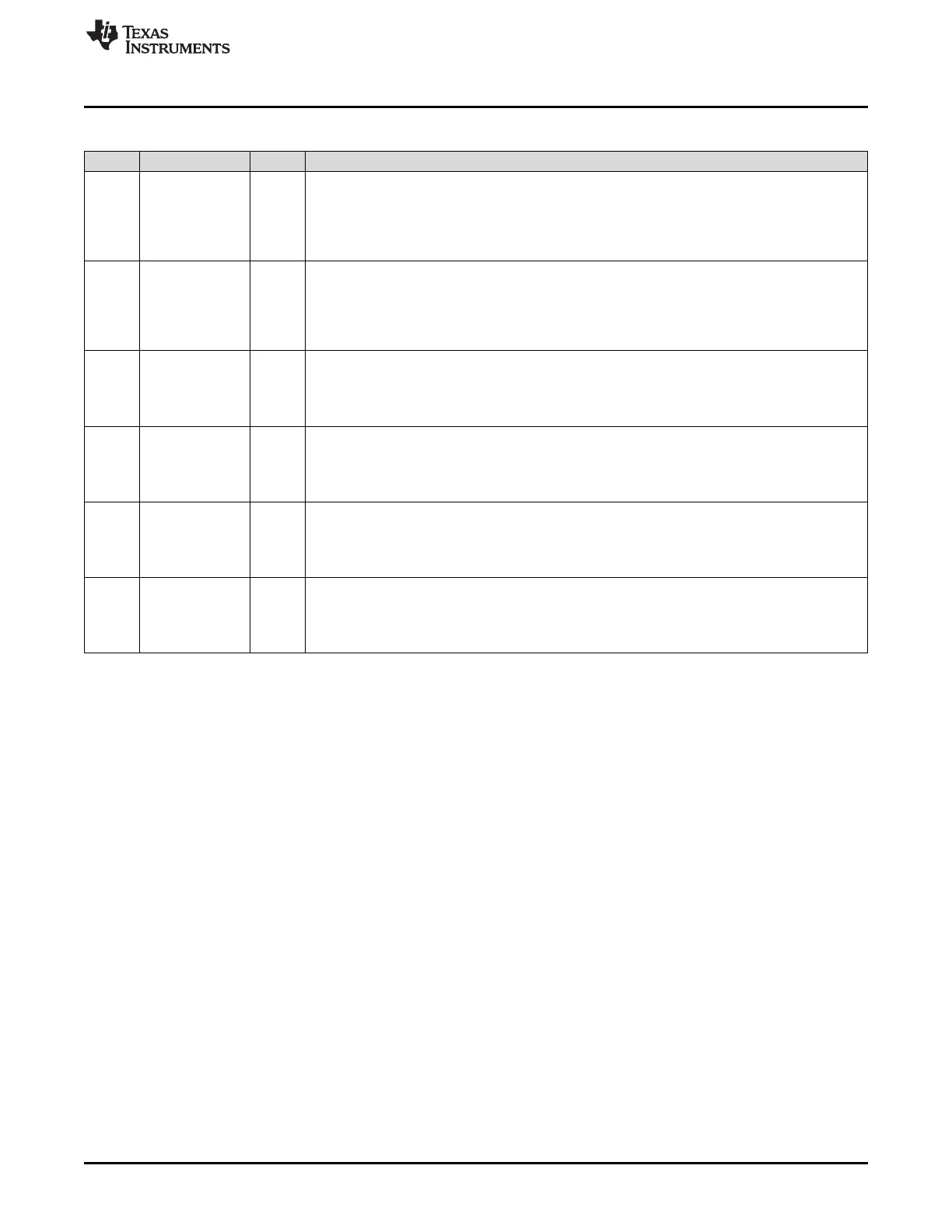

Table 26-97. Status Interrupt Register (SIR) Field Descriptions (continued)

Bit Field Value Description

5 RFNE Receive FIFO not empty. This flag is set by the communication controller when a received valid

frame was stored into the empty receive FIFO. The actual state of the receive FIFO is monitored in

register FSR.

0 Receive FIFO is empty.

1 Receive FIFO is not empty.

4 RXI Receive interrupt. This flag is set by the communication controller when the payload segment of a

received valid frame was stored into the data section of a matching dedicated receive buffer and if

bit MBI of that message buffer is set to 1.

0 No data section has been updated.

1 At least one data section has been updated.

3 TXI Transmit interrupt. This flag is set by the communication controller after successful frame

transmission if bit MBI in the respective message buffer is set to 1.

0 No frame is transmitted.

1 At least one frame was transmitted successfully.

2 CYCS Cycle start interrupt. This flag is set by the communication controller when a communication cycle

starts.

0 No communication cycle is started.

1 Communication cycle is started.

1 CAS Collision avoidance symbol. This flag is set by the communication controller when a CAS was

received.

0 No CAS symbol is received.

1 CAS symbol is received.

0 WST This flag is set when WSV in the communication controller status vector register changes to a value

other than UNDEFINED.

0 Wakeup status is unchanged.

1 Wakeup status is changed.

Loading...

Loading...