FlexRay Module Registers

www.ti.com

1346

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

FlexRay Module

26.3.2.2.3 Error Interrupt Line Select (EILS)

The settings in the error interrupt line select register assigns an interrupt generated by a specific error

interrupt flag to one of the two module interrupt lines (CC_int0 or CC_int1).

Figure 26-119 and Table 26-98 illustrate this register.

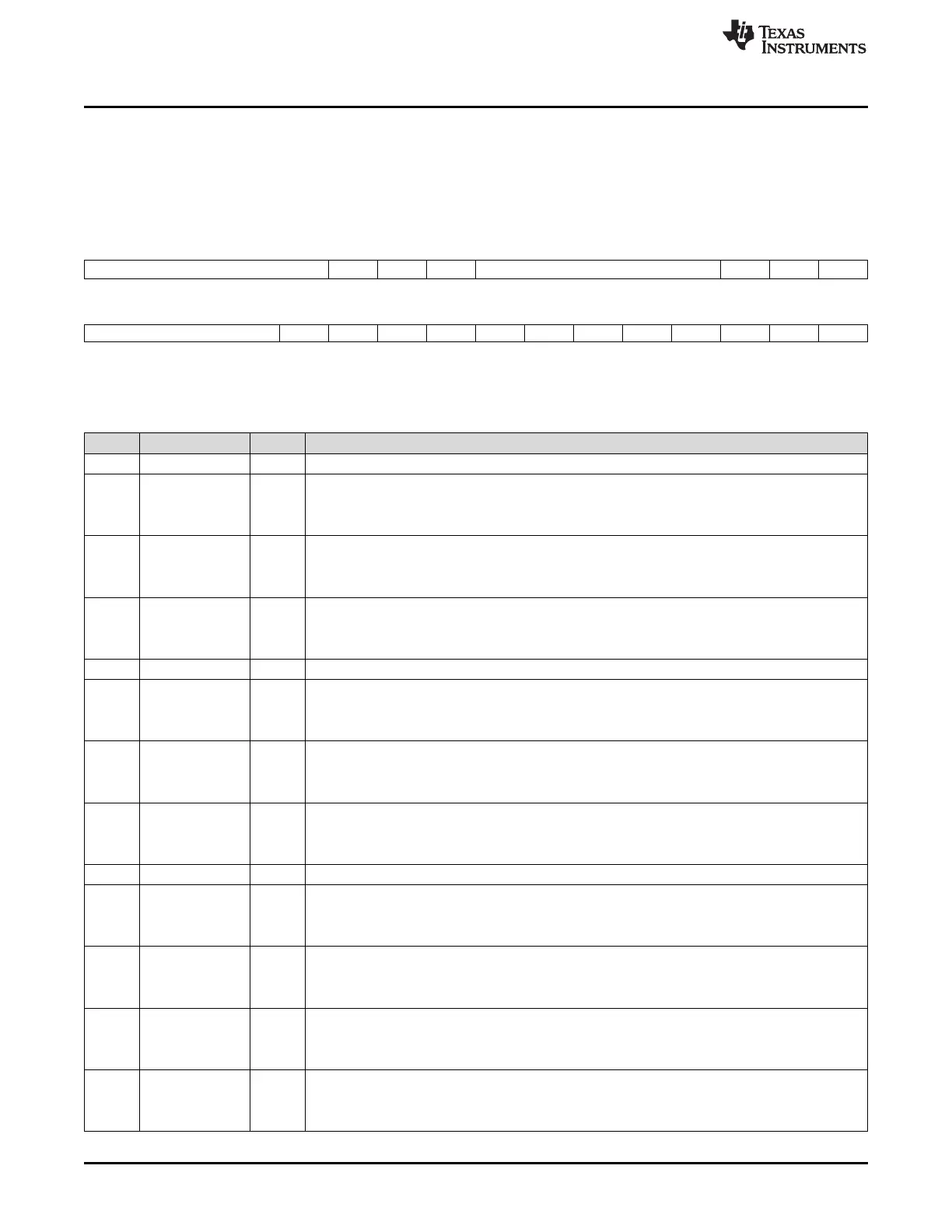

Figure 26-119. Error Interrupt Line Select Register (EILS) [offset_CC = 28h]

31 27 26 25 24 23 19 18 17 16

Reserved TABBL LTVBL EDBL Reserved TABAL LTVAL EDAL

R-0 R/W-0 R/W-0 R/W-0 R-0 R/W-0 R/W-0 R/W-0

15 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved MHFL IOBAL IIBAL EFAL RFOL UCREL CCLL CCFL SFOL SFBML CNAL PEMCL

R-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

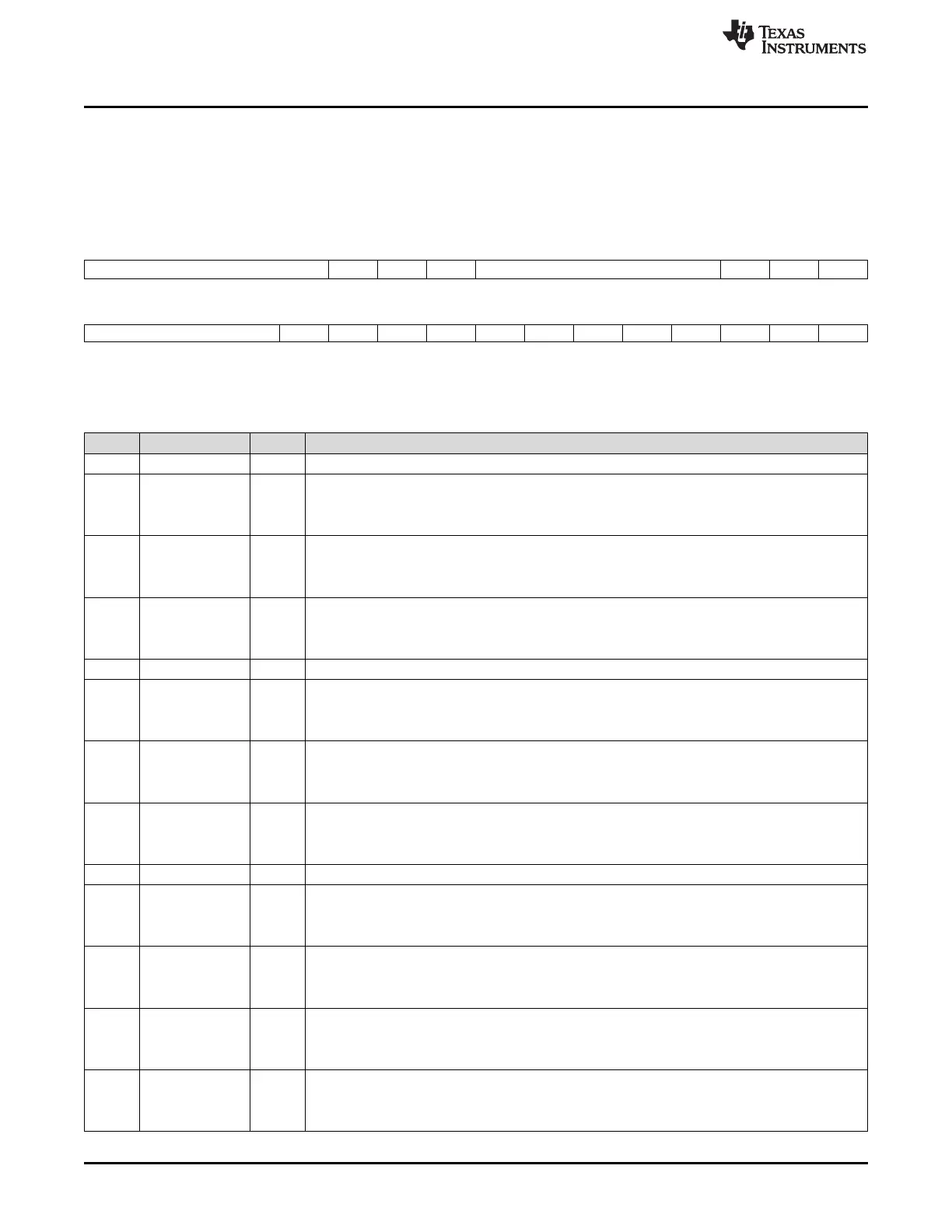

Table 26-98. Error Interrupt Line Select Register (EILS) Field Descriptions

Bit Field Value Description

31-27 Reserved 0 Reads return 0. Writes have no effect.

26 TABBL Transmission across boundary channel B interrupt line.

0 Interrupt is assigned to interrupt line CC_int0.

1 Interrupt is assigned to interrupt line CC_int1.

25 LTVBL Latest transmit violation channel B interrupt line.

0 Interrupt is assigned to interrupt line CC_int0.

1 Interrupt is assigned to interrupt line CC_int1.

24 EDBL Error detected on channel B interrupt line.

0 Interrupt is assigned to interrupt line CC_int0.

1 Interrupt is assigned to interrupt line CC_int1.

23-19 Reserved 0 Reads return 0. Writes have no effect.

18 TABAL Transmission across boundary channel A interrupt line.

0 Interrupt is assigned to interrupt line CC_int0.

1 Interrupt is assigned to interrupt line CC_int1.

17 LTVAL Latest transmit violation channel A interrupt line.

0 Interrupt is assigned to interrupt line CC_int0.

1 Interrupt is assigned to interrupt line CC_int1.

16 EDAL Error detected on channel A interrupt line.

0 Interrupt is assigned to interrupt line CC_int0.

1 Interrupt is assigned to interrupt line CC_int1.

15-12 Reserved 0 Reads return 0. Writes have no effect.

11 MHFL Message handler constraints flag interrupt line.

0 Interrupt is assigned to interrupt line CC_int0.

1 Interrupt is assigned to interrupt line CC_int1.

10 IOBAL Illegal output buffer access interrupt line.

0 Interrupt is assigned to interrupt line CC_int0.

1 Interrupt is assigned to interrupt line CC_int1.

9 IIBAL Illegal output buffer access interrupt line.

0 Interrupt is assigned to interrupt line CC_int0.

1 Interrupt is assigned to interrupt line CC_int1.

8 EFAL Empty FIFO access interrupt line.

0 Interrupt is assigned to interrupt line CC_int0.

1 Interrupt is assigned to interrupt line CC_int1.

Loading...

Loading...