4 3 2 1 0 4 3

0

12

4 3 2 1 0 4 3 012

Master SPI

Interrupt flag

Slave SPI

Interrupt flag

SPISOMI

from slave

SPISIMO

from master

Clock polarity = 1

Clock phase = 1

SPICS

SPICLK signal options:

SPIENA

Clock polarity = 1

Clock phase = 0

Clock polarity = 0

Clock polarity = 0

Clock phase = 0

Clock phase = 1

Basic Operation

www.ti.com

1514

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Multi-Buffered Serial Peripheral Interface Module (MibSPI) with Parallel Pin

Option (MibSPIP)

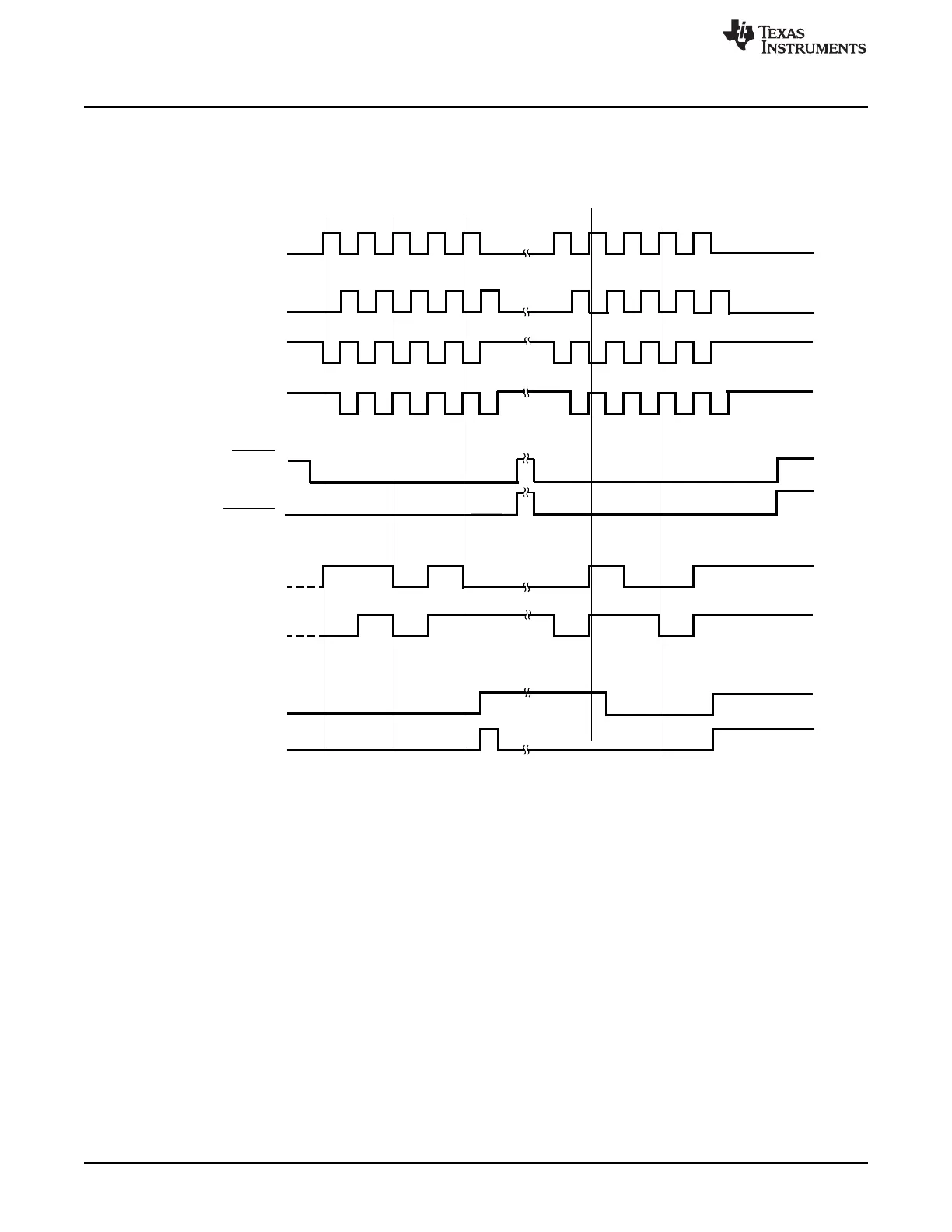

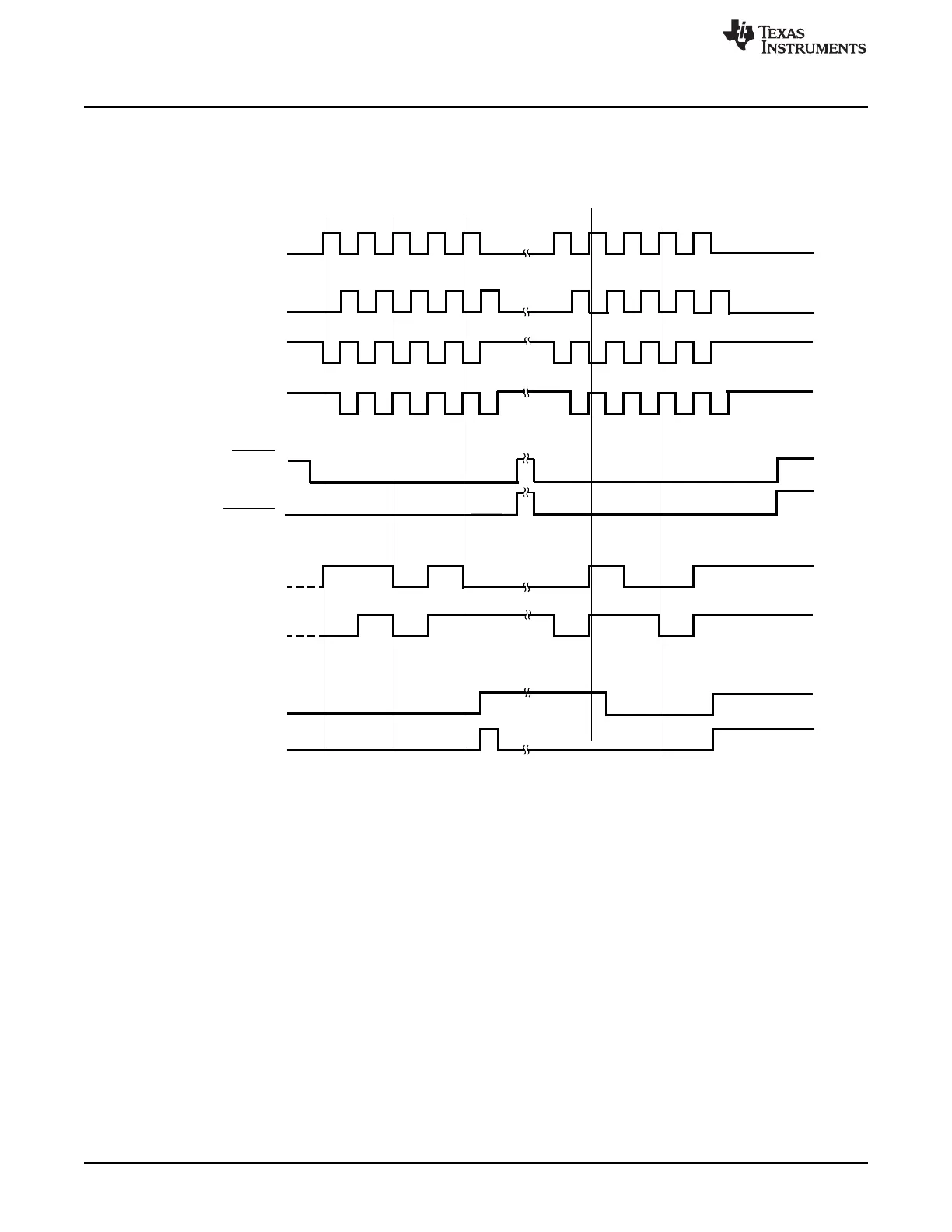

28.2.6.2.1 Data Transfer Example

Figure 28-16 illustrates a SPI data transfer between two devices using a character length of five bits.

Figure 28-16. Five Bits per Character (5-Pin Option)

Loading...

Loading...