SCI/LIN Control Registers

www.ti.com

1694

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Serial Communication Interface (SCI)/ Local Interconnect Network (LIN)

Module

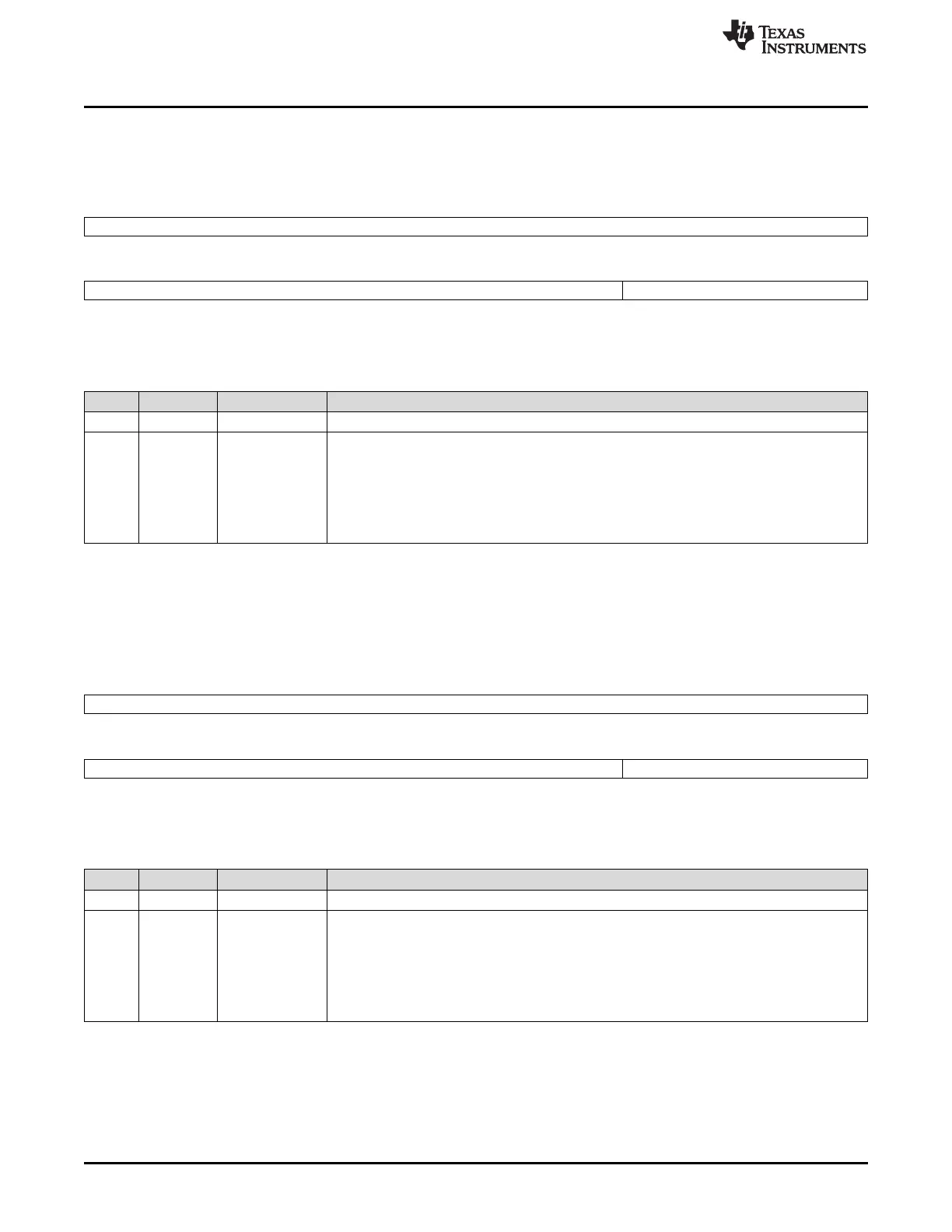

29.7.9 SCI Interrupt Vector Offset 0 (SCIINTVECT0)

Figure 29-36 and Table 29-21 illustrate this register.

Figure 29-36. SCI Interrupt Vector Offset 0 (SCIINTVECT0) (offset = 20h)

31 16

Reserved

R-0

15 5 4 0

Reserved INTVECT0

R-0 R-0

LEGEND: R = Read only; -n = value after reset

Table 29-21. SCI Interrupt Vector Offset 0 (SCIINTVECT0) Field Descriptions

Bit Field Value Description

31-5 Reserved 0 Reads return 0. Writes have no effect.

4-0 INVECT0 0-1Fh Interrupt vector offset for INT0. This register indicates the offset for interrupt line INT0. A read to

this register updates its value to the next highest priority pending interrupt in SCIFLR and clears

the flag in SCIFLR corresponding to the offset that was read. See Table 29-4 for a list of the

interrupts.

Note: The flags for the receive (SCIFLR[9]) and the transmit (SCIFLR[8]) interrupt cannot

be cleared by reading the corresponding offset vector in this register (see detailed

description in SCIFLR register).

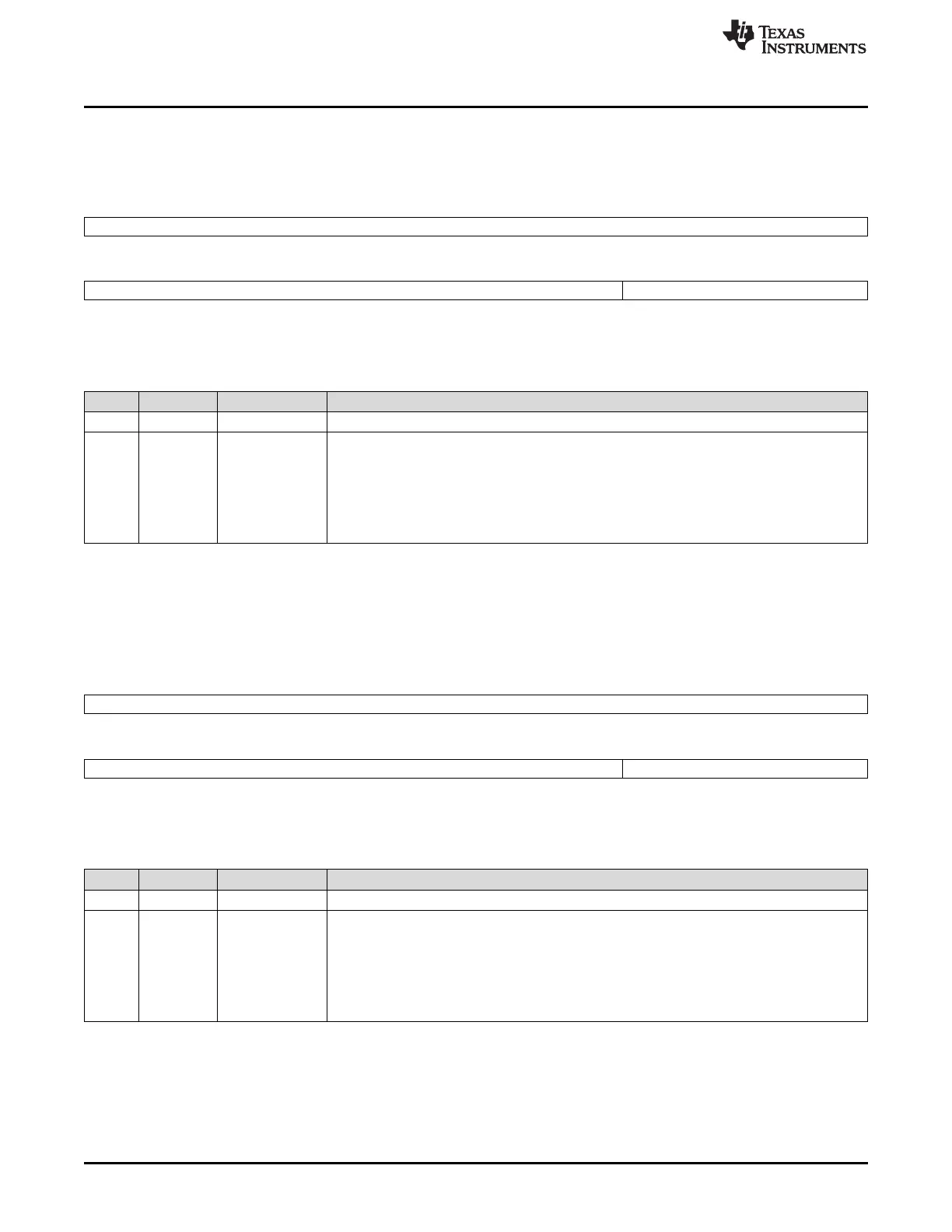

29.7.10 SCI Interrupt Vector Offset 1 (SCIINTVECT1)

Figure 29-37 and Table 29-22 illustrate this register.

Figure 29-37. SCI Interrupt Vector Offset 1 (SCIINTVECT1) (offset = 24h)

31 16

Reserved

R-0

15 5 4 0

Reserved INTVECT1

R-0 R-0

LEGEND: R = Read only; -n = value after reset

Table 29-22. SCI Interrupt Vector Offset 1 (SCIINTVECT1) Field Descriptions

Bit Field Value Description

31-5 Reserved 0 Reads return 0. Writes have no effect.

4-0 INVECT1 0-1Fh Interrupt vector offset for INT1. This register indicates the offset for interrupt line INT1. A read to

this register updates its value to the next highest priority pending interrupt in SCIFLR and clears

the flag in SCIFLR corresponding to the offset that was read. See Table 29-4 for list of

interrupts.

Note: The flags for the receive (SCIFLR[9]) and the transmit (SCIFLR[8]) interrupt cannot

be cleared by reading the corresponding offset vector in this register (see detailed

description in SCIFLR register).

Loading...

Loading...