SCI/LIN Control Registers

www.ti.com

1698

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Serial Communication Interface (SCI)/ Local Interconnect Network (LIN)

Module

29.7.13 SCI Data Buffers (SCIED, SCIRD, SCITD)

The SCI has three addressable registers in which transmit and receive data is stored. These three

registers are available in SCI mode only.

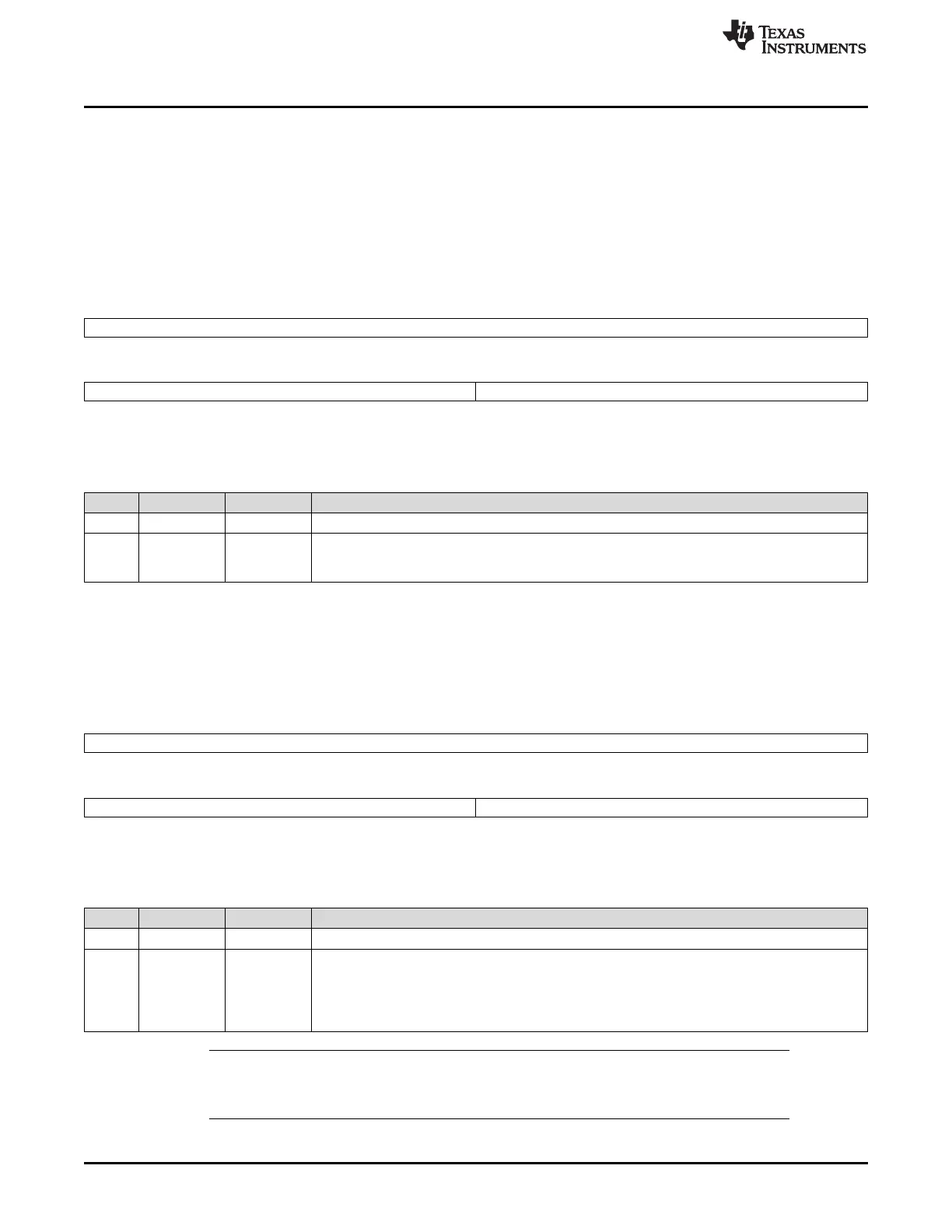

29.7.13.1 Receiver Emulation Data Buffer (SCIED)

The SCIED register is addressed at a location different from SCIRD, but is physically the same register.

Figure 29-40 and Table 29-26 illustrate this register.

Figure 29-40. Receiver Emulation Data Buffer (SCIED) (offset = 30h)

31 16

Reserved

R-0

15 8 7 0

Reserved ED

R-0 R-0

LEGEND: R = Read only; -n = value after reset

Table 29-26. Receiver Emulation Data Buffer (SCIED) Field Descriptions

Bit Field Value Description

31-8 Reserved 0 Reads return 0. Writes have no effect.

7-0 ED 0-FFh Emulator data. This bit is effective in SCI-compatible mode only. Reading SCIED[7:0] does not

clear the RXRDY flag, unlike reading SCIRD. This register should be used only by an emulator

that must continually read the data buffer without affecting the RXRDY flag.

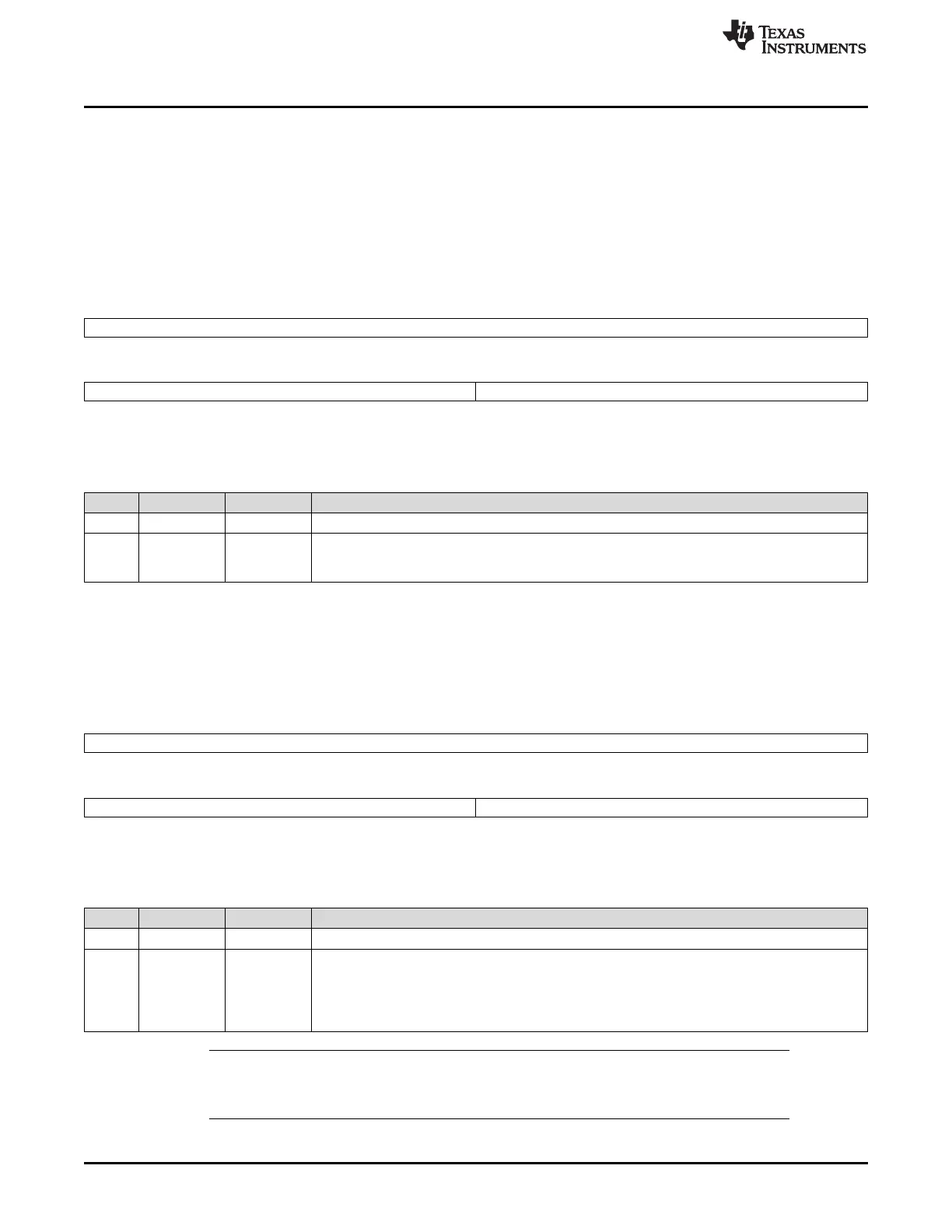

29.7.13.2 Receiver Data Buffer (SCIRD)

This register provides a location for the receiver data. Figure 29-41 and Table 29-27 illustrate this register.

Figure 29-41. Receiver Data Buffer (SCIRD) (offset = 34h)

31 16

Reserved

R-0

15 8 7 0

Reserved RD

R-0 R-0

LEGEND: R = Read only; -n = value after reset

Table 29-27. Receiver Data Buffer (SCIRD) Field Descriptions

Bit Field Value Description

31-8 Reserved 0 Reads return 0. Writes have no effect.

7-0 RD 0-FFh Receiver data. This bit is effective in SCI-compatible mode only. When a frame has been

completely received, the data in the frame is transferred from the receiver shift register SCIRXSHF

to this register. As this transfer occurs, the RXRDY flag is set and a receive interrupt is generated

if SET RX INT is set.

Note: When the data is read from SCIRD, the RXRDY flag is automatically cleared.

NOTE: When the SCI receives data that is fewer than eight bits in length, it loads the data into this

register in a left justified format padded with trailing zeros. Therefore, your software should

perform a logical shift on the data by the correct number of positions to make it right justified.

Loading...

Loading...