System and Peripheral Control Registers

www.ti.com

170

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Architecture

2.5.1.19 Clock Source Valid Status Register (CSVSTAT)

The CSVSTAT register, shown in Figure 2-26 and described in Table 2-38, indicates the status of usable

clock sources.

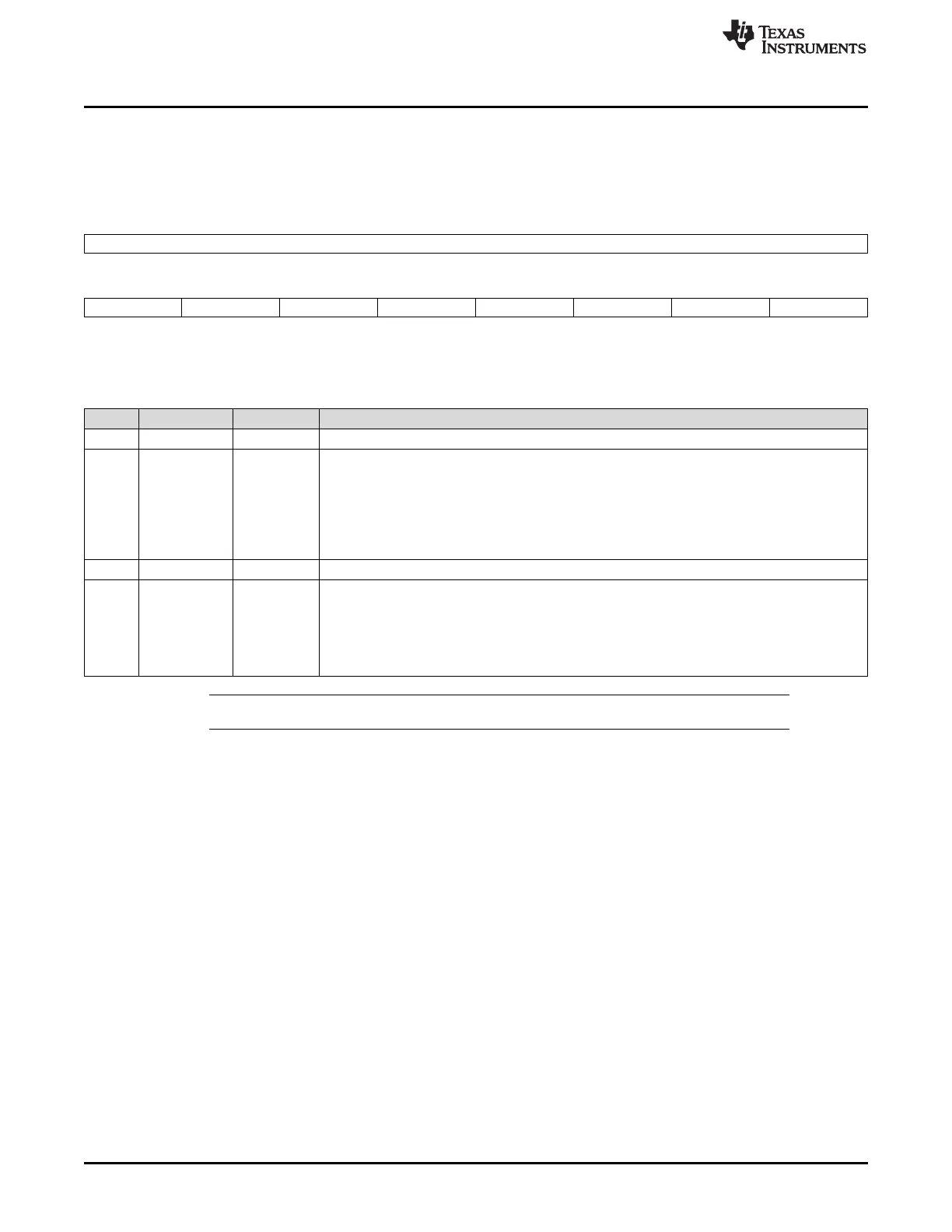

Figure 2-26. Clock Source Valid Status Register (CSVSTAT) (offset = 54h)

31 8

Reserved

R-0

7 6 5 4 3 2 1 0

CLKSR7V CLKSR6V CLKSR5V CLKSR4V CLKSR3V Reserved CLKSR1V CLKSR0V

R-1 R-0 R-0 R-1 R-1 R-0 R-0 R-0

LEGEND: R = Read only; -n = value after reset

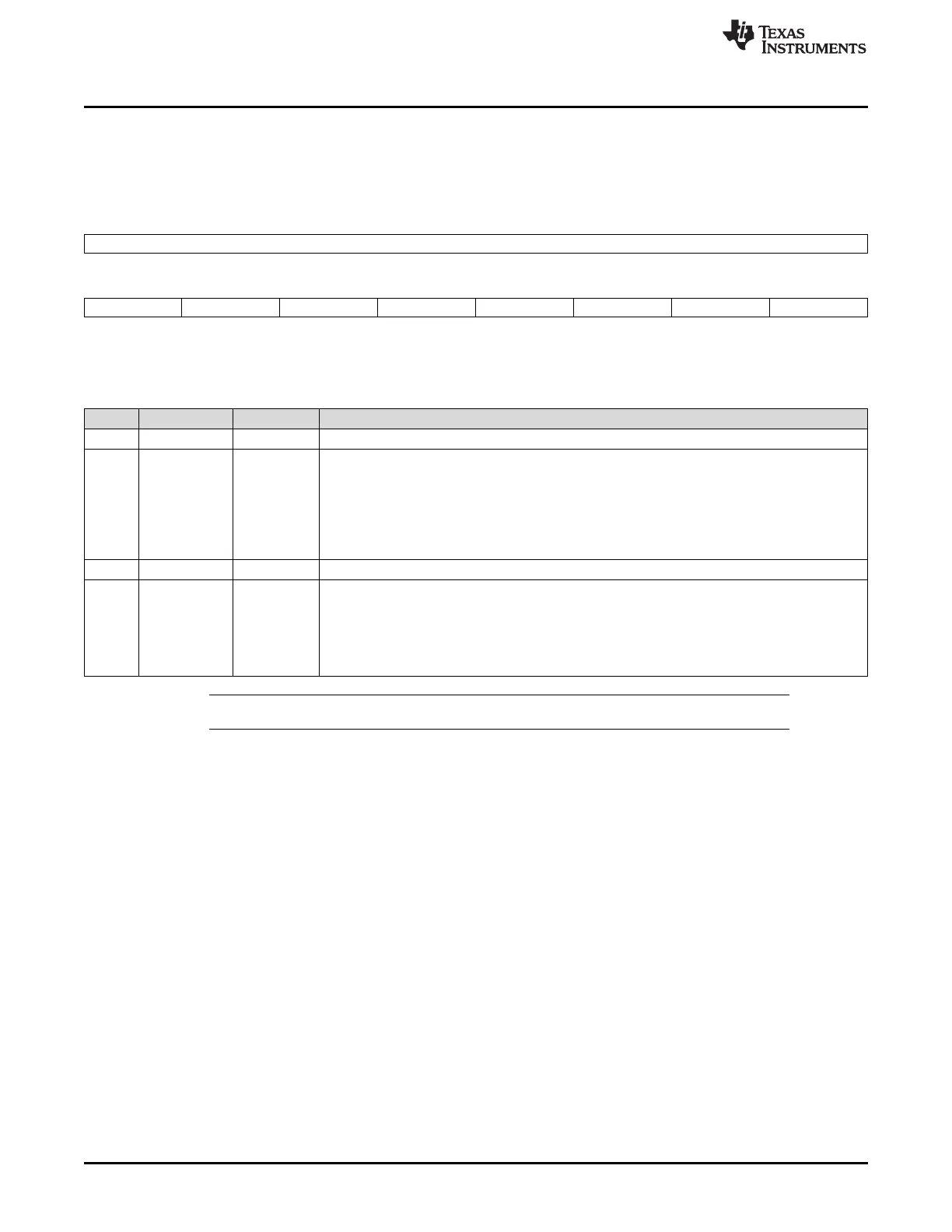

Table 2-38. Clock Source Valid Register (CSVSTAT) Field Descriptions

Bit Field Value Description

31-8 Reserved. 0 Reads return 0. Writes have no effect.

7-3 CLKSR[7-3]V Clock source[7-0] valid.

0 Clock source[7-0] is not valid.

1 Clock source[7-0] is valid.

Note: If the valid bit of the source of a clock domain is not set (that is, the clock source is

not fully stable), the respective clock domain is disabled by the Global Clock Module

(GCM).

2 Reserved. 0 Reads return 0. Writes have no effect.

1-0 CLKSR[1-0]V Clock source[1–0] valid.

0 Clock source[1–0] is not valid.

1 Clock source[1–0] is valid.

Note: If the valid bit of the source of a clock domain is not set (that is, the clock source is

not fully stable), the respective clock domain is disabled.

NOTE: A list of the available clock sources is shown in the Table 2-29.

Loading...

Loading...