www.ti.com

I2C Control Registers

1795

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Inter-Integrated Circuit (I2C) Module

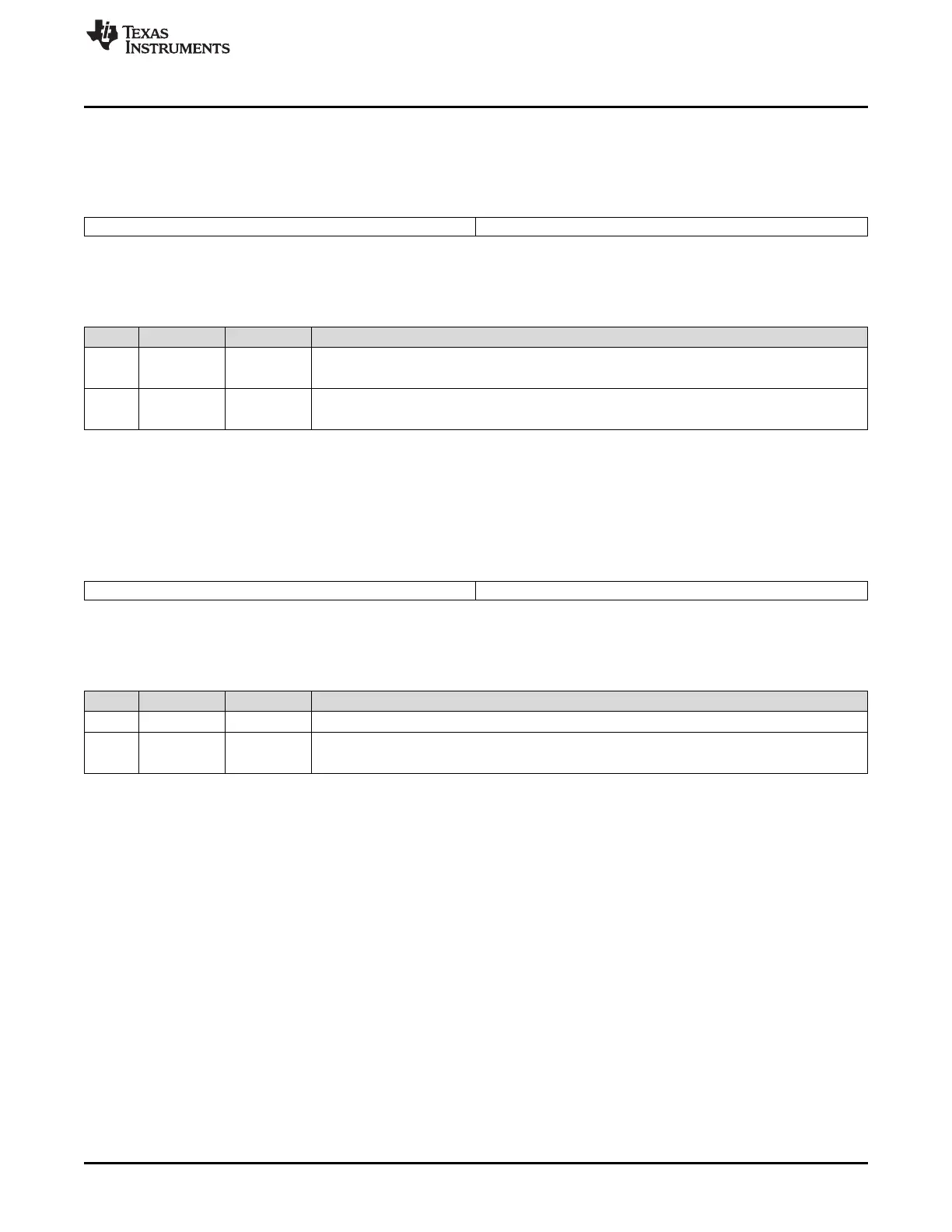

31.6.14 I2C Peripheral ID Register 1 (I2CPID1)

Figure 31-27 and Table 31-23 describe this register.

Figure 31-27. I2C Peripheral ID Register 1 (I2CPID1) [offset = 34h]

15 8 7 0

CLASS REVISION

R-1 R-46h

LEGEND: R = Read only; -n = value after reset

Table 31-23. I2C Peripheral ID Register 1 (I2CPID1) Field Descriptions

Bit Field Value Description

15-8 CLASS 0-FFh Peripheral class.

These bits identify the class of peripheral.

7-0 REVISION 0-FFh Revision level of the I2C.

These bits identify the revision level of the I2C.

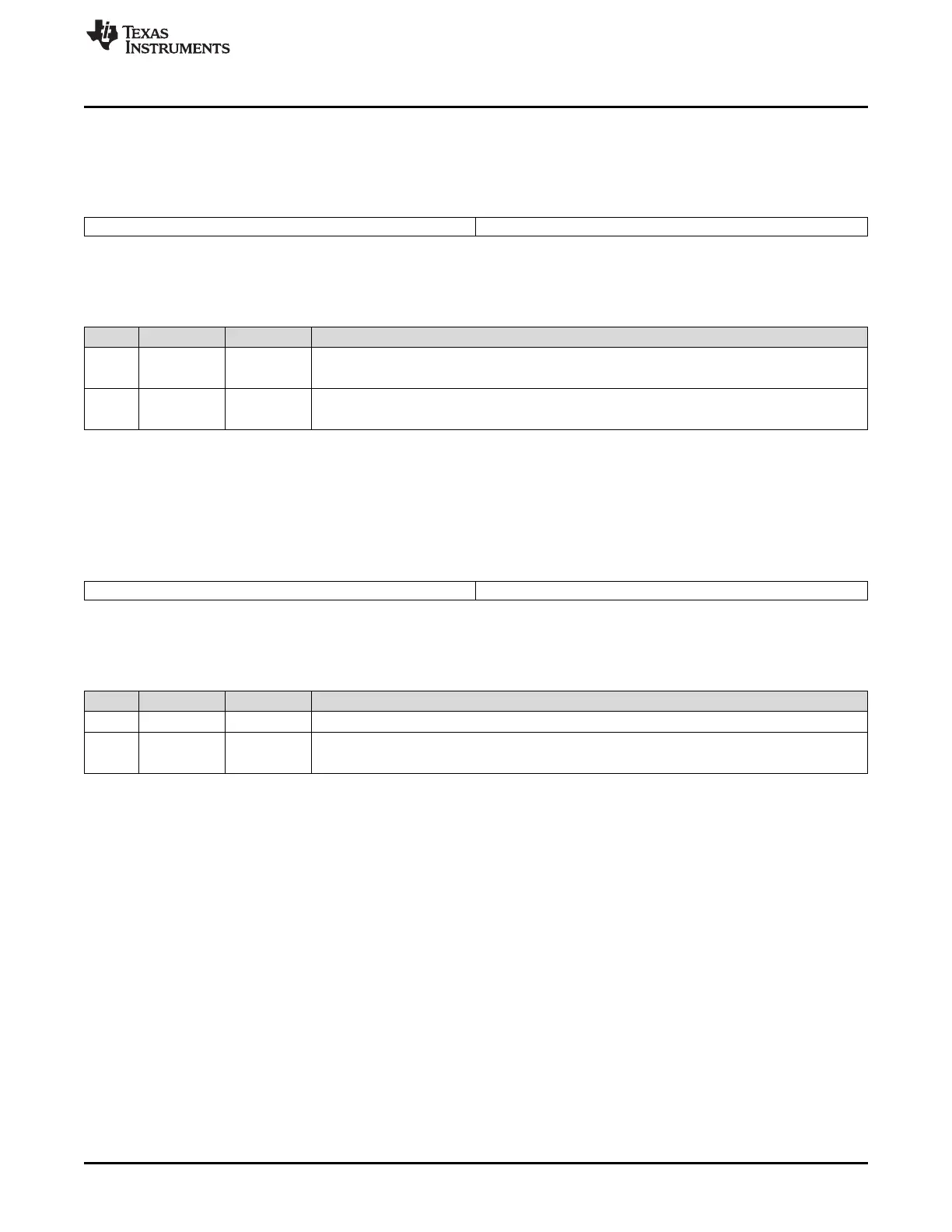

31.6.15 I2C Peripheral ID Register 2 (I2CPID2)

Figure 31-28 and Table 31-24 describe this register.

Figure 31-28. I2C Peripheral ID Register 2 (I2CPID2) [offset = 38h]

15 8 7 0

Reserved TYPE

R-0 R-5h

LEGEND: R = Read only; -n = value after reset

Table 31-24. I2C Peripheral ID Register 2 (I2CPID2) Field Descriptions

Bit Field Value Description

15-8 Reserved 0 Reads return 0. Writes have no effect.

7-0 TYPE 0-FFh Peripheral type.

These bits identify the type of peripheral.

Loading...

Loading...