MDIO Registers

www.ti.com

1872

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

EMAC/MDIO Module

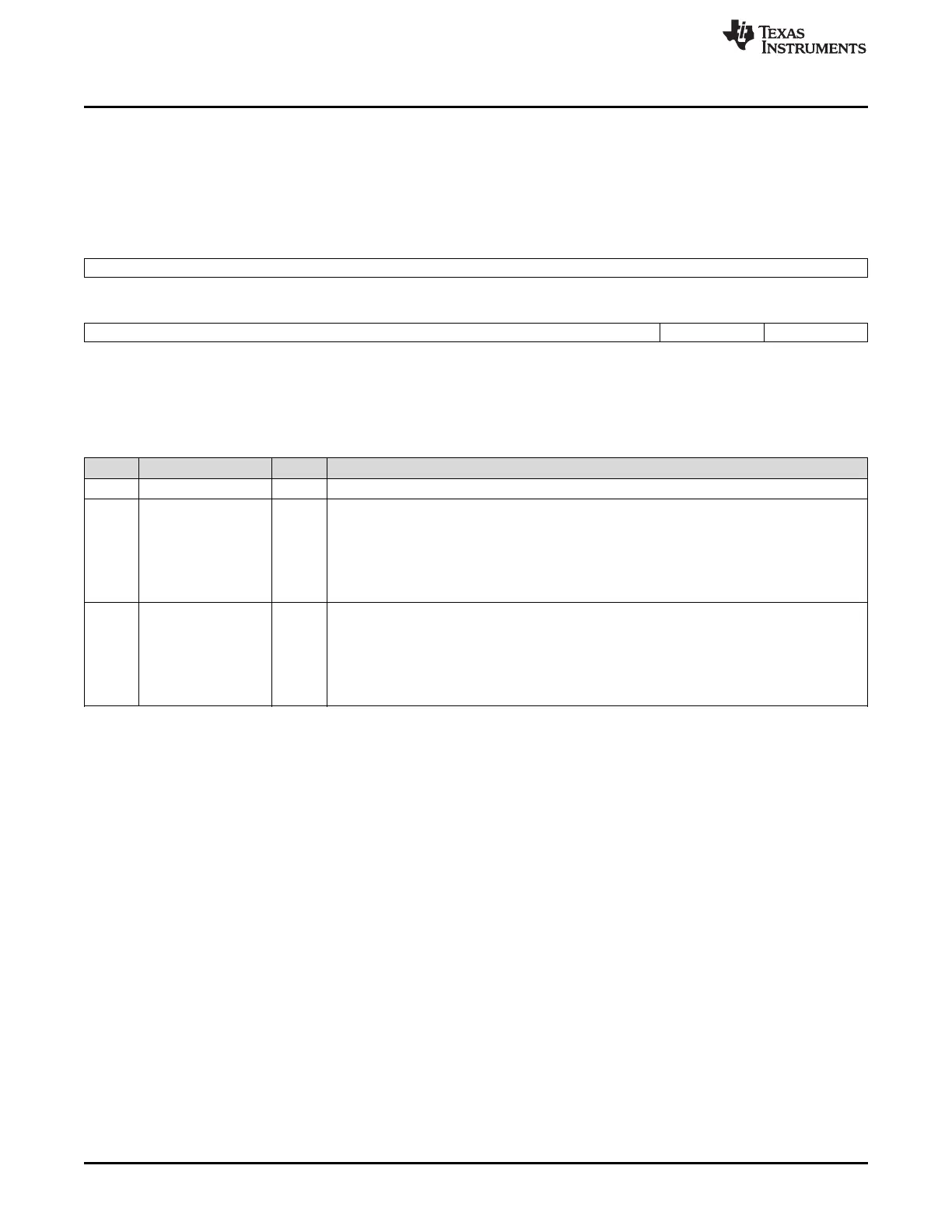

32.4.7 MDIO User Command Complete Interrupt (Unmasked) Register (USERINTRAW)

The MDIO user command complete interrupt (unmasked) register (USERINTRAW) is shown in

Figure 32-34 and described in Table 32-31.

Figure 32-34. MDIO User Command Complete Interrupt (Unmasked) Register (USERINTRAW)

(offset = 20h)

31 16

Reserved

R-0

15 2 1 0

Reserved USERACCESS1 USERACCESS0

R-0 R/W1C-0 R/W1C-0

LEGEND: R/W = Read/Write; R = Read only; W1C = Write 1 to clear (writing a 0 has no effect); -n = value after reset

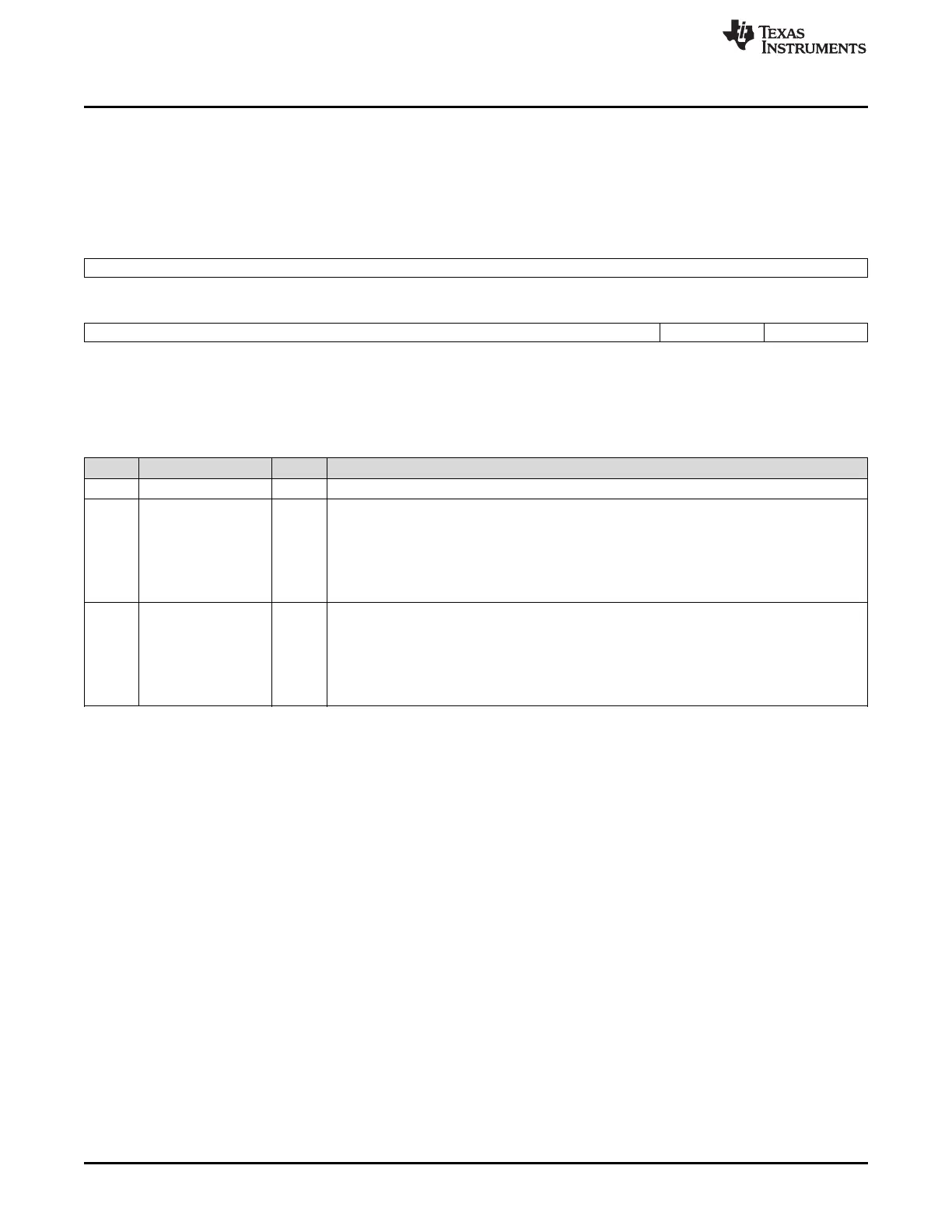

Table 32-31. MDIO User Command Complete Interrupt (Unmasked) Register (USERINTRAW)

Field Descriptions

Bit Field Value Description

31-2 Reserved 0 Reserved

1 USERACCESS1 MDIO User command complete event bit. When asserted, the bit indicates that the previously

scheduled PHY read or write command using the USERACCESS1 register has completed.

Writing a 1 will clear the event, writing a 0 has no effect.

0 No MDIO user command complete event.

1 The previously scheduled PHY read or write command using MDIO user access register

USERACCESS1 has completed.

0 USERACCESS0 MDIO User command complete event bit. When asserted, the bit indicates that the previously

scheduled PHY read or write command using the USERACCESS0 register has completed.

Writing a 1 will clear the event, writing a 0 has no effect.

0 No MDIO user command complete event.

1 The previously scheduled PHY read or write command using MDIO user access register

USERACCESS0 has completed.

Loading...

Loading...