www.ti.com

EMAC Module Registers

1893

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

EMAC/MDIO Module

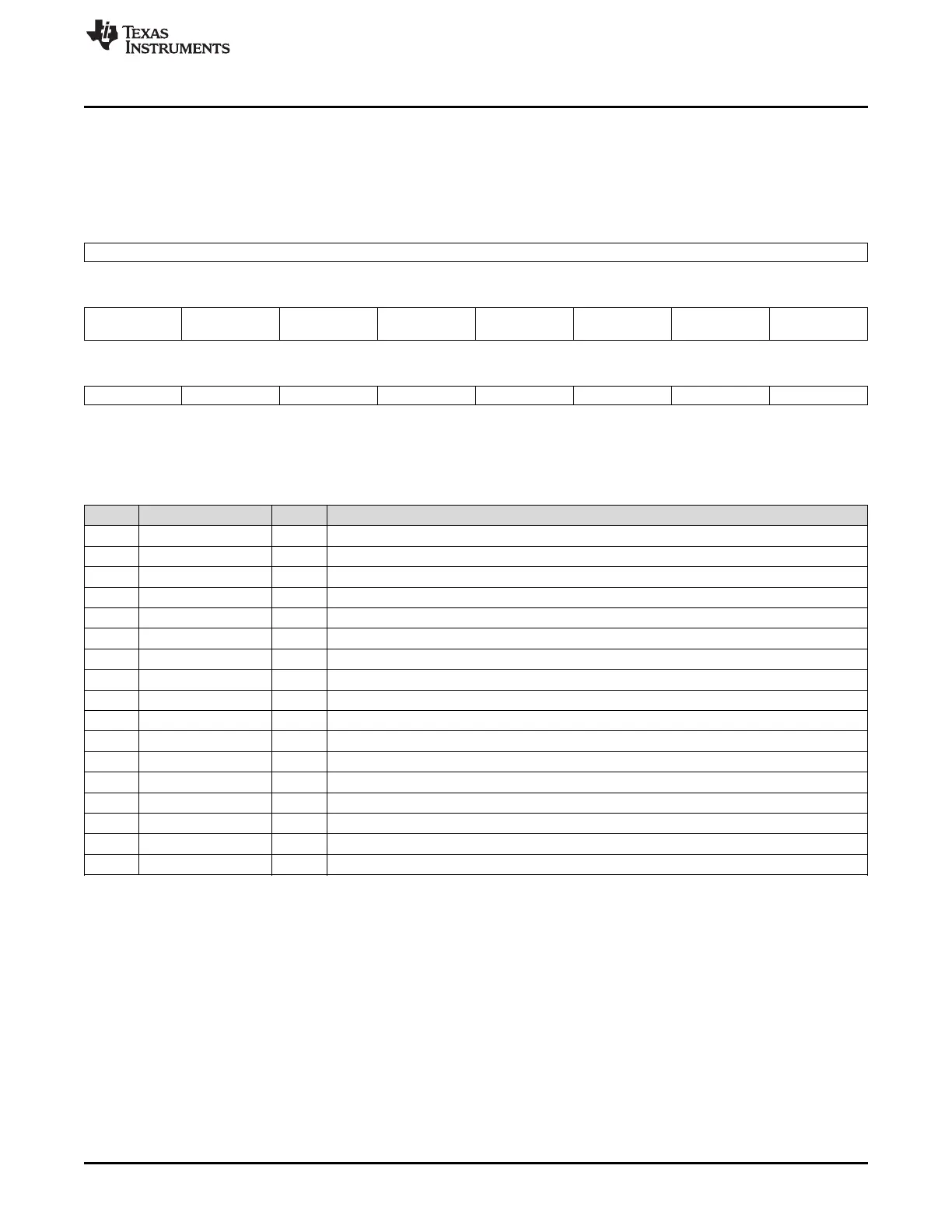

32.5.14 Receive Interrupt Status (Masked) Register (RXINTSTATMASKED)

The receive interrupt status (masked) register (RXINTSTATMASKED) is shown in Figure 32-55 and

described in Table 32-53.

Figure 32-55. Receive Interrupt Status (Masked) Register (RXINTSTATMASKED) (offset = A4h)

31 16

Reserved

R-0

15 14 13 12 11 10 9 8

RX7THRESH

PEND

RX6THRESH

PEND

RX5THRESH

PEND

RX4THRESH

PEND

RX3THRESH

PEND

RX2THRESH

PEND

RX1THRESH

PEND

RX0THRESH

PEND

R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0

7 6 5 4 3 2 1 0

RX7PEND RX6PEND RX5PEND RX4PEND RX3PEND RX2PEND RX1PEND RX0PEND

R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0

LEGEND: R = Read only; -n = value after reset

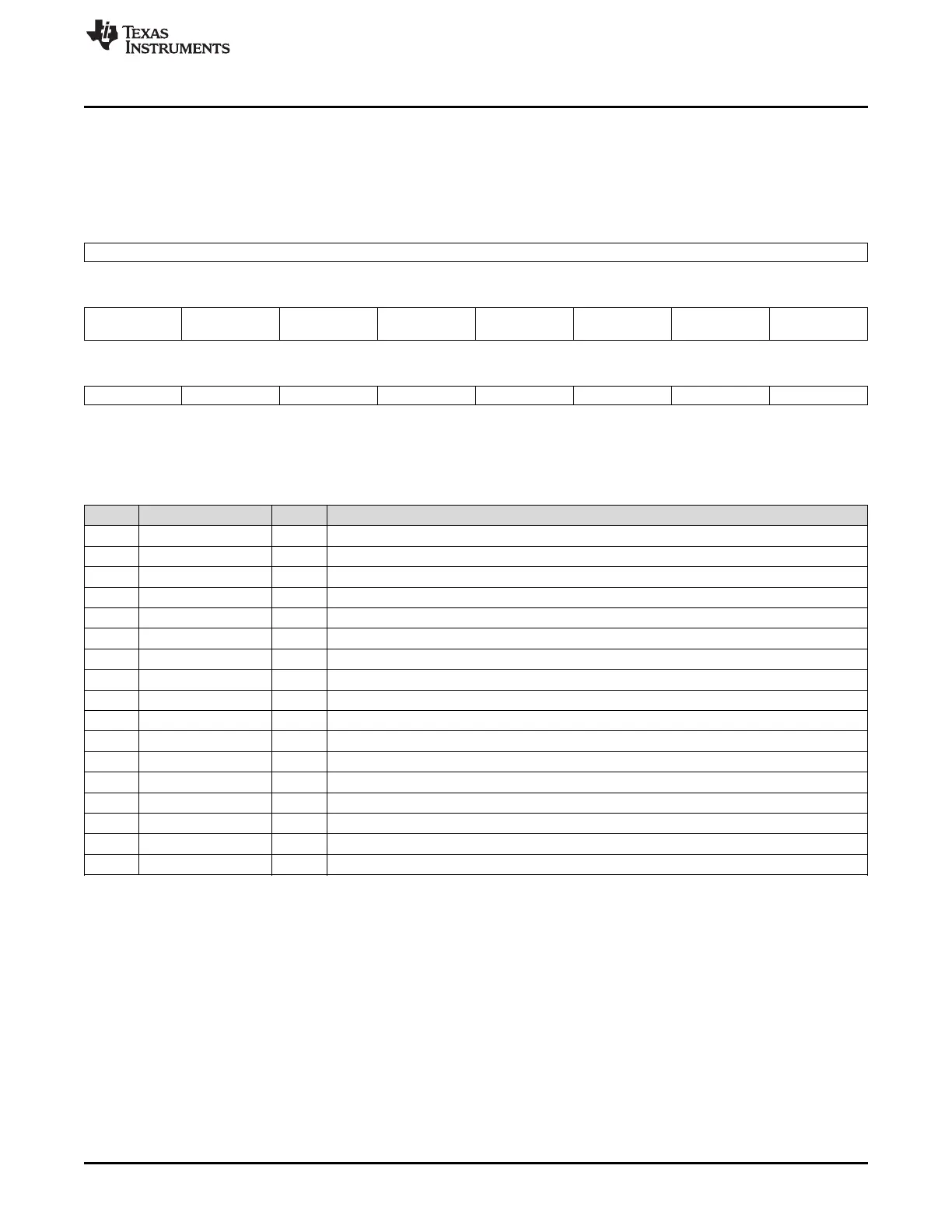

Table 32-53. Receive Interrupt Status (Masked) Register (RXINTSTATMASKED) Field Descriptions

Bit Field Value Description

31-16 Reserved 0 Reserved

15 RX7THRESHPEND 0-1 RX7THRESHPEND masked interrupt read.

14 RX6THRESHPEND 0-1 RX6THRESHPEND masked interrupt read.

13 RX5THRESHPEND 0-1 RX5THRESHPEND masked interrupt read.

12 RX4THRESHPEND 0-1 RX4THRESHPEND masked interrupt read.

11 RX3THRESHPEND 0-1 RX3THRESHPEND masked interrupt read.

10 RX2THRESHPEND 0-1 RX2THRESHPEND masked interrupt read.

9 RX1THRESHPEND 0-1 RX1THRESHPEND masked interrupt read.

8 RX0THRESHPEND 0-1 RX0THRESHPEND masked interrupt read.

7 RX7PEND 0-1 RX7PEND masked interrupt read.

6 RX6PEND 0-1 RX6PEND masked interrupt read.

5 RX5PEND 0-1 RX5PEND masked interrupt read.

4 RX4PEND 0-1 RX4PEND masked interrupt read.

3 RX3PEND 0-1 RX3PEND masked interrupt read.

2 RX2PEND 0-1 RX2PEND masked interrupt read.

1 RX1PEND 0-1 RX1PEND masked interrupt read.

0 RX0PEND 0-1 RX0PEND masked interrupt read.

Loading...

Loading...