www.ti.com

System and Peripheral Control Registers

197

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Architecture

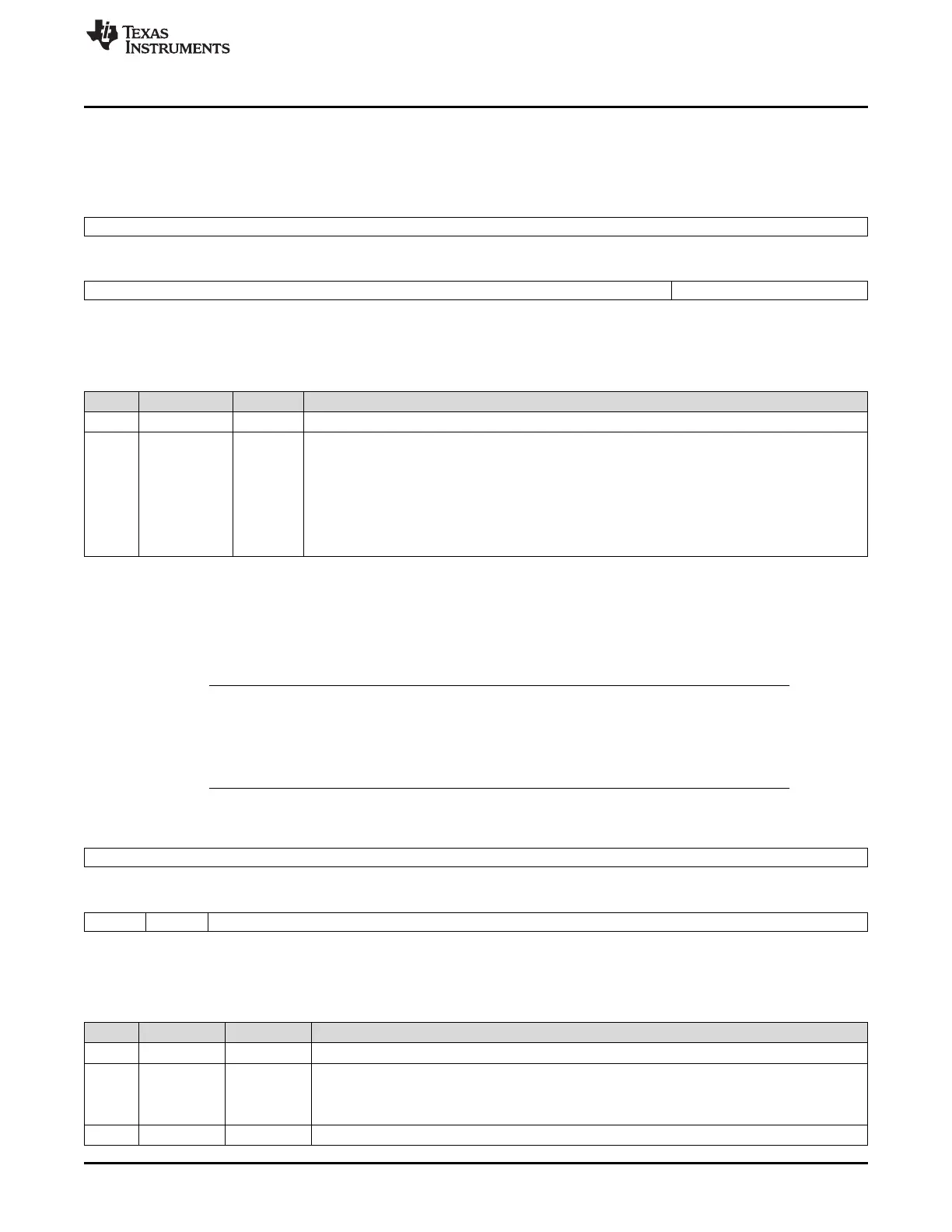

2.5.1.44 DEV Parity Control Register 1 (DEVCR1)

This register is shown in Figure 2-51 and described in Table 2-63.

Figure 2-51. DEV Parity Control Register 1 (DEVCR1) (offset = DCh)

31 16

Reserved

R-0

15 4 3 0

Reserved DEVPARSEL

R-0 R/WP-Ah

LEGEND: R/W = Read/Write; R = Read only; WP = Write in privileged mode only; -n = value after reset

Table 2-63. DEV Parity Control Register 1 (DEVCR1) Field Descriptions

Bit Field Value Description

31-4 Reserved 0 Reads return 0. Writes have no effect.

3-0 DEVPARSEL Device parity select bit key.

Note: After an odd (DEVPARSEL = Ah) or even (DEVPARSEL = 5h) scheme is programmed

into the DEVPARSEL register, any one bit change can be detected and will retain its

programmed scheme. More than one bit changes in DEVPARSEL will cause a default to odd

parity scheme.

5h The device parity is even.

Ah The device parity is odd.

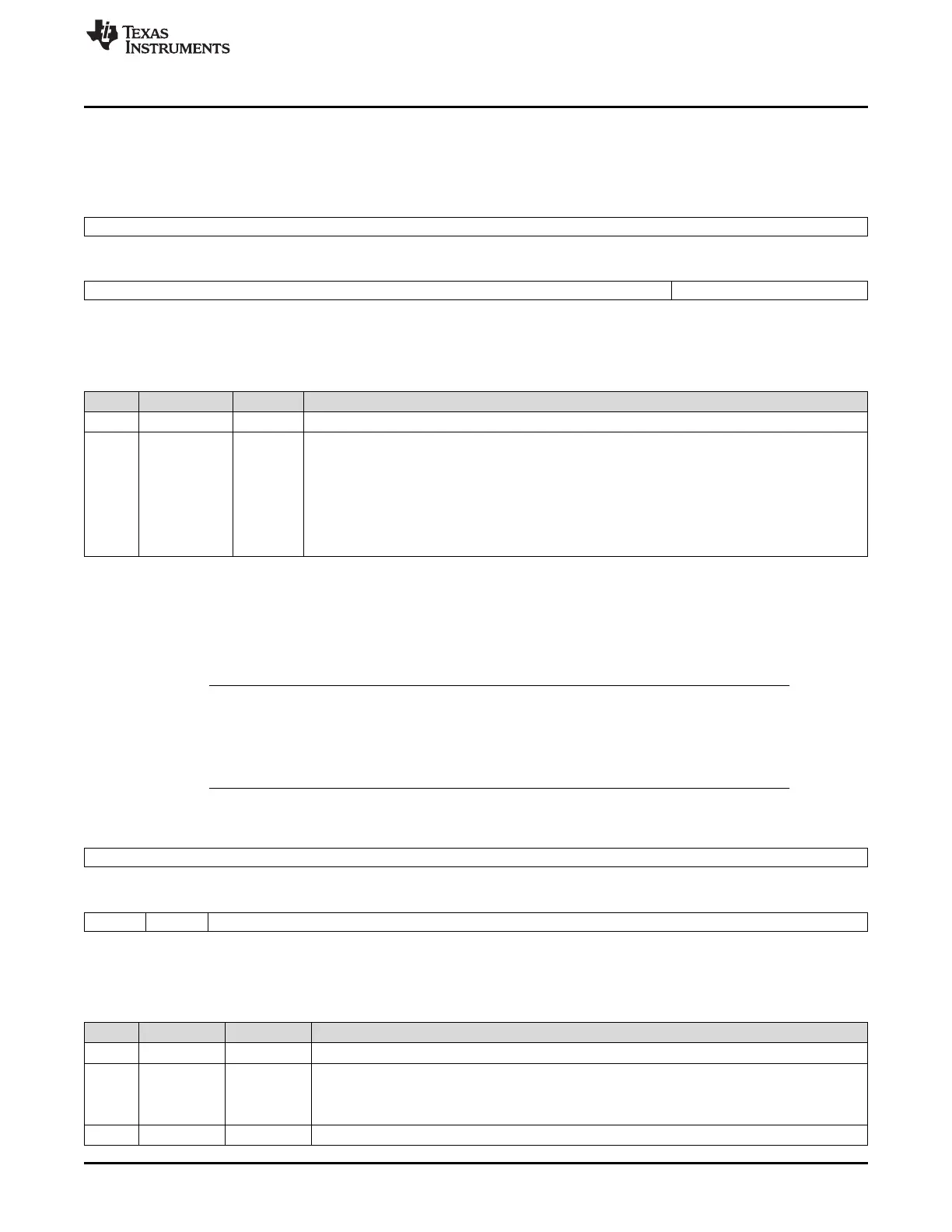

2.5.1.45 System Exception Control Register (SYSECR)

The SYSECR register, shown in Figure 2-52 and described in Table 2-64, is used to generate a software

reset.

NOTE: The register bits in SYSECR are designated as high-integrity bits and have been

implemented with error-correcting logic such that each bit, although read and written as a

single bit, is actually a multi-bit key with error correction capability. As such, single-bit flips

within the “key” can be corrected allowing protection of the system as a whole. An error

detected is signaled to the ESM module.

Figure 2-52. System Exception Control Register (SYSECR) (offset = E0h)

31 16

Reserved

R-0

15 14 13 0

RESET1 RESET0 Reserved

R/WP-0 R/WP-1 R-0

LEGEND: R/W = Read/Write; R = Read only; WP = Write in privileged mode only; -n = value after reset

Table 2-64. System Exception Control Register (SYSECR) Field Descriptions

Bit Field Value Description

31-16 Reserved 0 Reads return 0. Writes have no effect.

15-14 RESET[1-0] Software reset bits. Setting RESET1 or clearing RESET0 causes a system software reset.

1h No reset will occur.

0, 2h-3h A global system reset will occur.

13-0 Reserved 0 Reads return 0. Writes have no effect.

Loading...

Loading...