www.ti.com

System and Peripheral Control Registers

203

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Architecture

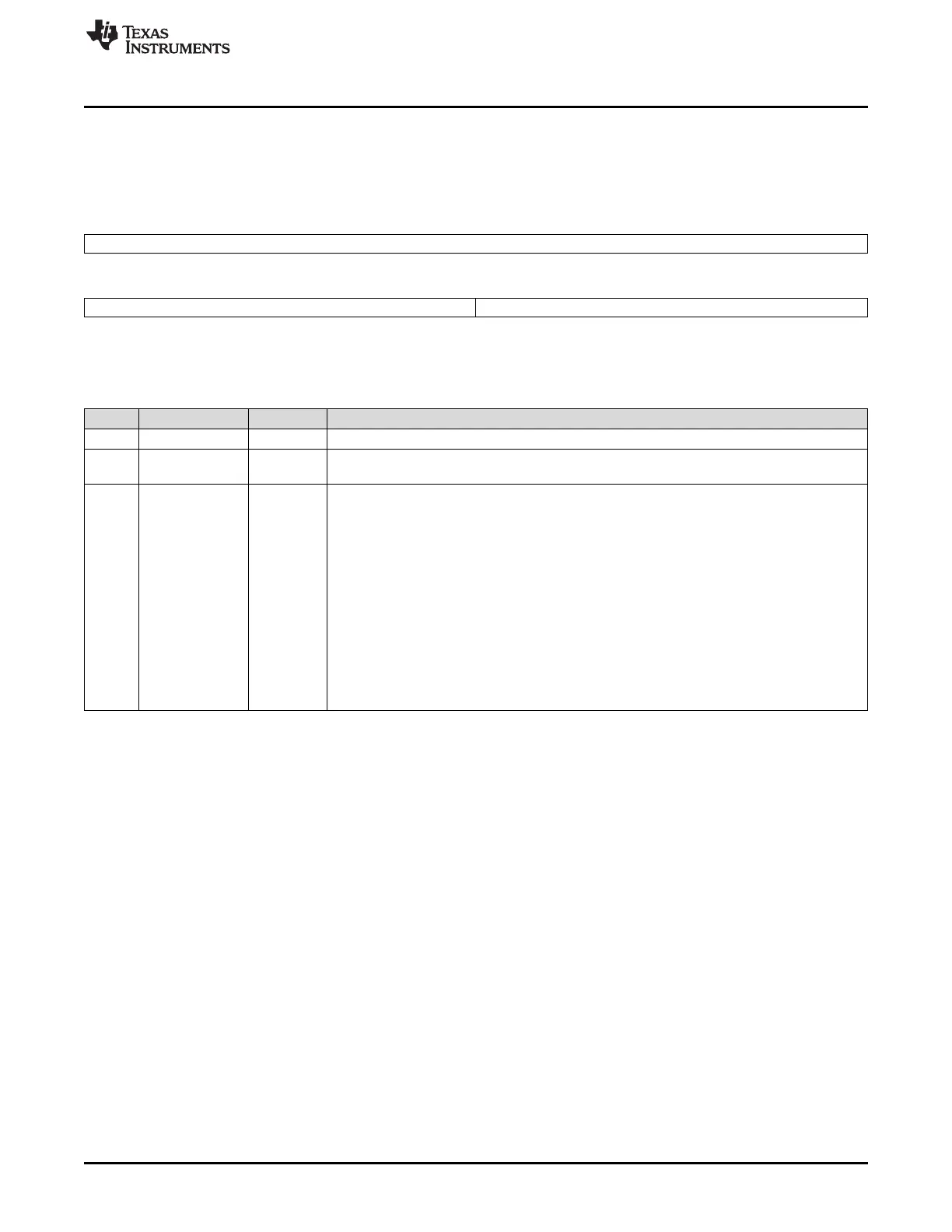

2.5.1.50 Software Interrupt Vector Register (SSIVEC)

The SSIVEC register, shown in Figure 2-57 and described in Table 2-69, contains information about

software interrupts.

Figure 2-57. Software Interrupt Vector Register (SSIVEC) (offset = F4h)

31 16

Reserved

R-0

15 8 7 0

SSIDATA SSIVECT

R-0 R-0

LEGEND: R = Read only; -n = value after reset

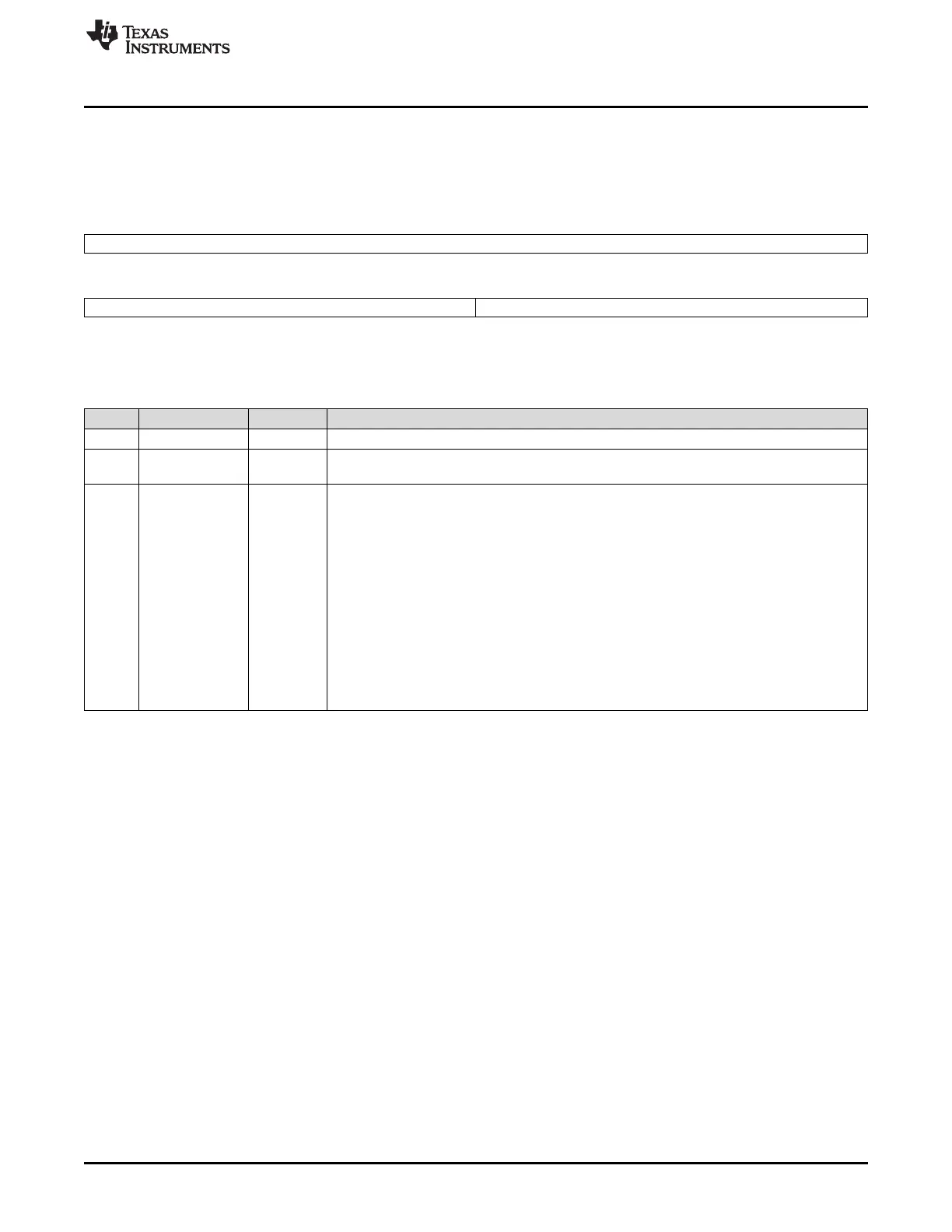

Table 2-69. Software Interrupt Vector Register (SSIVEC) Field Descriptions

Bit Field Value Description

31-16 Reserved 0 Reads return 0. Writes have no effect.

15-8 SSIDATA 0-FFh System software interrupt data key. These bits contain the data key value of the source for the

system software interrupt, which is indicated by the vector in the SSIVEC[7-0] field.

7-0 SSIVECT These bits contain the source for the system software interrupt.

Note: A read from the SSIVECT bits clears the corresponding SSI_FLAG[4-1] bit in the

SSIF register, corresponding to the source vector of the system software interrupt.

Note: The SSIR[4-1] interrupt has the following priority order:

SSIR1 has the highest priority.

SSIR4 has the lowest priority.

0 No software interrupt is pending.

1h A software interrupt has been generated by writing the correct key value to The SSIR1 register.

2h A software interrupt has been generated by writing the correct key value to The SSIR2 register.

3h A software interrupt has been generated by writing the correct key value to The SSIR3 register.

4h A software interrupt has been generated by writing the correct key value to The SSIR4 register.

5h-FFh Reserved

Loading...

Loading...