www.ti.com

ePWM Registers

2097

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Enhanced Pulse Width Modulator (ePWM) Module

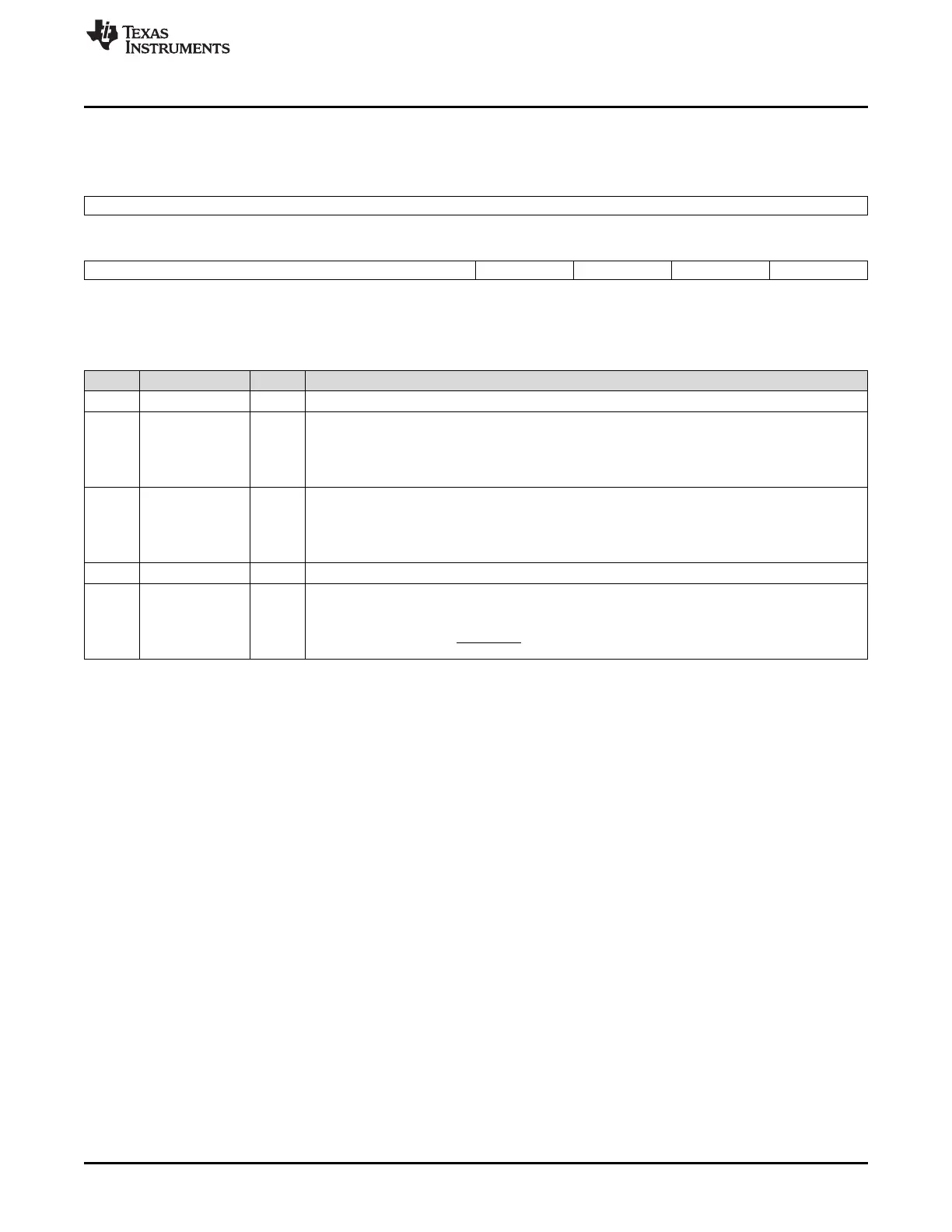

35.4.6.4 Event-Trigger Force Register (ETFRC)

Figure 35-88. Event-Trigger Force Register (ETFRC) [offset = 38h]

15 8

Reserved

R-0

7 4 3 2 1 0

Reserved SOCB SOCA Reserved INT

R-0 R/W-0 R/W-0 R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

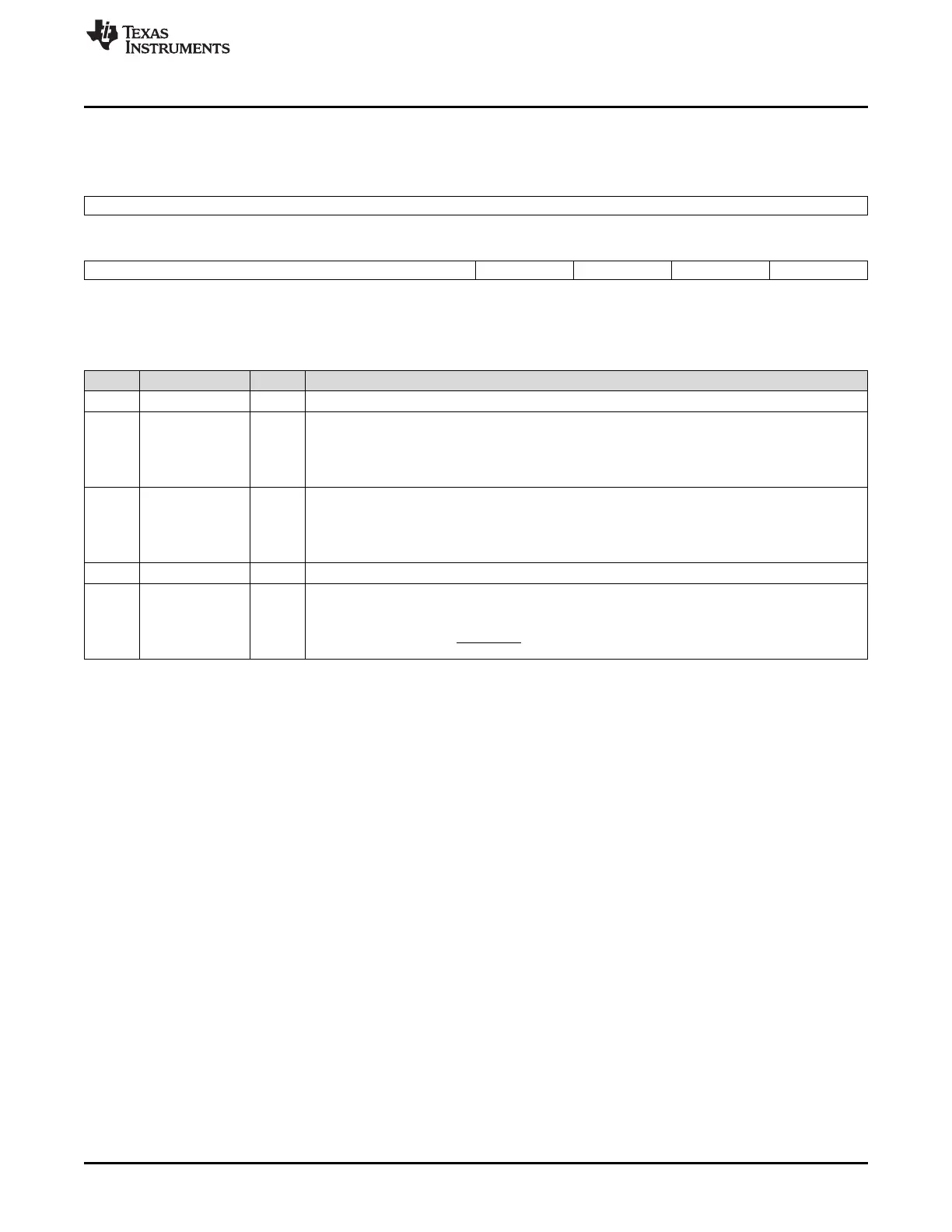

Table 35-48. Event-Trigger Force Register (ETFRC) Field Descriptions

Bits Name Value Description

15-4 Reserved 0 Reserved

3 SOCB SOCB Force Bit. The SOCB pulse will only be generated if the event is enabled in the ETSEL

register. The ETFLG[SOCB] flag bit will be set regardless.

0 Has no effect. Always reads back a 0.

1 Generates a pulse on EPWMxSOCB and sets the SOCBFLG bit. This bit is used for test purposes.

2 SOCA SOCA Force Bit. The SOCA pulse will only be generated if the event is enabled in the ETSEL

register. The ETFLG[SOCA] flag bit will be set regardless.

0 Writing 0 to this bit will be ignored. Always reads back a 0.

1 Generates a pulse on EPWMxSOCA and set the SOCAFLG bit. This bit is used for test purposes.

1 Reserved 0 Reserved

0 INT INT Force Bit. The interrupt will only be generated if the event is enabled in the ETSEL register.

The INT flag bit will be set regardless.

0 Writing 0 to this bit will be ignored. Always reads back a 0.

1 Generates an interrupt on EPWMxINT and set the INT flag bit. This bit is used for test purposes.

Loading...

Loading...