www.ti.com

Control Registers

2125

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Data Modification Module (DMM)

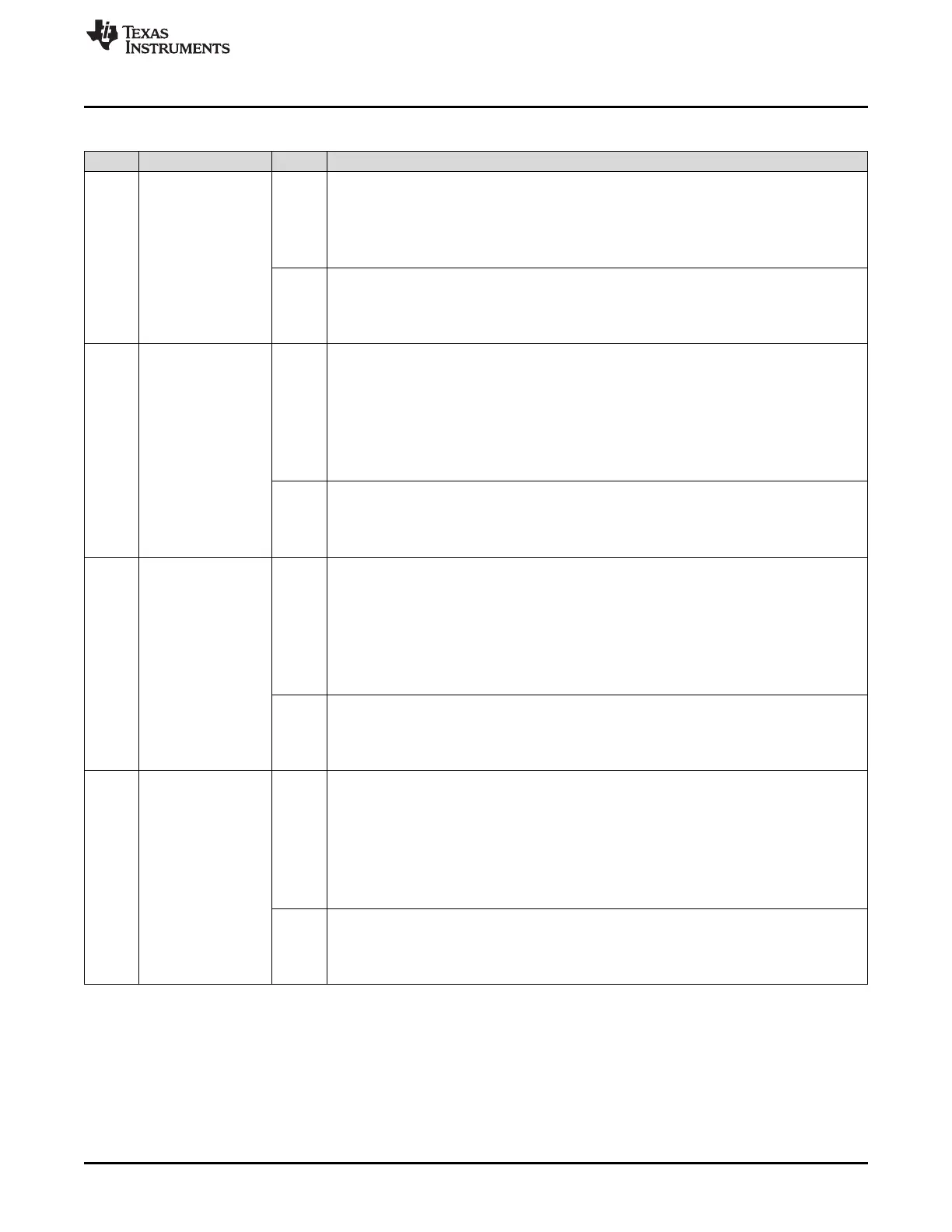

Table 36-9. DMM Interrupt Clear Register (DMMINTCLR) Field Descriptions (continued)

Bit Field Value Description

5 SRC_OVF Source Overflow. This disables an interrupt if the external system experienced and overflow

which was signaled in the Trace Mode packet.

User and privilege mode (read):

0 No interrupt will be generated.

1 An interrupt will be generated.

Privilege mode (write):

0 No influence on bit.

1 Disable interrupt (clears corresponding bit in DMMINTCLR; DMM Interrupt Level Register

(DMMINTLVL)).

4 DEST3_ERR Destination 3 Error.This disables the interrupt generation in case data should be written into a

address not specified by DMMDEST3REG1/DMMDEST3BL1 or

DMMDEST3REG2/DMMDEST3BL2. If both blocksizes are programmed to 0 or a reserved

value, the interrupt will still be generated, the write to the internal RAM however will not take

place.

User and privilege mode (read):

0 No interrupt will be generated.

1 An interrupt will be generated.

Privilege mode (write):

0 No influence on bit.

1 Disable interrupt (clears corresponding bit in DMMINTCLR; DMM Interrupt Level Register

(DMMINTLVL)).

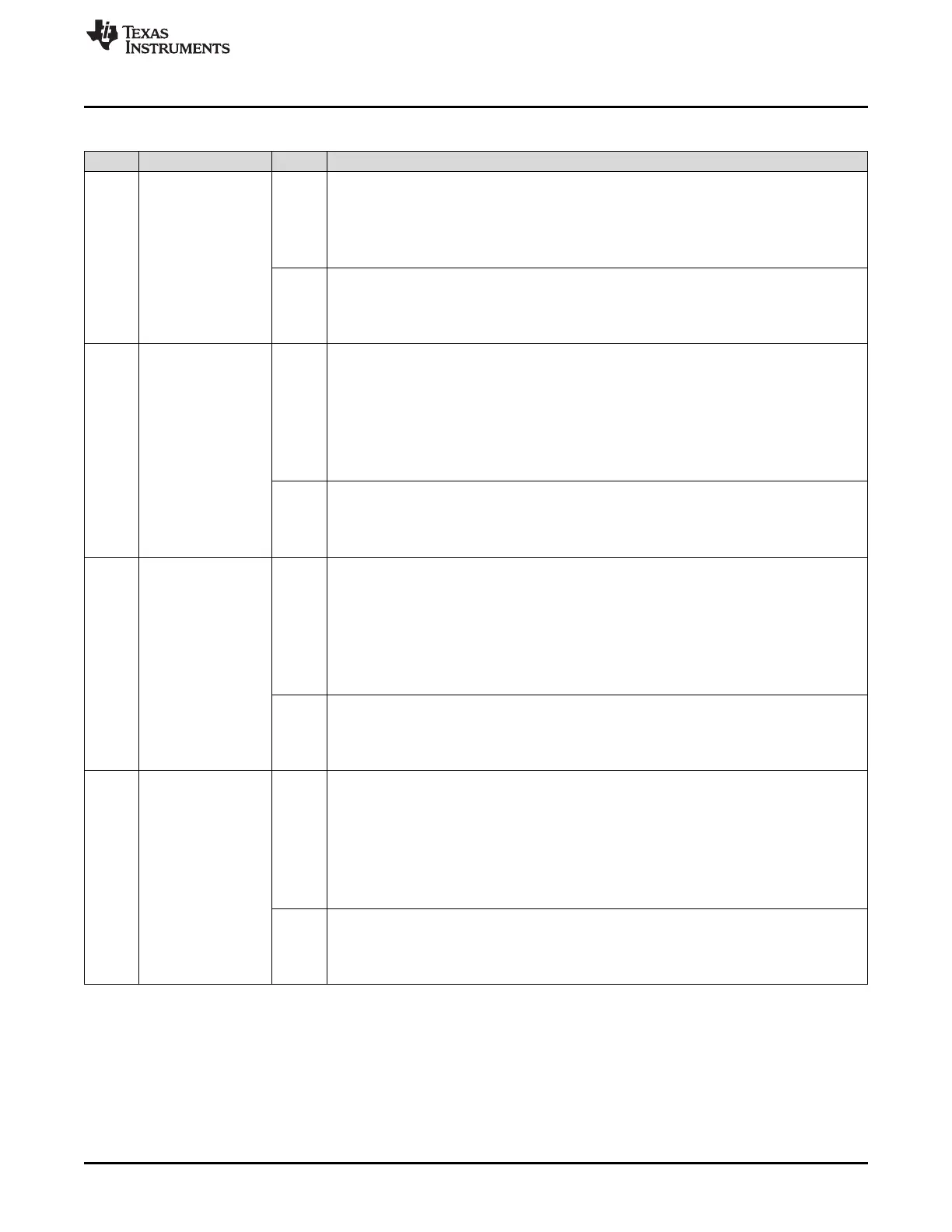

3 DEST2_ERR Destination 2 Error Interrupt Set.This disables the interrupt generation in case data should be

written into a address not specified by DMMDEST2REG1/DMMDEST2BL1 or

DMMDEST2REG2/DMMDEST2BL2. If both blocksizes are programmed to 0 or a reserved

value, the interrupt will still be generated, the write to the internal RAM however will not take

place.

User and privilege mode (read):

0 No interrupt will be generated.

1 An interrupt will be generated.

Privilege mode (write):

0 No influence on bit.

1 Disable interrupt (clears corresponding bit in DMMINTCLR; DMM Interrupt Level Register

(DMMINTLVL)).

2 DEST1_ERR Destination 1 Error Interrupt Set.This disables the interrupt generation in case data should be

written into a address not specified by DMMDEST1REG1/DMMDEST1BL1 or

DMMDEST1REG2/DMMDEST1BL2. If both blocksizes are programmed to 0 or a reserved

value, the interrupt will still be generated, the write to the internal RAM however will not take

place.

User and privilege mode (read):

0 No interrupt will be generated.

1 An interrupt will be generated.

Privilege mode (write):

0 No influence on bit.

1 Disable interrupt (clears corresponding bit in DMMINTCLR; DMM Interrupt Level Register

(DMMINTLVL)).

Loading...

Loading...