www.ti.com

eFuse Controller Registers

2193

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

eFuse Controller

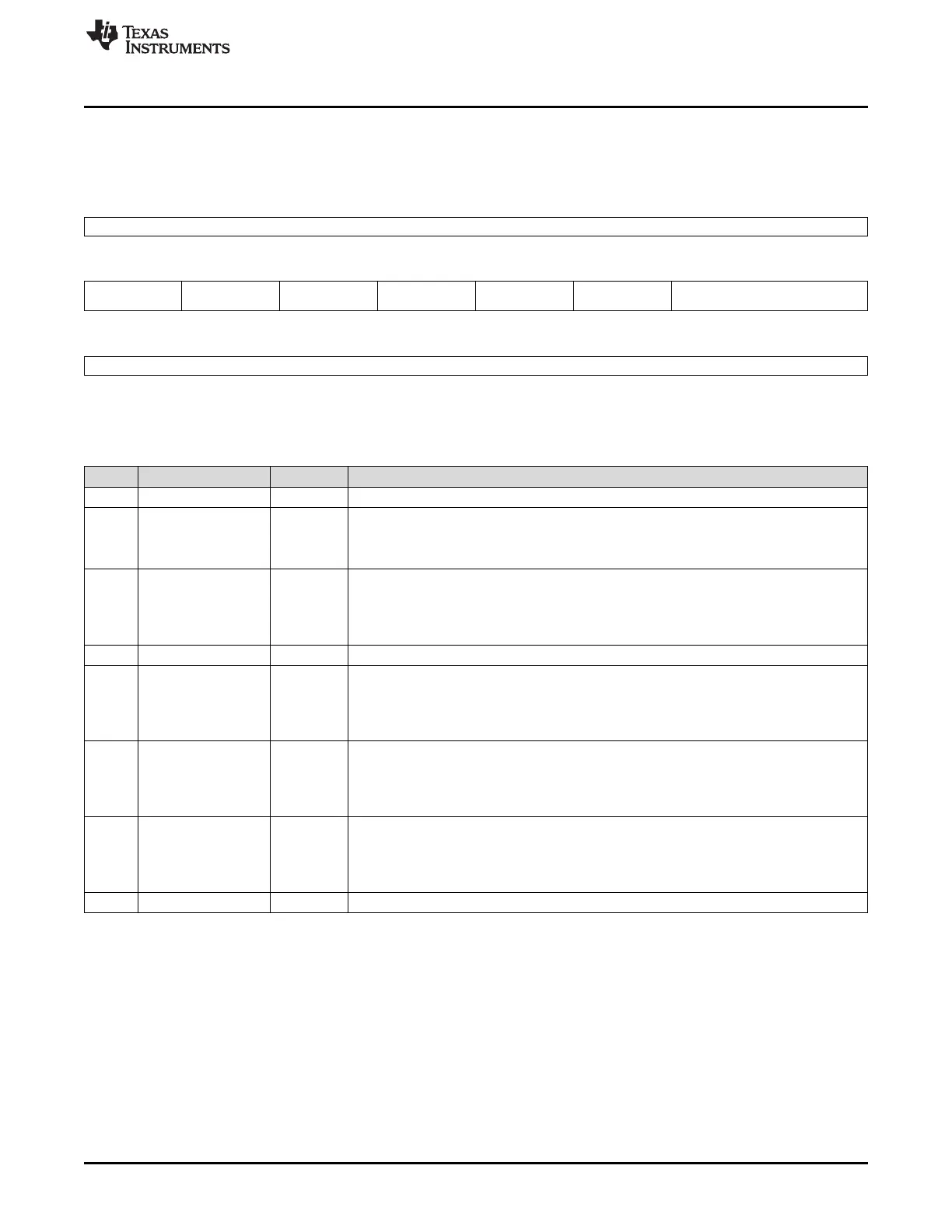

38.4.2 EFC Pins Register (EFCPINS)

Figure 38-3 and Figure 38-3 describe the EFCPINS register.

Figure 38-3. EFC Pins Register (EFCPINS) [offset = 2Ch]

31 16

Reserved

R-0

15 14 13 12 11 10 9 8

EFC Selftest

Done

EFC Selftest

Error

Reserved EFC Single Bit

Error

EFC Instruction

Error

EFC Autoload

Error

Reserved

R-0 R-0 R-0 R-x R-0 R-x R-x

7 0

Reserved

R-x

LEGEND: R = Read only; -n = value after power-on reset (nPORRST); x = Indeterminate

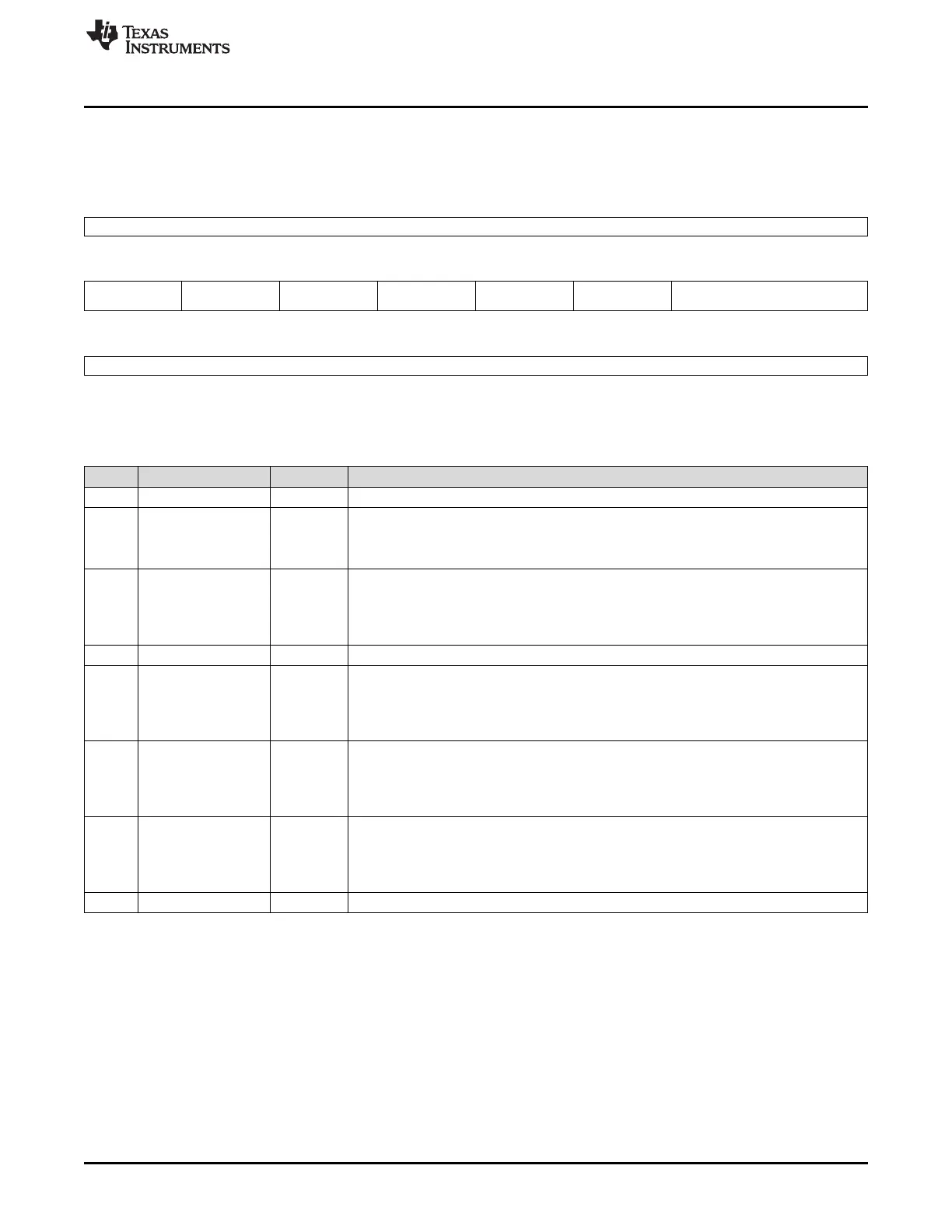

Table 38-4. EFC Pins Register (EFCPINS) Field Descriptions

Bit Name Value Description

31–16 Reserved 0 Reads return zeros, writes have no effect.

15 EFC Selftest Done This bit can be polled to determine when the EFC ECC selftest is complete

0 EFC ECC selftest is not complete.

1 EFC ECC selftest is complete.

14 EFC Selftest Error This bit indicates the pass/fail status of the EFC ECC Selftest once the EFC Selftest Done

bit (bit 15) is set.

0 EFC ECC Selftest passed.

1 EFC ECC Selftest failed.

13 Reserved 0 Reads return zeros. Do NOT write a 1 to this bit.

12 EFC Single Bit Error This bit indicates if a single bit error was corrected by the ECC logic during the autoload

after reset.

0 No single bit error was detected.

1 A single bit error was detected and corrected.

11 EFC Instruction Error This bit indicates an error occurred during a factory test or program operation. This bit

should not be set from normal use.

0 No instruction error detected.

1 An error occurred during a factory test or program operation.

10 EFC Autoload Error This bit indicates that some non-correctable error occurred during the autoload sequence

after reset. This bit also sets ESM group 3, channel 1.

0 The autoload function completed successfully.

1 There were non-correctable errors during the autoload sequence.

9-0 Reserved 0-1 After reset, these bits are indeterminate and reads return either a 1 or 0.

Loading...

Loading...