eFuse Controller Registers

www.ti.com

2194

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

eFuse Controller

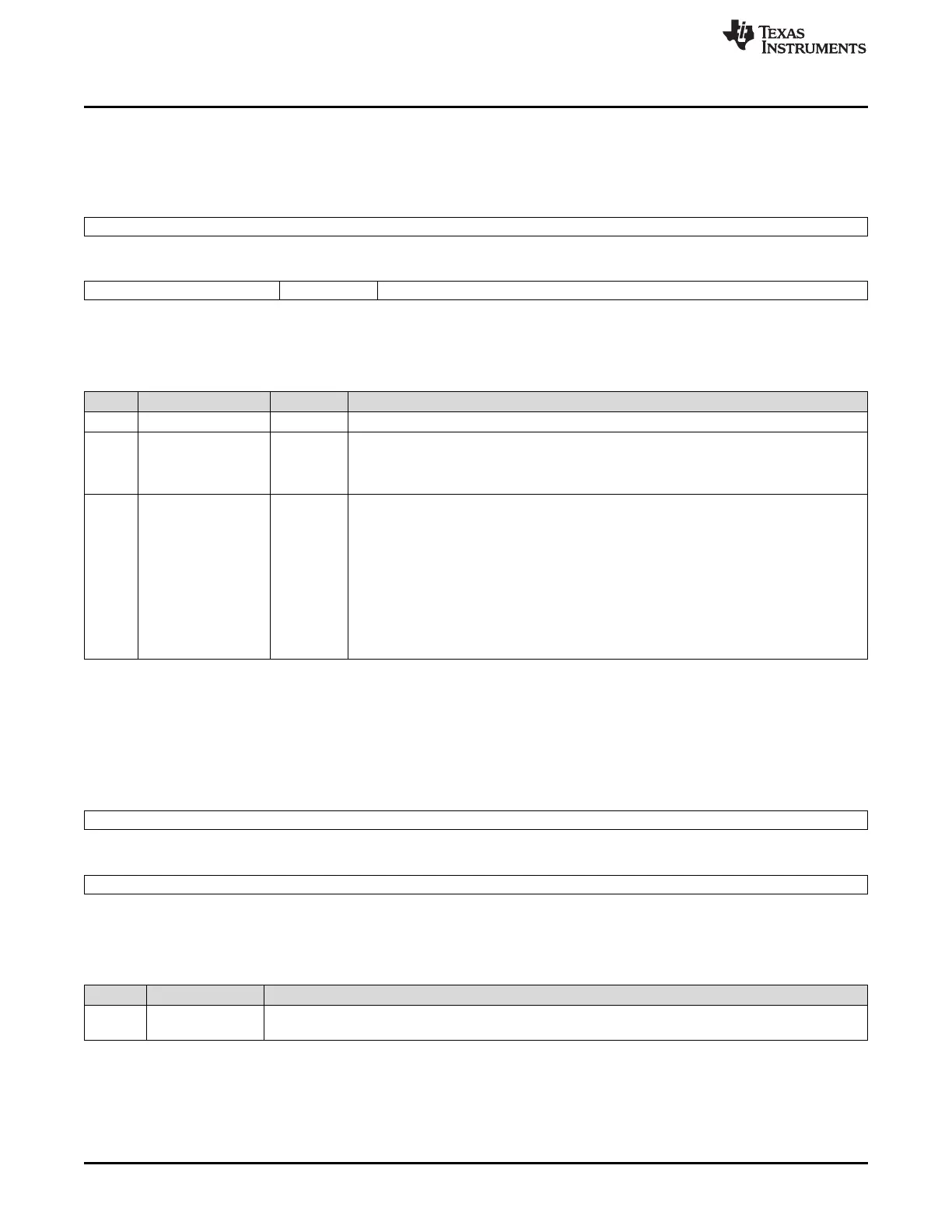

38.4.3 EFC Error Status Register (EFCERRSTAT)

Figure 38-4 and Table 38-5 describe the EFCERRSTAT register.

Figure 38-4. EFC Error Status Register (EFCERRSTAT) [offset = 3Ch]

31 8

Reserved

R-0

7 6 5 4 0

Reserved Instruc Done Error Code

R-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after power-on reset (nPORRST)

Table 38-5. EFC Error Status Register (EFCERRSTAT) Field Descriptions

Bit Name Value Description

31–6 Reserved 0 Reads return zeros, writes have no effect.

5 Instruc Done Instruction done. Used to indicate that the eFuse self test has completed

0 The eFuse controller is still executing.

1 The eFuse controller has completed executing.

4-0 Error Code The error status of the last instruction executed by the eFuse Controller

0 No error.

5h An uncorrectable (multibit) error was detected during the power-on autoload sequence.

15h At least one single bit error was detected and corrected during the power-on autoload

sequence.

18h The signature generated by the ECC self-test logic did not match the golden signature

written in the EFCSTSIG register. The EDAC circuitry might have a fault.

All other

values

All other values are reserved for e-fuse system tests and are not expected to occur in

normal system use.

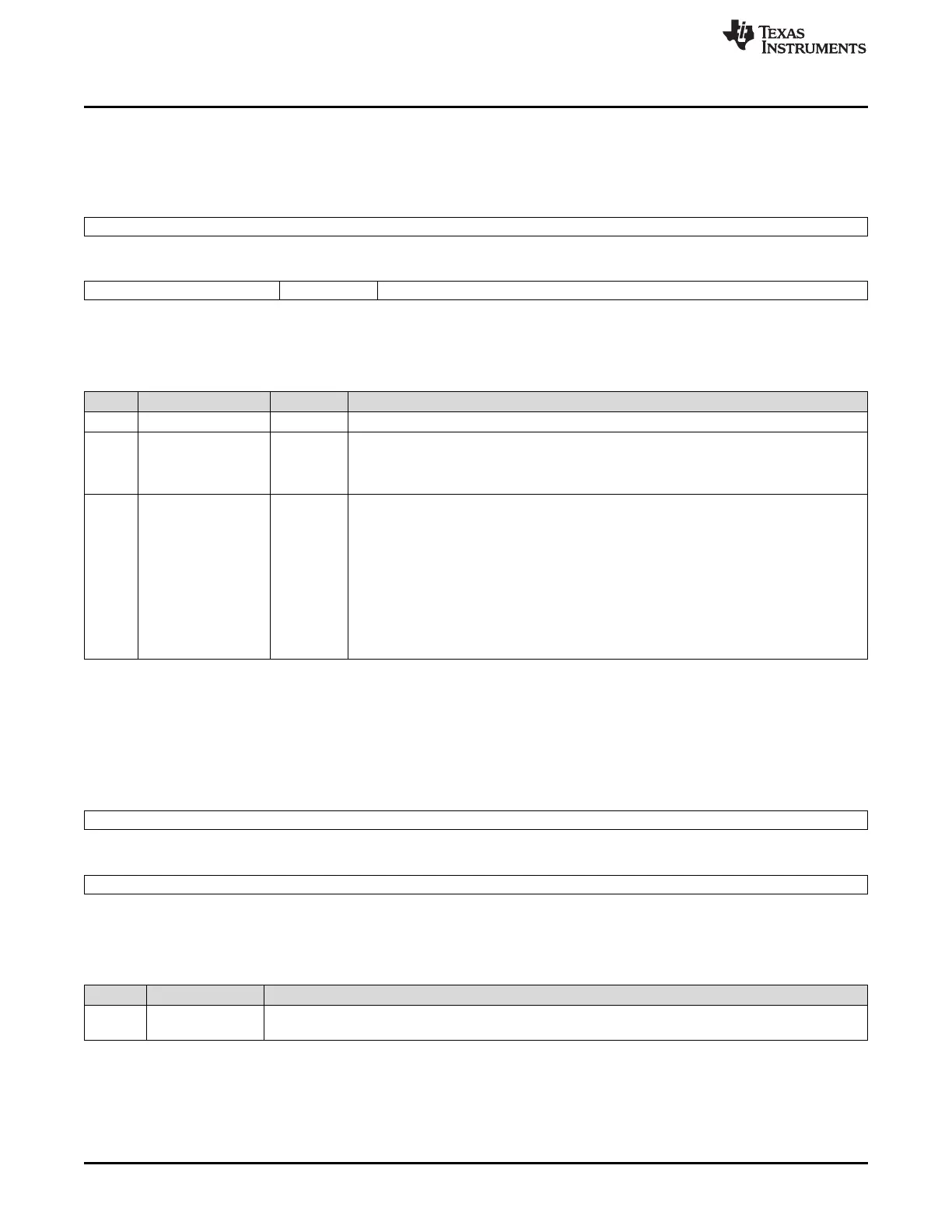

38.4.4 EFC Self Test Cycles Register (EFCSTCY)

Figure 38-5 and Table 38-6 describe the EFCSTCY register.

Figure 38-5. EFC Self Test Cycles Register (EFCSTCY) [offset = 48h]

31 16

Cycles

R/W-0

15 0

Cycles

R/W-0

LEGEND: R/W = Read/Write; -n = value after power-on reset (nPORRST)

Table 38-6. EFC Self Test Cycles Register (EFCSTCY) Field Descriptions

Bit Name Description

31–0 Cycles This register is used to determine the number of cycles to run the eFuse controller ECC logic self test. It is

recommended to use a value of 600 (0x00000258).

Loading...

Loading...