Control of Multiplexed Inputs

www.ti.com

306

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

I/O Multiplexing and Control Module (IOMM)

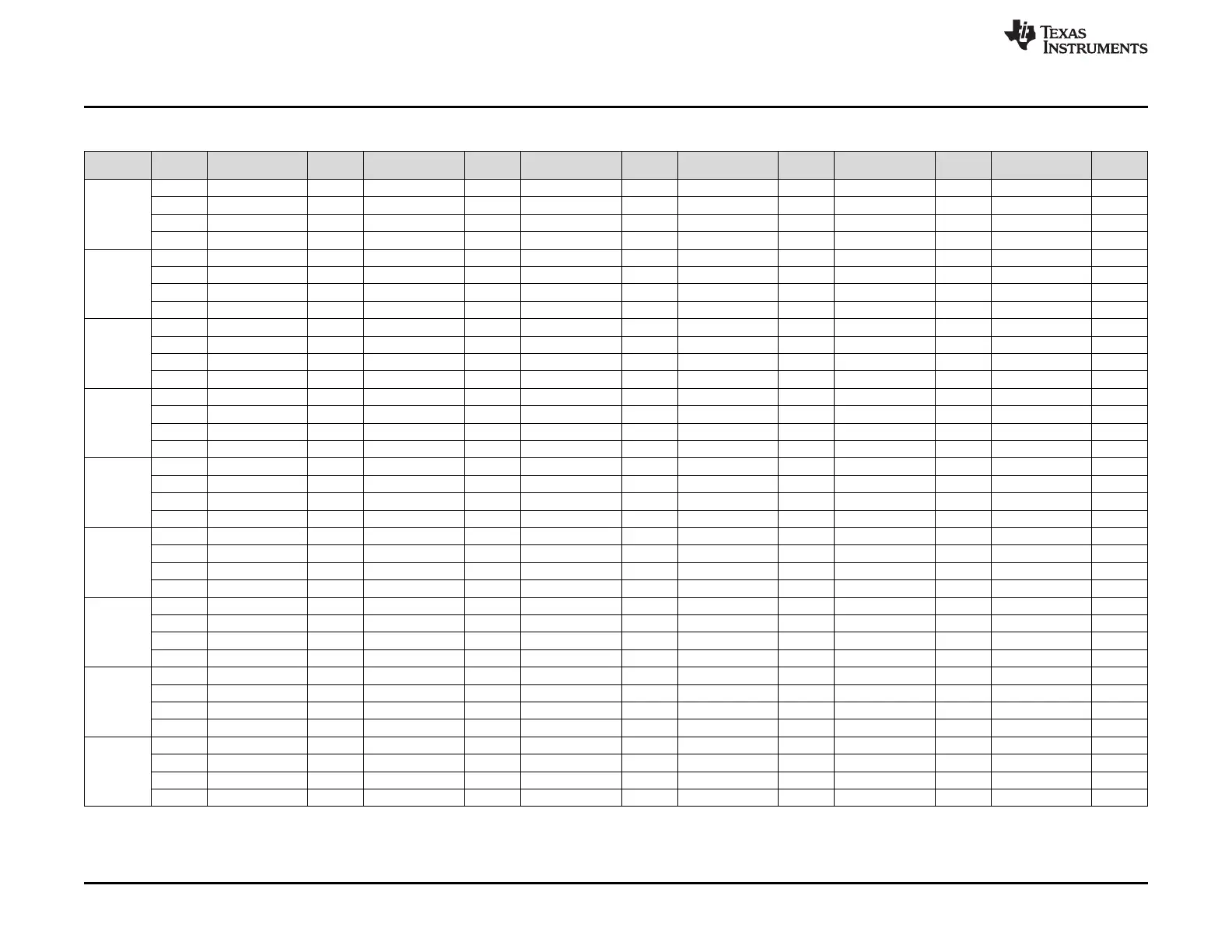

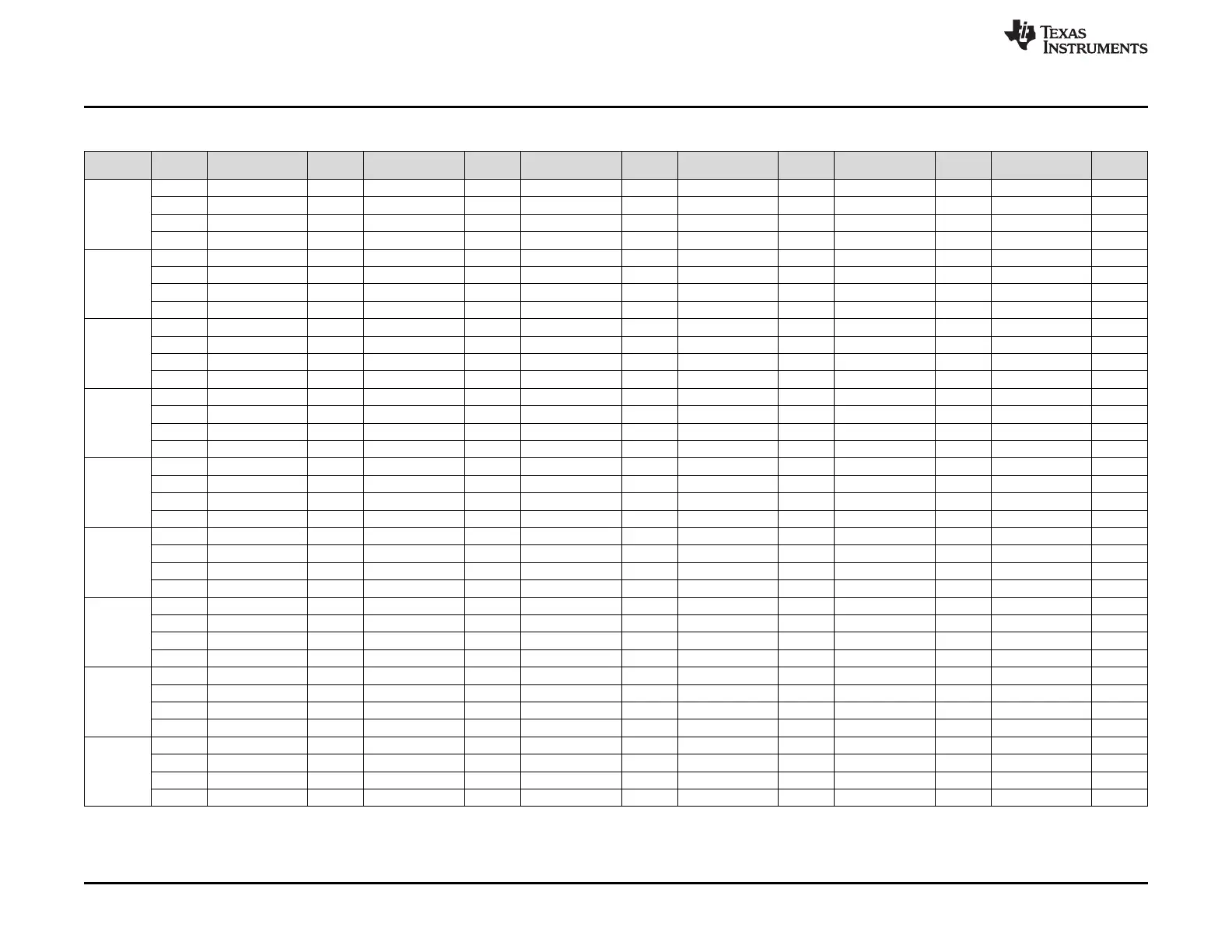

Table 6-1. Multiplexing for Outputs on 337ZWT Package (continued)

Address

Offset

337ZWT

BALL

Default Function Selection

Bit

Alternate Function 1 Selection

Bit

Alternate Function 2 Selection

Bit

Alternate Function 3 Selection

Bit

Alternate Function 4 Selection

Bit

Alternate Function 5 Selection

Bit

168h J3 MIBSPI1NCS[3] 22[0] N2HET1[21] 22[3] nTZ1_3 22[5]

G19 MIBSPI1NENA 22[8] MII_RXD[2] 22[10] N2HET1[23] 22[11] ECAP4 22[13]

V9 MIBSPI3CLK 22[16] EXT_SEL[01] 22[17] eQEP1A 22[21]

V10 MIBSPI3NCS[0] 22[24] AD2EVT 22[25] eQEP1I 22[29]

16Ch V5 MIBSPI3NCS[1] 23[0] MDCLK 23[2] N2HET1[25] 23[3]

B2 MIBSPI3NCS[2] 23[8] I2C1_SDA 23[9] N2HET1[27] 23[11] nTZ1_2 23[13]

C3 MIBSPI3NCS[3] 23[16] I2C1_SCL 23[17] N2HET1[29] 23[19] nTZ1_1 23[21]

W9 MIBSPI3NENA 23[24] MIBSPI3NCS[5] 23[25] N2HET1[31] 23[27] eQEP1B 23[29]

170h W8 MIBSPI3SIMO 24[0] EXT_SEL[00] 24[1] ECAP3 24[5]

V8 MIBSPI3SOMI 24[8] EXT_ENA 24[9] ECAP2 24[13]

H19 MIBSPI5CLK 24[16] DMM_DATA[04] 24[17] MII_TXEN 24[18] RMII_TXEN 24[19]

E19 MIBSPI5NCS[0] 24[24] DMM_DATA[05] 24[25] ePWM4A 24[29]

174h B6 MIBSPI5NCS[1] 25[0] DMM_DATA[06] 25[1]

W6 MIBSPI5NCS[2] 25[8] DMM_DATA[02] 25[9]

T12 MIBSPI5NCS[3] 25[16] DMM_DATA[03] 25[17]

H18 MIBSPI5NENA 25[24] DMM_DATA[07] 25[25] MII_RXD[3] 25[26] ECAP5 25[29]

178h J19 MIBSPI5SIMO[0] 26[0] DMM_DATA[08] 26[1] MII_TXD[1] 26[2] RMII_TXD[1] 26[3]

E16 MIBSPI5SIMO[1] 26[8] DMM_DATA[09] 26[9] EXT_SEL[00] 26[12]

H17 MIBSPI5SIMO[2] 26[16] DMM_DATA[10] 26[17] EXT_SEL[01] 26[20]

G17 MIBSPI5SIMO[3] 26[24] DMM_DATA[11] 26[25] I2C2_SDA 26[26] EXT_SEL[02] 26[28]

17Ch J18 MIBSPI5SOMI[0] 27[0] DMM_DATA[12] 27[1] MII_TXD[0] 27[2] RMII_TXD[0] 27[3]

E17 MIBSPI5SOMI[1] 27[8] DMM_DATA[13] 27[9] EXT_SEL[03] 27[12]

H16 MIBSPI5SOMI[2] 27[16] DMM_DATA[14] 27[17] EXT_SEL[04] 27[20]

G16 MIBSPI5SOMI[3] 27[24] DMM_DATA[15] 27[25] I2C2_SCL 27[26] EXT_ENA 27[28]

180h K18 N2HET1[00] 28[0] MIBSPI4CLK 28[1] ePWM2B 28[5]

V2 N2HET1[01] 28[8] MIBSPI4NENA 28[9] N2HET2[08] 28[11] eQEP2A 28[13]

W5 N2HET1[02] 28[16] MIBSPI4SIMO 28[17] ePWM3A 28[21]

U1 N2HET1[03] 28[24] MIBSPI4NCS[0] 28[25] N2HET2[10] 28[27] eQEP2B 28[29]

184h B12 N2HET1[04] 29[0] MIBSPI4NCS[1] 29[1] ePWM4B 29[5]

V6 N2HET1[05] 29[8] MIBSPI4SOMI 29[9] N2HET2[12] 29[11] ePWM3B 29[13]

W3 N2HET1[06] 29[16] SCI3RX 29[17] ePWM5A 29[21]

T1 N2HET1[07] 29[24] MIBSPI4NCS[2] 29[25] N2HET2[14] 29[27] ePWM7B 29[29]

188h E18 N2HET1[08] 30[0] MIBSPI1SIMO[1] 30[1] MII_TXD[3] 30[2]

V7 N2HET1[09] 30[8] MIBSPI4NCS[3] 30[9] N2HET2[16] 30[11] ePWM7A 30[13]

D19 N2HET1[10] 30[16] MIBSPI4NCS[4] 30[17] MII_TX_CLK 30[18] nTZ1_3 30[21]

E3 N2HET1[11] 30[24] MIBSPI3NCS[4] 30[25] N2HET2[18] 30[27] EPWM1SYNCO 30[29]

Loading...

Loading...