www.ti.com

STC1 Segment 0 (CPU) Test Coverage and Duration

443

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Self-Test Controller (STC) Module

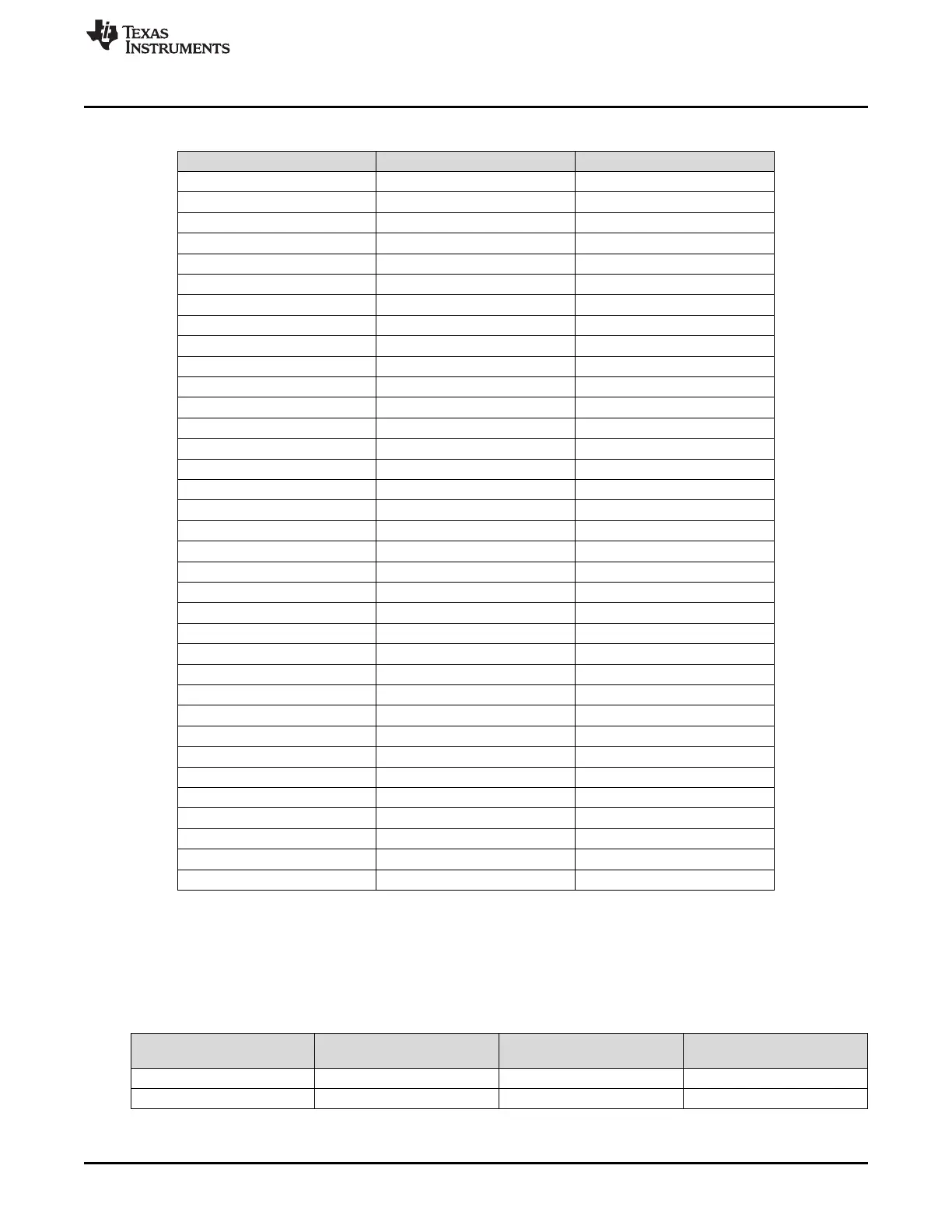

Table 10-2. STC1 Segment 0 Test Coverage and Duration (continued)

Intervals Test Coverage (%) Test Time (Cycles)

91 93.96 148239

92 94.01 149868

93 94.07 151497

94 94.12 153126

95 94.17 154755

96 94.22 156384

97 94.27 158013

98 94.32 159642

99 94.37 161271

100 94.41 162900

101 94.46 164529

102 94.50 166158

103 94.54 167787

104 94.60 169416

105 94.64 171045

106 94.68 172674

107 94.72 174303

108 94.78 175932

109 94.82 177561

110 94.86 179190

111 94.91 180819

112 94.95 182448

113 94.99 184077

114 95.04 185706

115 95.08 187335

116 95.15 188964

117 95.19 190593

118 95.23 192222

119 95.27 193851

120 95.31 195480

121 95.35 197109

122 95.39 198738

123 95.43 200367

124 95.47 201996

125 95.51 203625

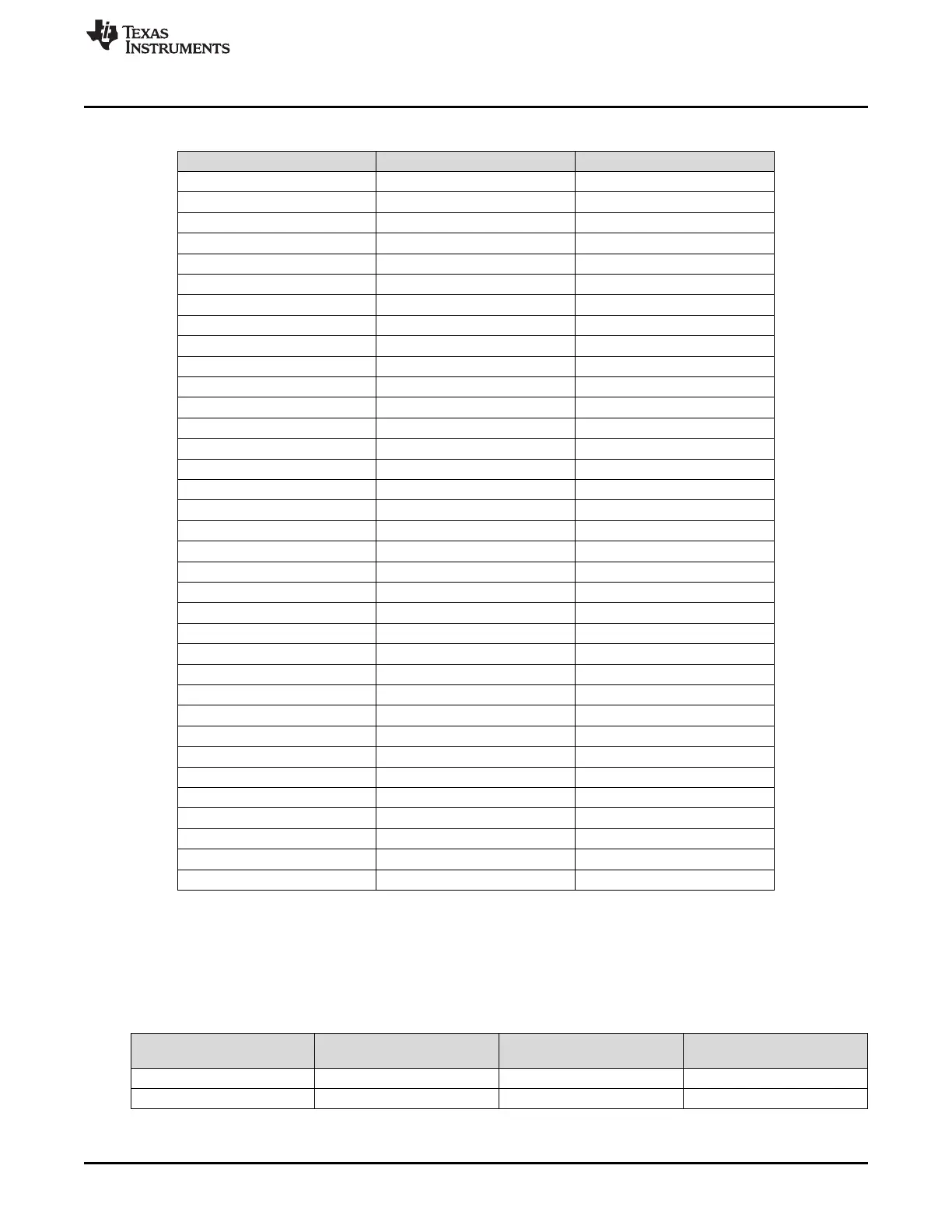

Table 10-3 gives the typical STC execution times for 40 intervals and 125 intervals at different clock rates.

You can choose the number of intervals to be run based on the coverage needed and allowed time for

STC execution.

Table 10-3. Typical Execution Times for STC1 Segment 0

Number of Intervals Coverage

@ GCLK1 = 330 MHz

STCCLK = 110 MHz

@ GCLK1 = 300 MHz

STCCLK = 100 MHz

40 >90% 592.4 µS 651.6 µS

125 >95% 1.8511 mS 2.036 mS

Loading...

Loading...