RTI Control Registers

www.ti.com

622

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Real-Time Interrupt (RTI) Module

17.3.35 RTI Compare Interrupt Clear Enable Register (RTIINTCLRENABLE)

When the RTI compare event is configured to generate a DMA request or triggers (all triggered by RTI

compare interrupt request flag) to other peripherals, it is often desirable to clear the RTI compare flag

automatically so that the requests can be generated repeatedly without any CPU intervention. This

register works with the RTI compare clear registers to enable an "auto-clear" of the compare interrupt

enable bit after a compare equal event. This register is shown in Figure 17-46 and described in Table 17-

37.

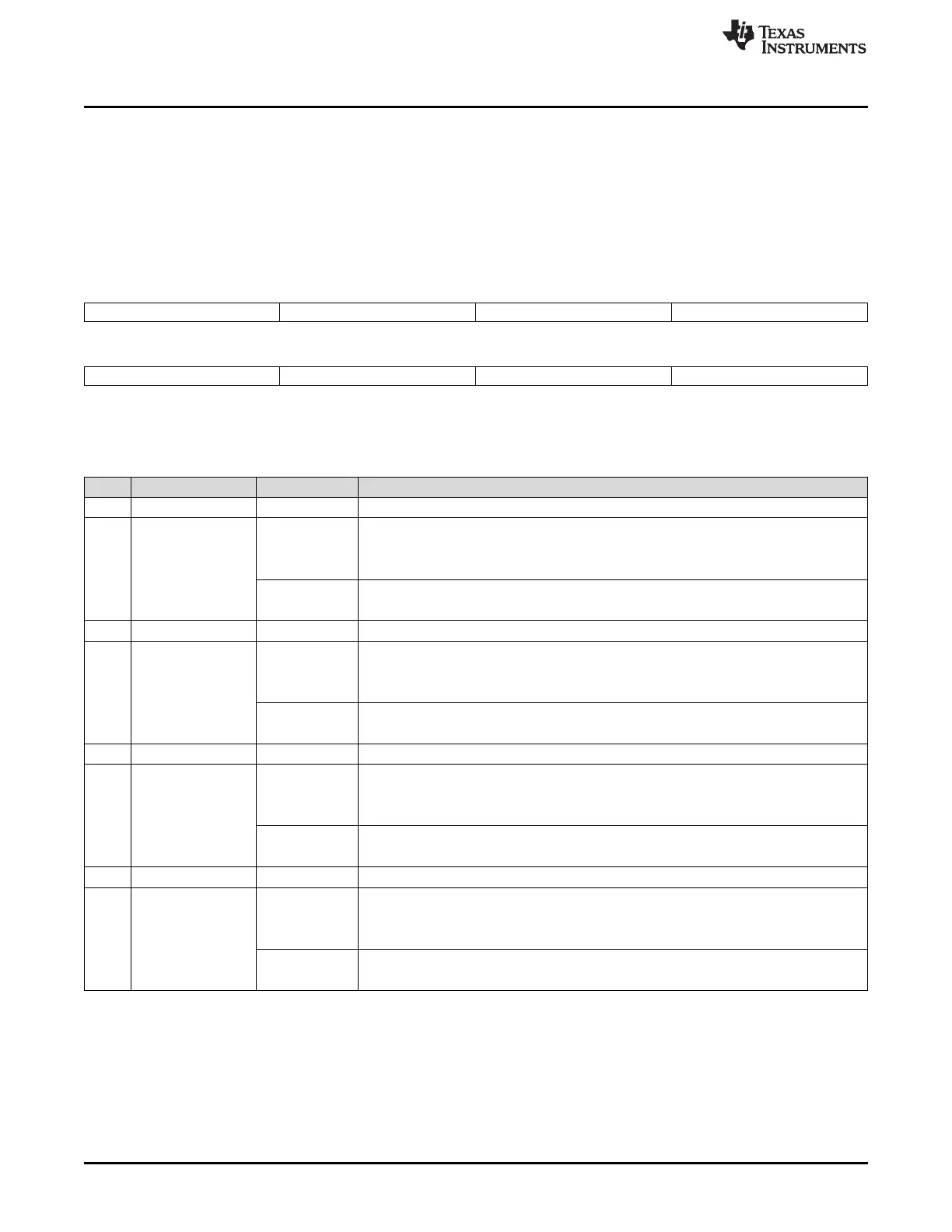

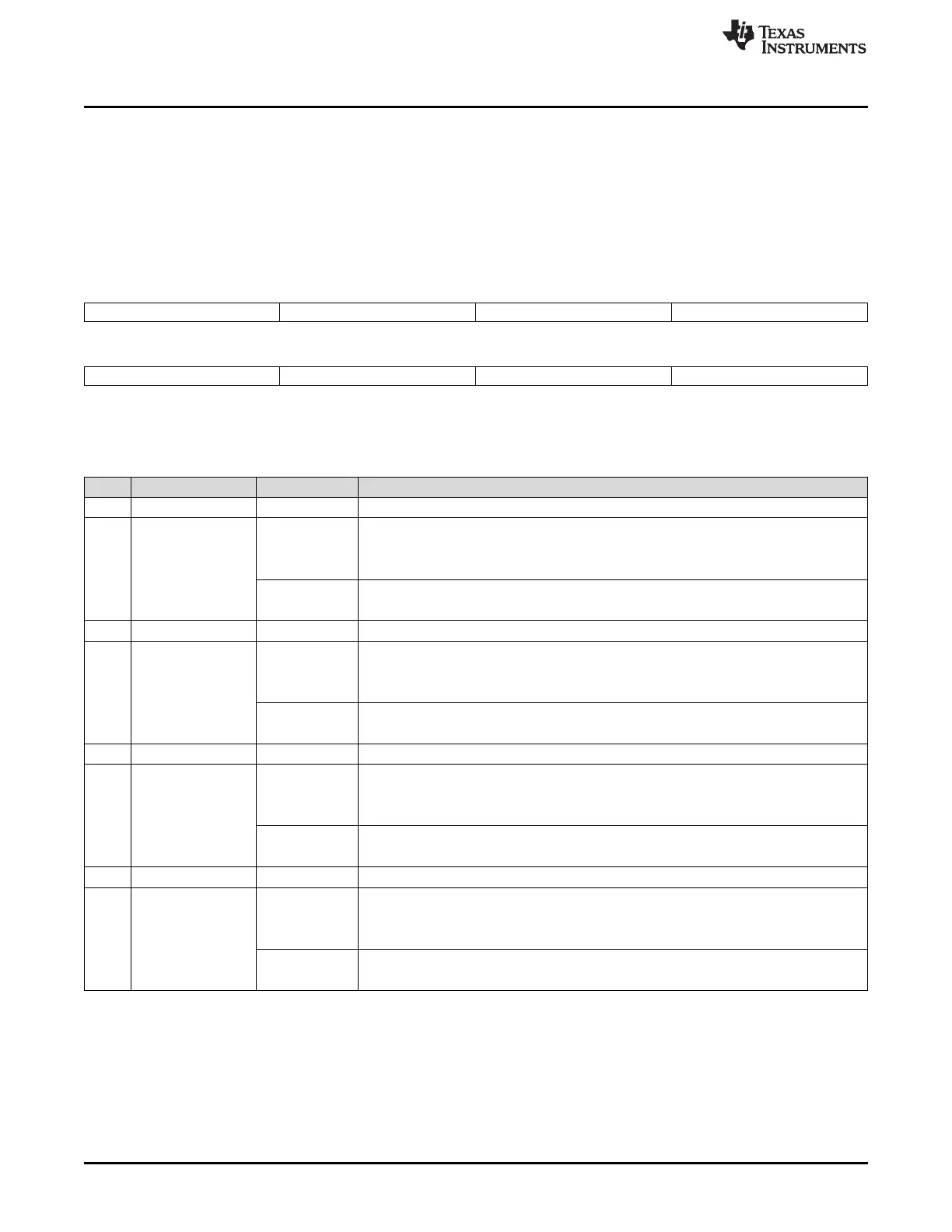

Figure 17-46. RTI Compare Interrupt Clear Enable Register (RTIINTCLRENABLE) [offset = ACh]

31 28 27 24 23 20 19 16

Reserved INTCLRENABLE3 Reserved INTCLRENABLE2

R-0 R/WP-5h R-0 R/WP-5h

15 12 11 8 7 4 3 0

Reserved INTCLRENABLE1 Reserved INTCLRENABLE0

R-0 R/WP-5h R-0 R/WP-5h

LEGEND: R/W = Read/Write; R = Read only; WP = Write in privileged mode only; -n = value after reset

Table 17-37. RTI Compare Interrupt Clear Enable Register (RTIINTCLRENABLE) Field Descriptions

Bit Field Value Description

31-28 Reserved 0 Reads return 0. Writes have no effect.

27-24 INTCLRENABLE3 Enables the auto-clear functionality on the compare 3 interrupt.

5h Read: Auto-clear for compare 3 interrupt is disabled.

Privileged Write: Auto-clear for compare 3 interrupt becomes disabled.

All other values Read: Auto-clear for compare 3 interrupt is enabled.

Privileged Write: Auto-clear for compare 3 interrupt becomes enabled.

23-20 Reserved 0 Reads return 0. Writes have no effect.

19-16 INTCLRENABLE2 Enables the auto-clear functionality on the compare 2 interrupt.

5h Read: Auto-clear for compare 2interrupt is disabled.

Privileged Write: Auto-clear for compare 2 interrupt becomes disabled.

All other values Read: Auto-clear for compare 2 interrupt is enabled.

Privileged Write: Auto-clear for compare 2 interrupt becomes enabled.

15-12 Reserved 0 Reads return 0. Writes have no effect.

11-8 INTCLRENABLE1 Enables the auto-clear functionality on the compare 1 interrupt.

5h Read: Auto-clear for compare 1 interrupt is disabled.

Privileged Write: Auto-clear for compare 1 interrupt becomes disabled.

All other values Read: Auto-clear for compare 1 interrupt is enabled.

Privileged Write: Auto-clear for compare 1 interrupt becomes enabled.

7-4 Reserved 0 Reads return 0. Writes have no effect.

3-0 INTCLRENABLE0 Enables the auto-clear functionality on the compare 0 interrupt.

5h Read: Auto-clear for compare 0 interrupt is disabled.

Privileged Write: Auto-clear for compare 0 interrupt becomes disabled.

All other values Read: Auto-clear for compare 0 interrupt is enabled.

Privileged Write: Auto-clear for compare 0 interrupt becomes enabled.

Loading...

Loading...