Example Configuration

www.ti.com

842

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

External Memory Interface (EMIF)

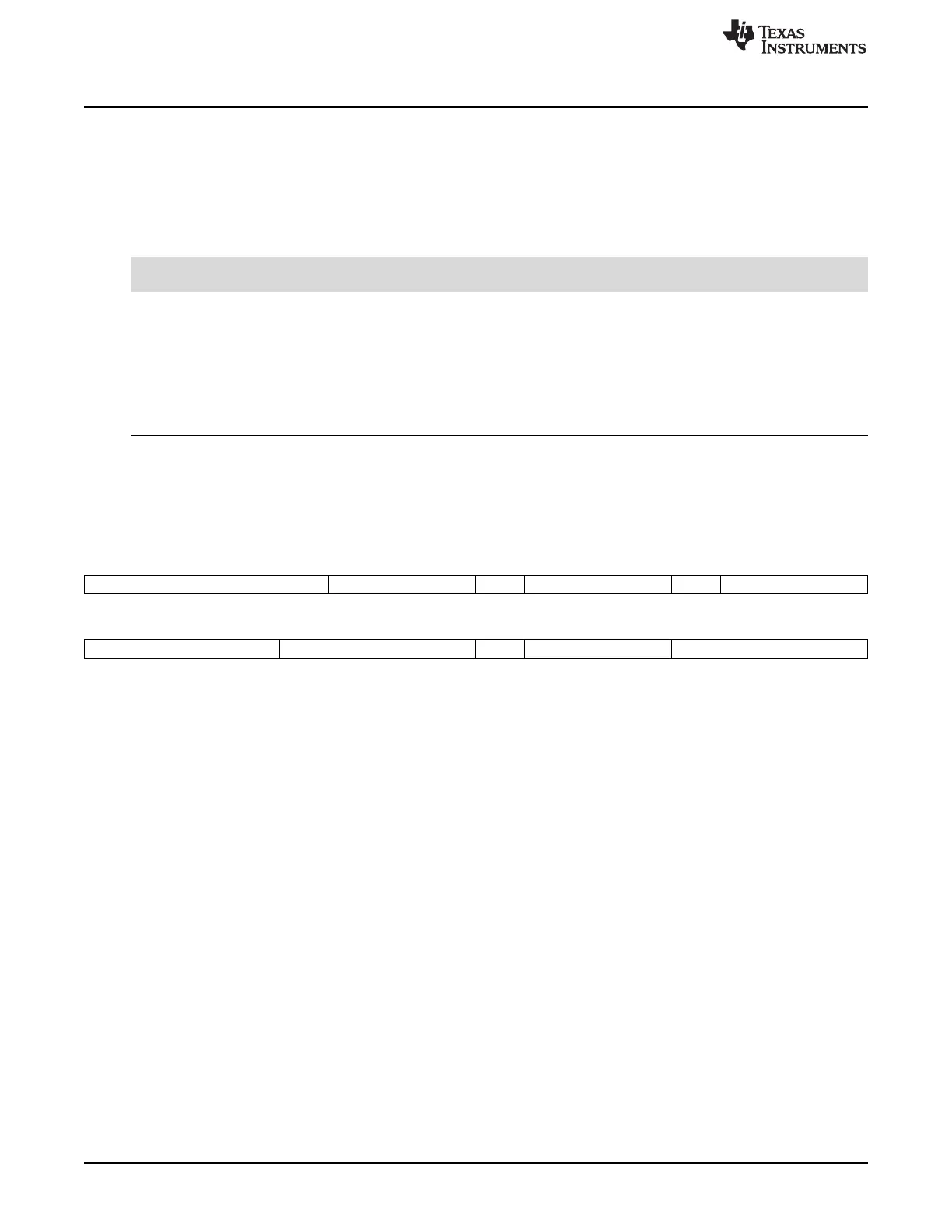

21.4.2.1.2 SDRAM Timing Register (SDTIMR) Settings for the EMIF to K4S641632H-TC(L)70 Interface

The fields of the SDRAM timing register (SDTIMR) should be programmed first as described in Table 21-

38 to satisfy the required timing parameters for the K4S641632H-TC(L)70. Based on these calculations, a

value of 6111 4610h should be written to SDTIMR. Figure 21-28 shows a graphical description of how

SDTIMR should be programmed.

(1)

The Samsung datasheet does not specify a t

RFC

value. Instead, Samsung specifies t

RC

as the minimum auto refresh period.

(2)

The Samsung datasheet does not specify a t

WR

value. Instead, Samsung specifies t

RDL

as last data in to row precharge minimum

delay.

Table 21-38. SDTIMR Field Calculations for the EMIF to K4S641632H-TC(L)70 Interface

Field Name Formula

Value from K4S641632H-TC(L)70

Datasheet

Value Calculated for

Field

T_RFC T_RFC >= (t

RFC

× f

EMIF_CLK

) - 1 t

RC

= 68 ns (min)

(1)

6

T_RP T_RP >= (t

RP

× f

EMIF_CLK

) - 1 t

RP

= 20 ns (min) 1

T_RCD T_RCD >= (t

RCD

× f

EMIF_CLK

) - 1 t

RCD

= 20 ns (min) 1

T_WR T_WR >= (t

WR

× f

EMIF_CLK

) - 1 t

RDL

= 2 CLK = 20 ns (min)

(2)

1

T_RAS T_RAS >= (t

RAS

× f

EMIF_CLK

) - 1 t

RAS

= 49 ns (min) 4

T_RC T_RC >= (t

RC

× f

EMIF_CLK

) - 1 t

RC

= 68 ns (min) 6

T_RRD T_RRD >= (t

RRD

× f

EMIF_CLK

) - 1 t

RRD

= 14 ns (min) 1

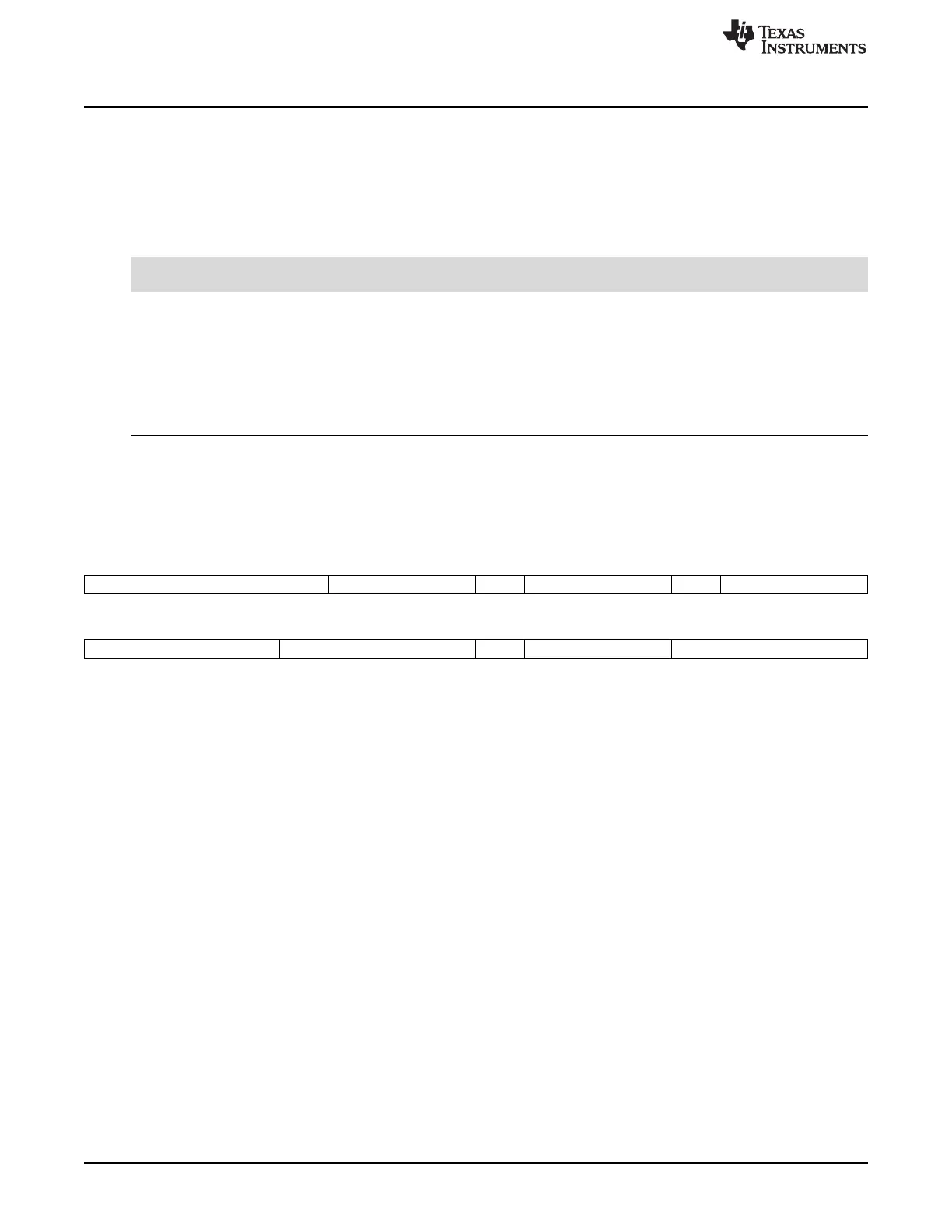

Figure 21-28. SDRAM Timing Register (SDTIMR)

31 27 26 24 23 22 20 19 18 16

0 0110 001 0 001 0 001

T_RFC T_RP Rsvd T_RCD Rsvd T_WR

15 12 11 8 7 6 4 3 0

0100 0110 0 001 0000

T_RAS T_RC Rsvd T_RRD Reserved

Loading...

Loading...