www.ti.com

Example Configuration

843

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

External Memory Interface (EMIF)

21.4.2.1.3 SDRAM Self Refresh Exit Timing Register (SDSRETR) Settings for the EMIF to K4S641632H-

TC(L)70 Interface

The SDRAM self refresh exit timing register (SDSRETR) should be programmed second to satisfy the t

XSR

timing requirement from the K4S641632H-TC(L)70 datasheet. Table 21-39 shows the calculation of the

proper value to program into the T_XS field of this register. Based on this calculation, a value of 6h should

be written to SDSRETR. Figure 21-29 shows how SDSRETR should be programmed.

(1)

The Samsung datasheet does not specify a t

XSR

value. Instead, Samsung specifies t

RC

as the minimum required time after CKE

going high to complete self refresh exit.

Table 21-39. RR Calculation for the EMIF to K4S641632H-TC(L)70 Interface

Field Name Formula

Value from K4S641632H-TC(L)70

Datasheet

Value Calculated for

Field

T_XS T_XS >= (t

XSR

× f

EMIF_CLK

) - 1 t

RC

= 68 ns (min)

(1)

6

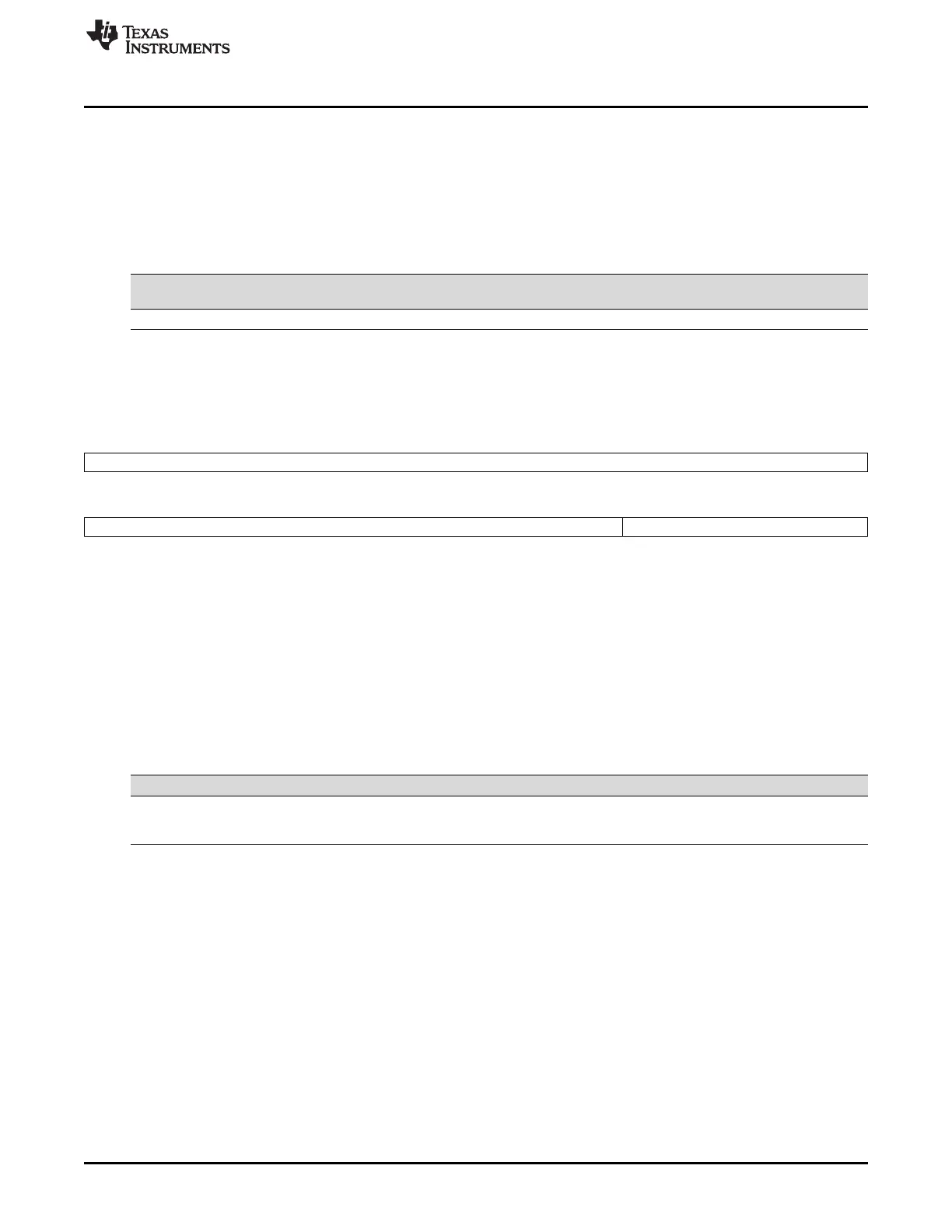

Figure 21-29. SDRAM Self Refresh Exit Timing Register (SDSRETR)

31 16

0000 0000 0000 0000

Reserved

15 5 4 0

000 0000 0000 0 0110

Reserved T_XS

21.4.2.1.4 SDRAM Refresh Control Register (SDRCR) Settings for the EMIF to K4S641632H-TC(L)70

Interface

The SDRAM refresh control register (SDRCR) should next be programmed to satisfy the required refresh

rate of the K4S641632H-TC(L)70. Table 21-40 shows the calculation of the proper value to program into

the RR field of this register. Based on this calculation, a value of 61Ah should be written to SDRCR.

Figure 21-30 shows how SDRCR should be programmed.

Table 21-40. RR Calculation for the EMIF to K4S641632H-TC(L)70 Interface

Field Name Formula Values Value Calculated for Field

RR RR ≤ f

EMIF_CLK

× t

Refresh Period

/ n

cycles

From SDRAM datasheet: t

Refresh Period

= 64 ms; n

cycles

= 4096 EMIF clock

rate: f

EMIF_CLK

= 100 MHz

RR = 1562 cycles = 61Ah cycles

Loading...

Loading...