www.ti.com

ADC Registers

931

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Analog To Digital Converter (ADC) Module

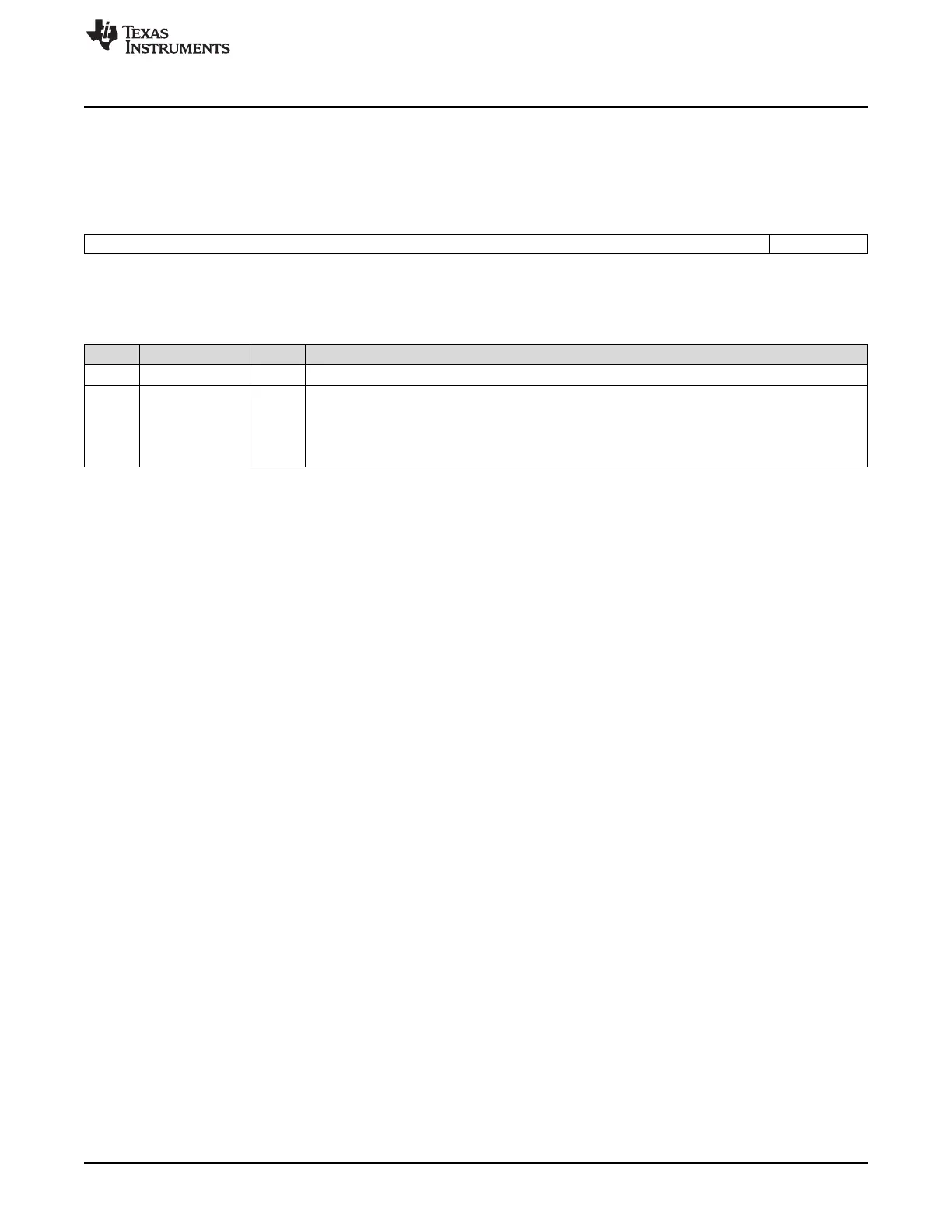

22.3.43 ADC ADEVT Pin Direction Control Register (ADEVTDIR)

ADC ADEVT Pin Direction Control Register (ADEVTDIR) is shown in Figure 22-72 and described in

Table 22-49.

Figure 22-72. ADC ADEVT Pin Direction Control Register (ADEVTDIR) [offset = FCh]

31 1 0

Reserved ADEVT_DIR

R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

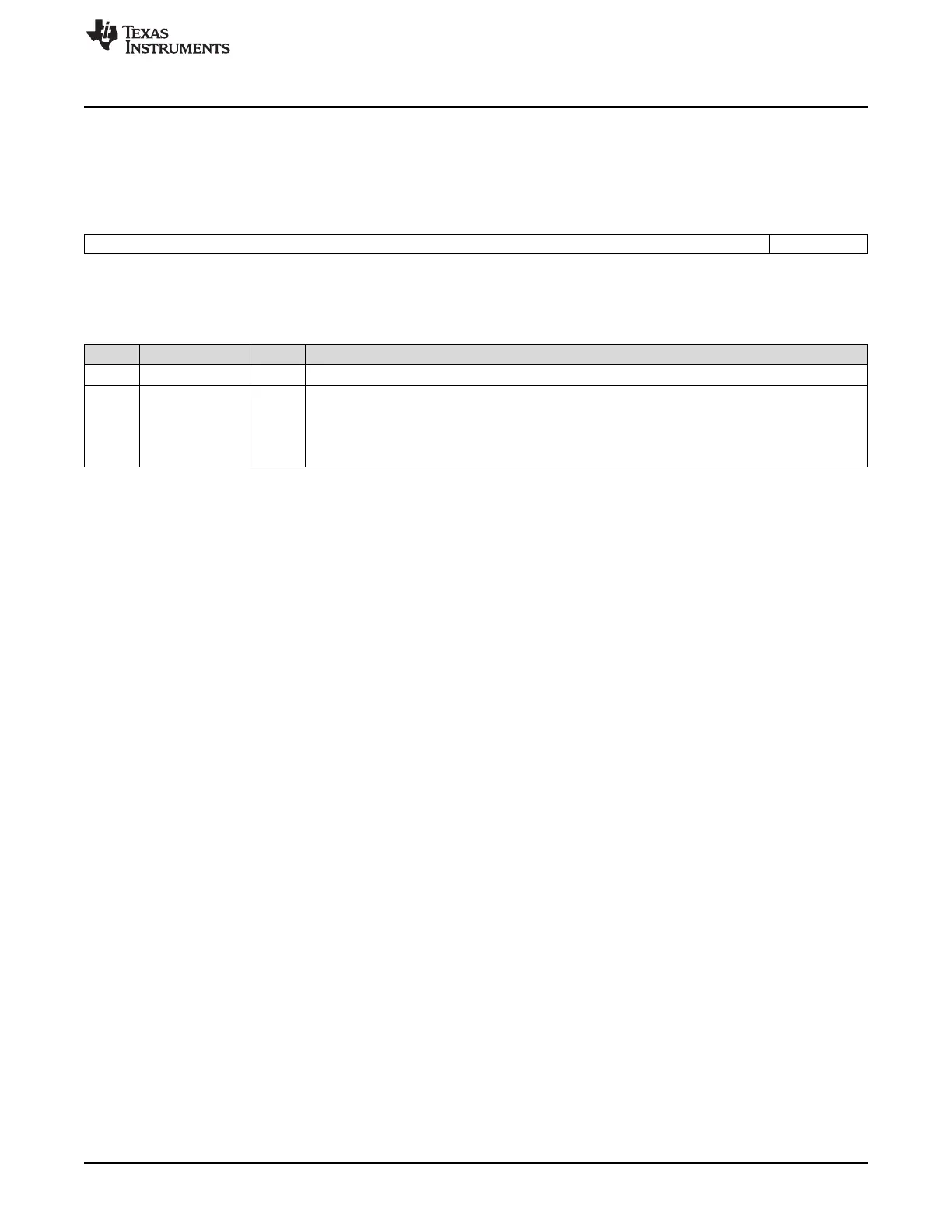

Table 22-49. ADC ADEVT Pin Direction Control Register (ADEVTDIR) Field Descriptions

Bit Field Value Description

31-1 Reserved 0 Reads return 0. Writes have no effect.

0 ADEVT_DIR ADEVT Pin Direction.

Any operating mode read/write:

0 ADEVT is an input pin; the output buffer is disabled.

1 ADEVT is an output pin; the output buffer is enabled.

Loading...

Loading...