FlexRay Module Registers

www.ti.com

1332

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

FlexRay Module

26.3.2.1.4 Single-Bit Error Status Register (SBESTAT)

In normal operation mode, the Single-Bit Error Status Register indicates an ECC single-bit error by setting

the SBE flag. In addition, it holds the faulty message buffer number and the indication of the buffer RAM

when an ECC single-bit error occurred. The register is updated without regard to the single-bit error lock

setting of ECC Control Register (ECC_CTRL).

A flag is cleared by writing a 1 to the corresponding bit position. Writing a 0 has no effect on the flag. A

hardware reset or CHI command CLEAR_RAMS will also clear the register.

Figure 26-112 and Table 26-92 illustrate this register.

NOTE: An ECC single-bit error in the FTU RAM (TCR) is indicated by a dedicated TCR Single-Bit

Error Status (TSBESTAT) register.

When one of the flags SBEFA, SBEFB, SBEFC, SBEFD, SBEFE, SBEFF and SBEFG

changes from 0 to 1, the SBE flag is set to 1.

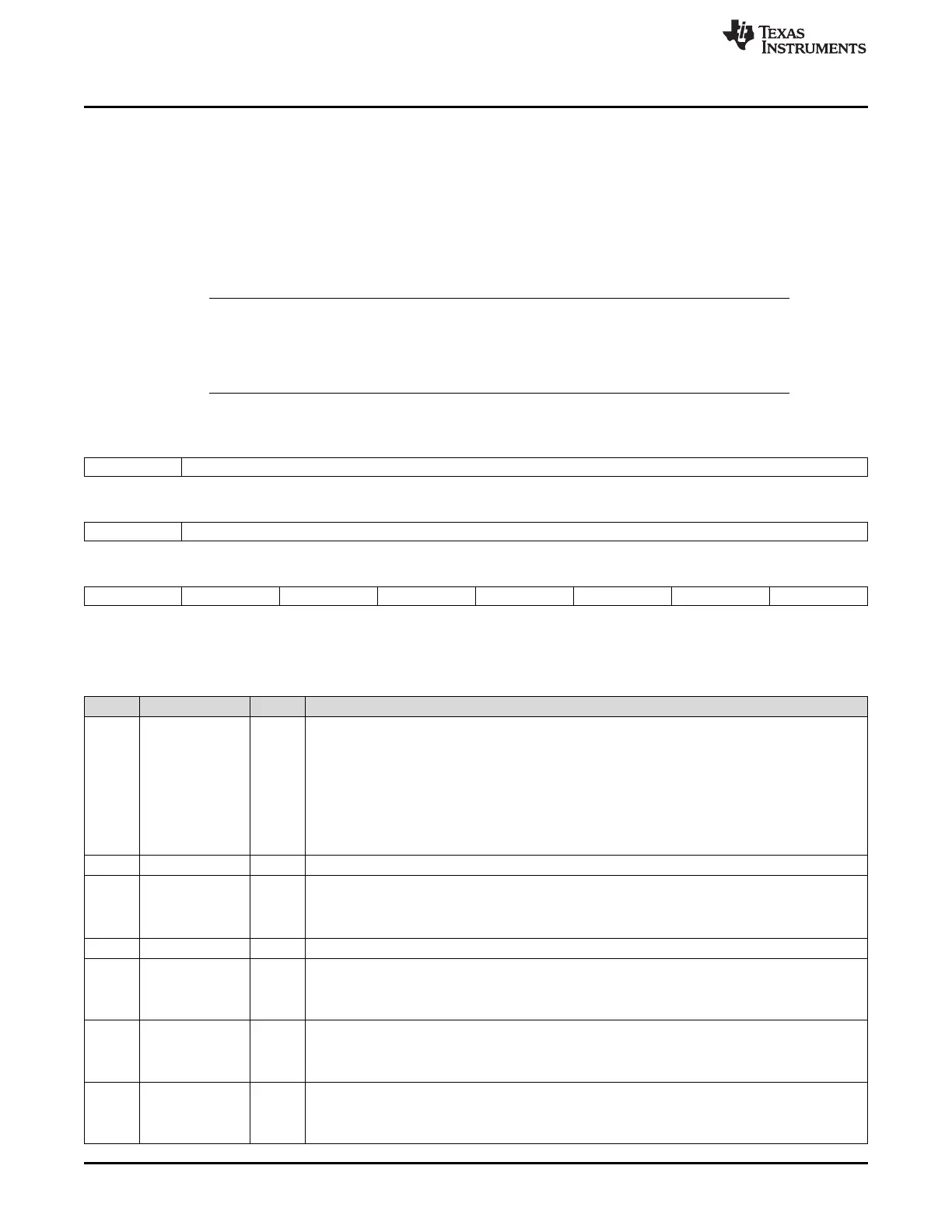

Figure 26-112. Single-Bit Error Status Register (SBESTAT) [offset_CC = 0Ch]

31 30 16

SBE Reserved

R/W1C-0 R-0

15 14 8

Reserved FMB

R-0 R/W1C-0

7 6 5 4 3 2 1 0

Reserved MFMB FMBD STBF2 STBF1 SMR SOBF SIBF

R-0 R/W1C-0 R/W1C-0 R/W1C-0 R/W1C-0 R/W1C-0 R/W1C-0 R/W1C-0

LEGEND: R/W = Read/Write; R = Read only; W1C = Write 1 to clear; -n = value after reset

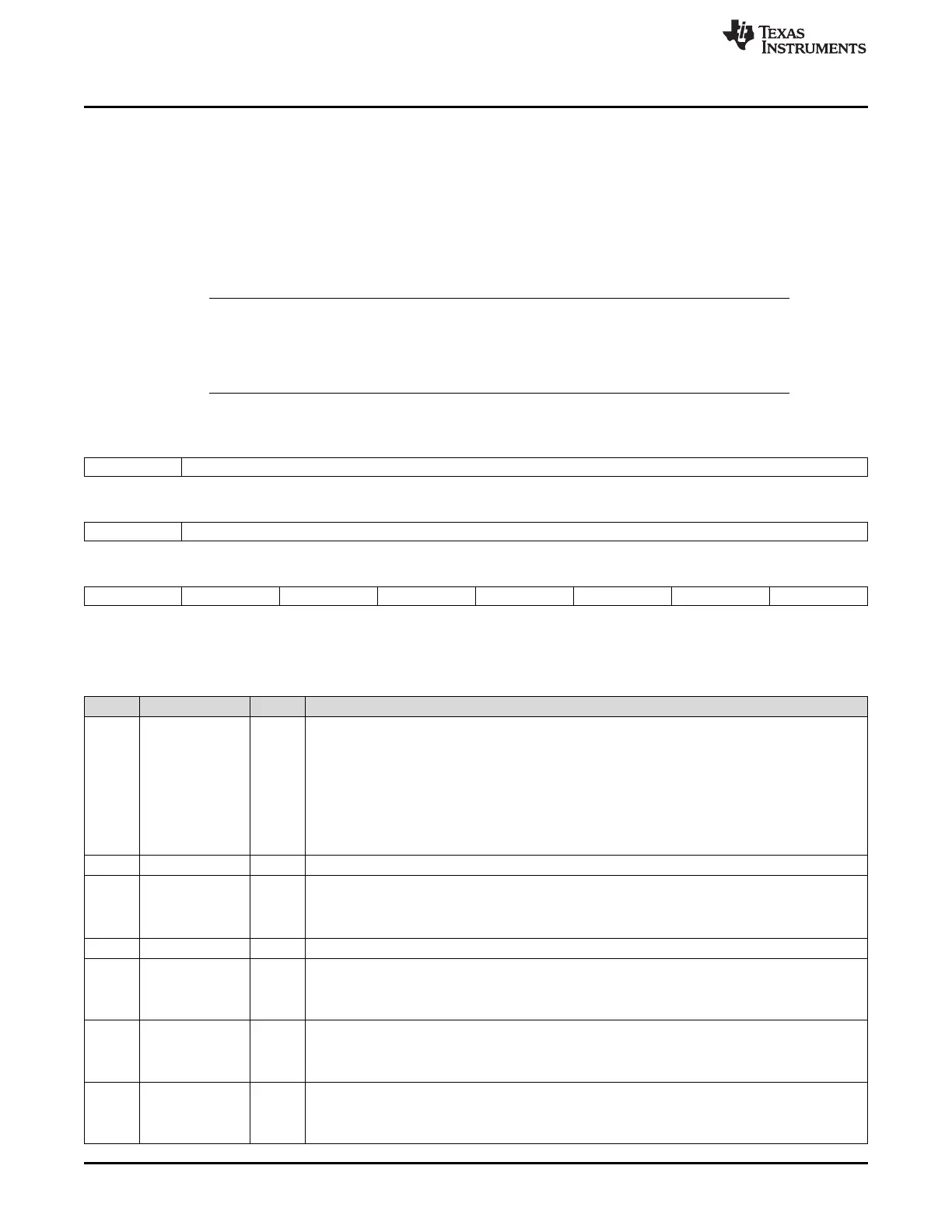

Table 26-92. Single-Bit Error Status Register (SBESTAT) Field Descriptions

Bit Field Value Description

31 SBE ECC Single-Bit Error. The flag signals an ECC single-bit error to the host. The flag is set by the

ECC logic of the communication controller, when it detects an ECC single-bit error while reading

from one of the FlexRay RAM blocks. This flag is set without regard to the SBEL bit setting in the

ECC Control Register (ECC_CTRL).

Note: ECC multi-bit errors are indicated by a separate PERR bit in the Error Interrupt Register

(EIR).

0 No ECC single-bit error occurred.

1 ECC single-bit error occurred.

30-15 Reserved 0 Reads return 0. Writes have no effect.

14-8 FMB 0-7Fh Faulty message buffer. An ECC single-bit error occurred when reading from a message buffer or

when transferring data from Input Buffer or Transient Buffer 1,2 to the message buffer referenced

by FMB. This value is only valid when one of the flags SIBF, SMR, STBF1, STBF2, and flag FMBD

is set. It is not updated while flag FMBD is set.

7 Reserved 0 Reads return 0. Writes have no effect.

6 MFMB Multiple message buffers with ECC single-bit error fault detected.

0 No additional faulty message buffer.

1 Another faulty message buffer was detected while flag FMBD is set.

5 FMBD Message buffer with ECC single-bit error fault detected.

0 No faulty message buffer.

1 Message buffer referenced by FMB holds faulty data due to an ECC single-bit error.

4 STBF2 ECC single-bit error in transient buffer RAM B.

0 No ECC single-bit error.

1 ECC single-bit error occurred when reading transient buffer RAM B.

Loading...

Loading...