www.ti.com

SCI/LIN Control Registers

1687

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Serial Communication Interface (SCI)/ Local Interconnect Network (LIN)

Module

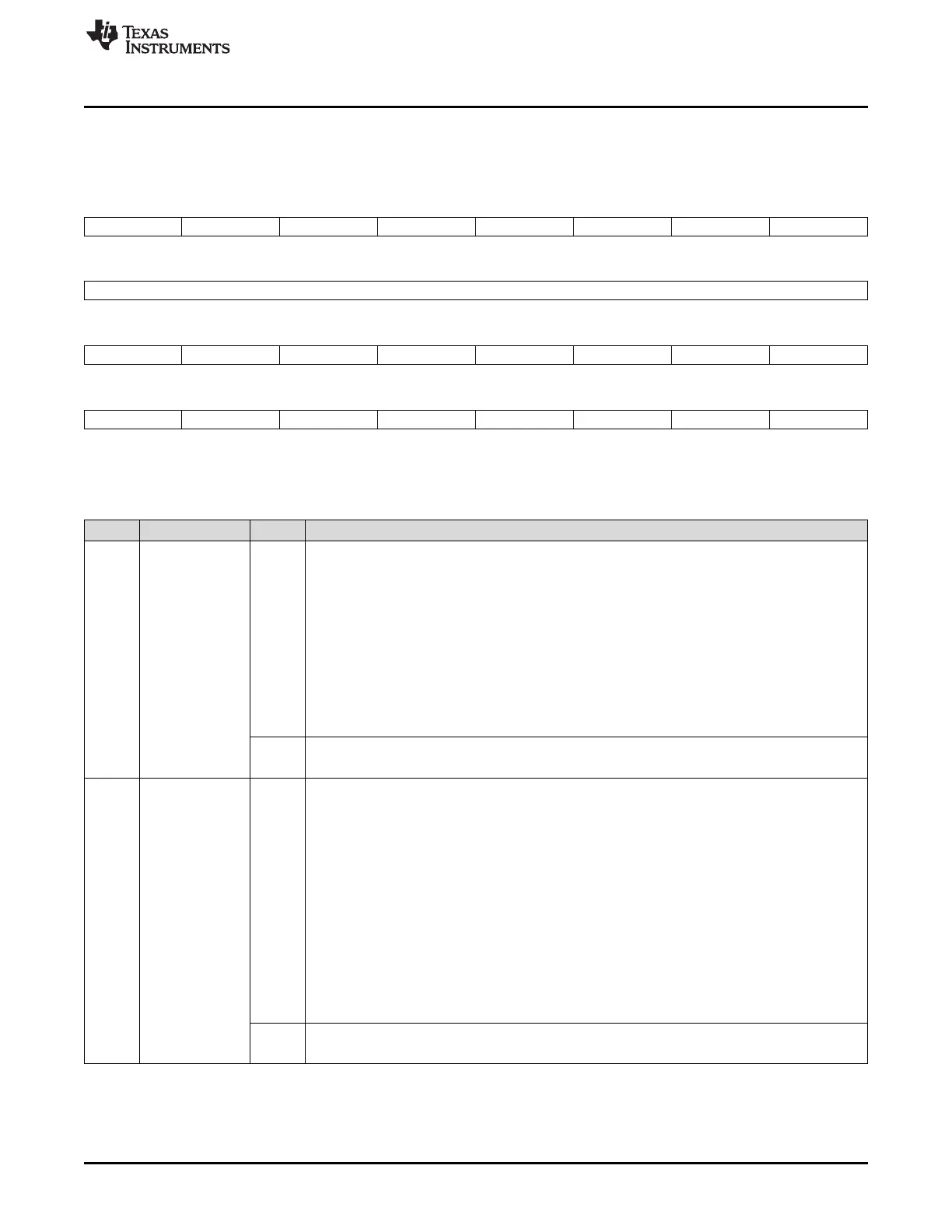

29.7.8 SCI Flags Register (SCIFLR)

Figure 29-35 and Table 29-20 illustrate this register.

Figure 29-35. SCI Flags Register (SCIFLR) (offset = 1Ch)

31 30 29 28 27 26 25 24

BE PBE CE ISFE NRE FE OE PE

R/WL-0 R/WL-0 R/WL-0 R/WL-0 R/WL-0 R/W-0 R/W-0 R/W-0

23 16

Reserved

R-0

15 14 13 12 11 10 9 8

Reserved ID RX ID TX RX WAKE TX EMPTY TX WAKE RX RDY TX RDY

R-0 R/WL-0 R/WL-0 R/WC-0 R/W-1 R/WC-0 R/W-0 R/W-1

7 6 5 4 3 2 1 0

TOA3WUS TOAWUS Reserved TIMEOUT BUSY IDLE WAKE UP BRKDT

R/WL-0 R/WL-0 R-0 R/WL-0 R/W-0 R-0 R/WL-0 R/WC-0

LEGEND: R/W = Read/Write; R = Read only; WC = Write in SCI-compatible mode only; WL = Write in LIN mode only; -n = value after reset

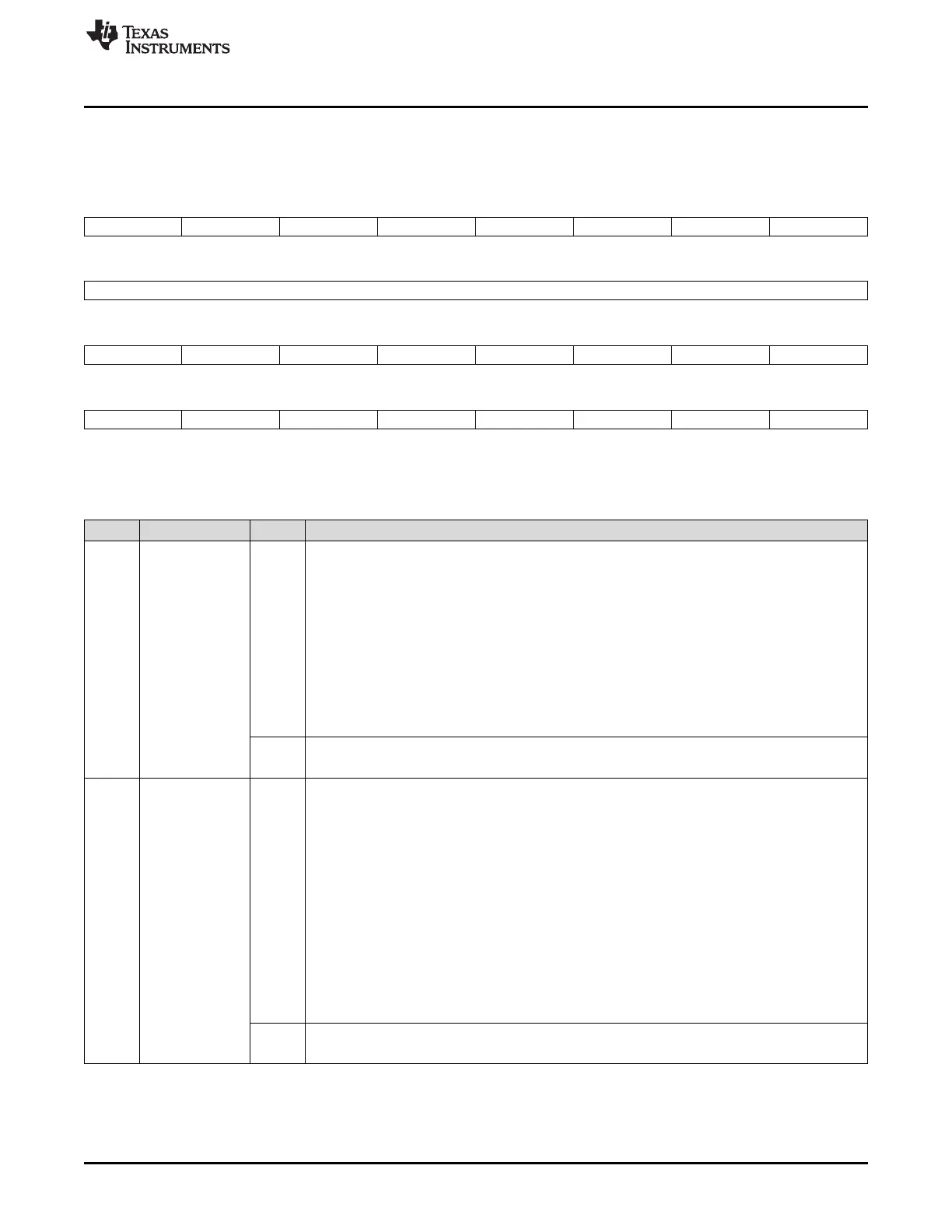

Table 29-20. SCI Flags Register (SCIFLR) Field Descriptions

Bit Field Value Description

31 BE Bit error flag. This bit is effective in LIN mode only. This bit is set when a bit error has occurred.

This is detected by the internal bit monitor. See Section 29.3.1.8 for more information. The bit error

flag is cleared by any of the following:

• Setting of the SWnRST bit

• Setting of the RESET bit

• A system reset

• Writing a 1 to this bit

• On reception of a new synch break

• Reading the corresponding interrupt offset in SCIINTVECT0/1

0 Read: No error has been detected since this bit was last cleared.

Write: No effect.

1 Read: An error has been detected since this bit was last cleared.

Write: The bit is cleared to 0.

30 PBE Physical bus error flag. This bit is effective in LIN mode only. This bit is set when a physical bus

error has been detected by the bit monitor in TED. See Section 29.3.1.8 for more information. The

physical bus error flag is cleared by the following:

• Setting of the SWnRST bit

• Setting of the RESET bit

• A system reset

• Writing a 1 to this bit

• On reception of a new synch break

• Reading the corresponding interrupt offset in SCIINTVECT0/1

Note: The PBE will only be flagged, if no Synch Break can be generated (for example,

because of a bus shortage to VBAT) or if no Synch Break Delimiter can be generated (for

example, because of a bus shortage to GND).

0 Read: No error has been detected since this bit was last cleared.

Write: No effect.

1 Read: An error has been detected since this bit was last cleared.

Write: The bit is cleared to 0.

Loading...

Loading...