System and Peripheral Control Registers

www.ti.com

178

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Architecture

2.5.1.27 SYS Pin Control Register 10 (SYSPC10)

The SYSPC10 register, shown in Figure 2-34 and described in Table 2-46, controls the function of the

ECPCLK slew mode.

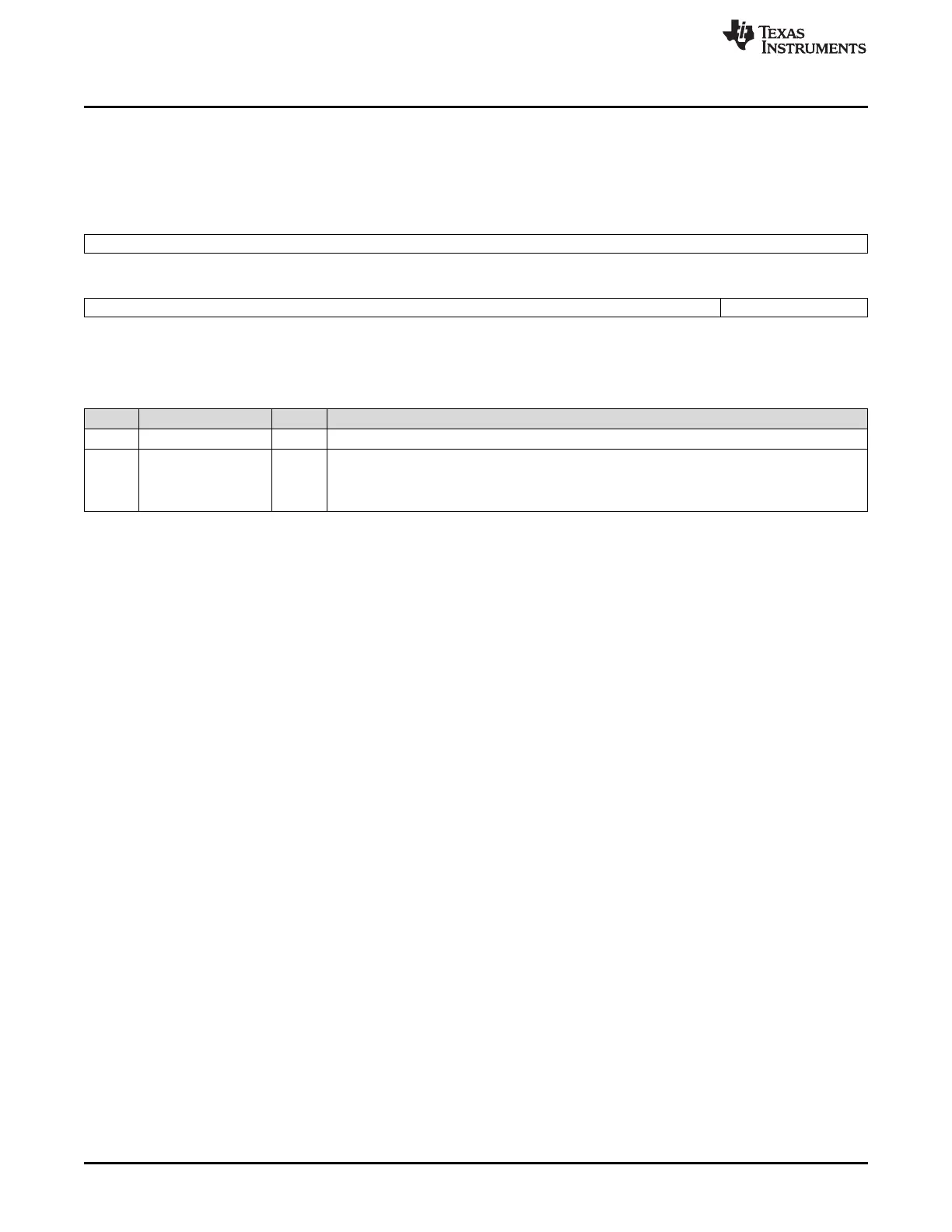

Figure 2-34. SYS Pin Control Register 10 (SYSPC10) (offset = 78h)

31 16

Reserved

R-0

15 1 0

Reserved ECPCLK_SLEW

R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

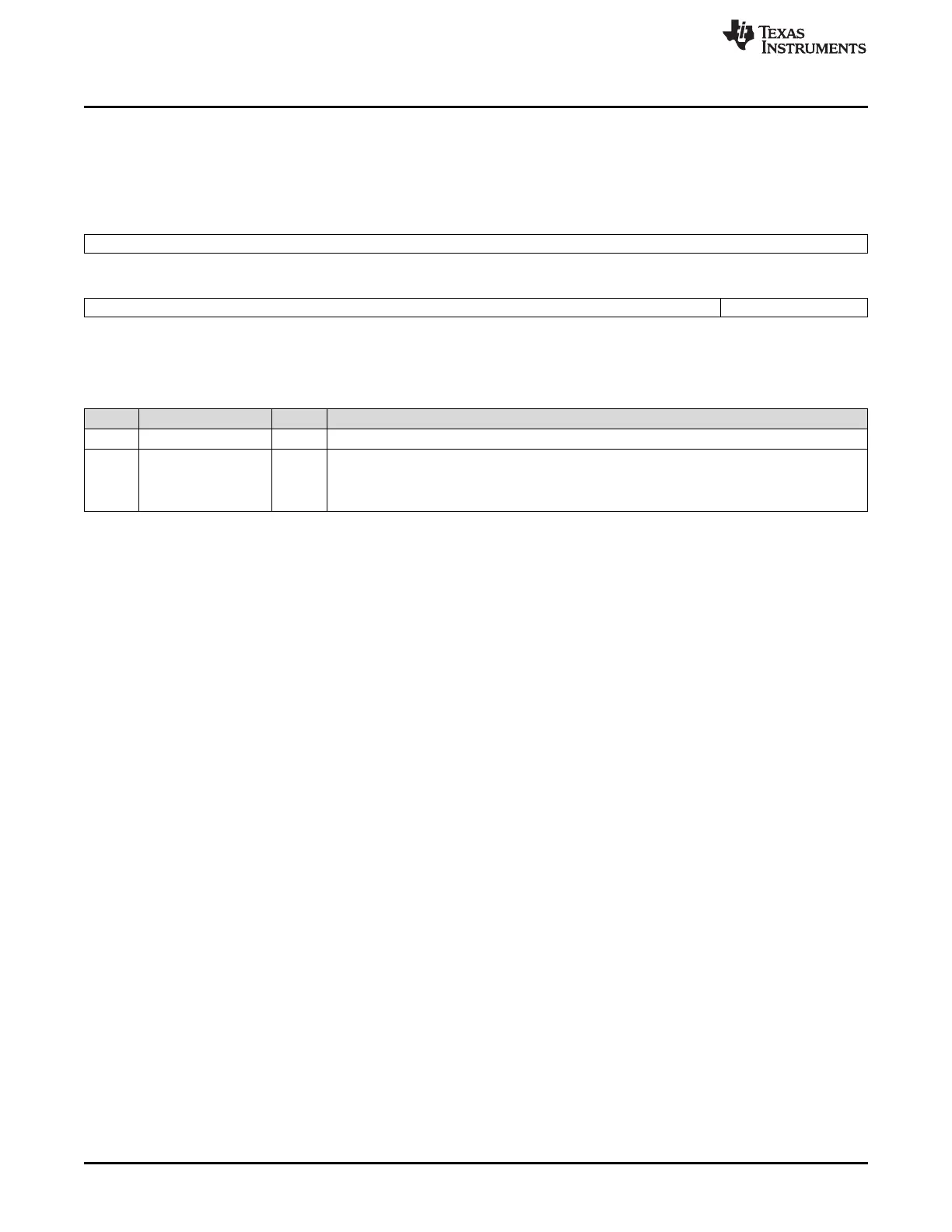

Table 2-46. SYS Pin Control Register 10 (SYSPC10) Field Descriptions

Bit Field Value Description

31-1 Reserved 0 Reads return 0. Writes have no effect.

0 ECPCLK_SLEW ECPCLK slew control. This bit controls between the fast or slow slew mode.

0 Fast mode is enabled; the normal output buffer is used for this pin.

1 Slow mode is enabled; slew rate control is used for this pin.

Loading...

Loading...