EMAC Control Module Registers

www.ti.com

1856

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

EMAC/MDIO Module

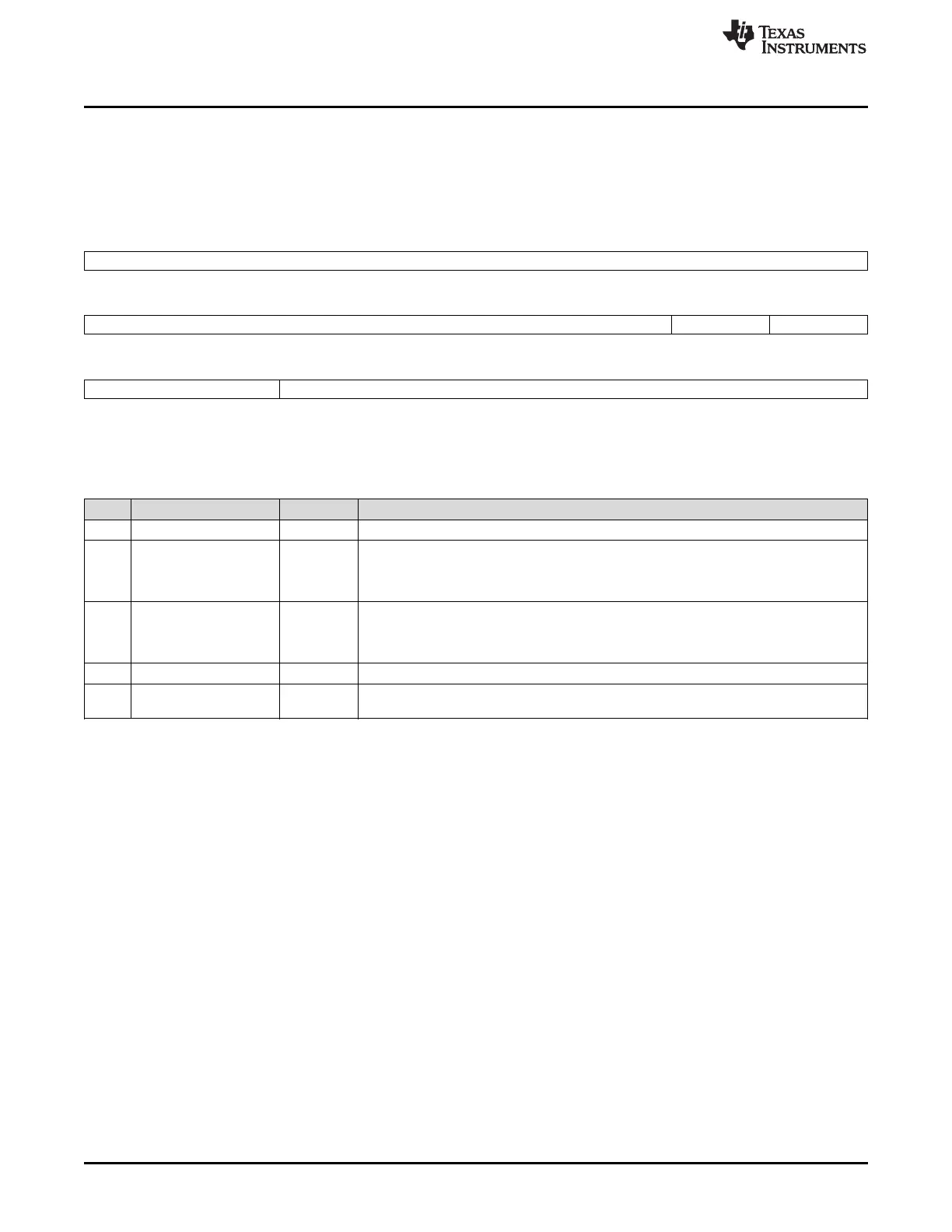

32.3.3 EMAC Control Module Interrupt Control Register (INTCONTROL)

The EMAC control module interrupt control register (INTCONTROL) is shown in Figure 32-17 and

described in Table 32-13. The settings in the INTCONTROL register are used in conjunction with the

CnRXIMAX and CnTXIMAX registers.

Figure 32-17. EMAC Control Module Interrupt Control Register (INTCONTROL) (offset = 0Ch)

31 24

Reserved

R-0

23 18 17 16

Reserved C0TXPACEEN C0RXPACEEN

R-0 R/W-0 R/W-0

15 12 11 0

Reserved INTPRESCALE

R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

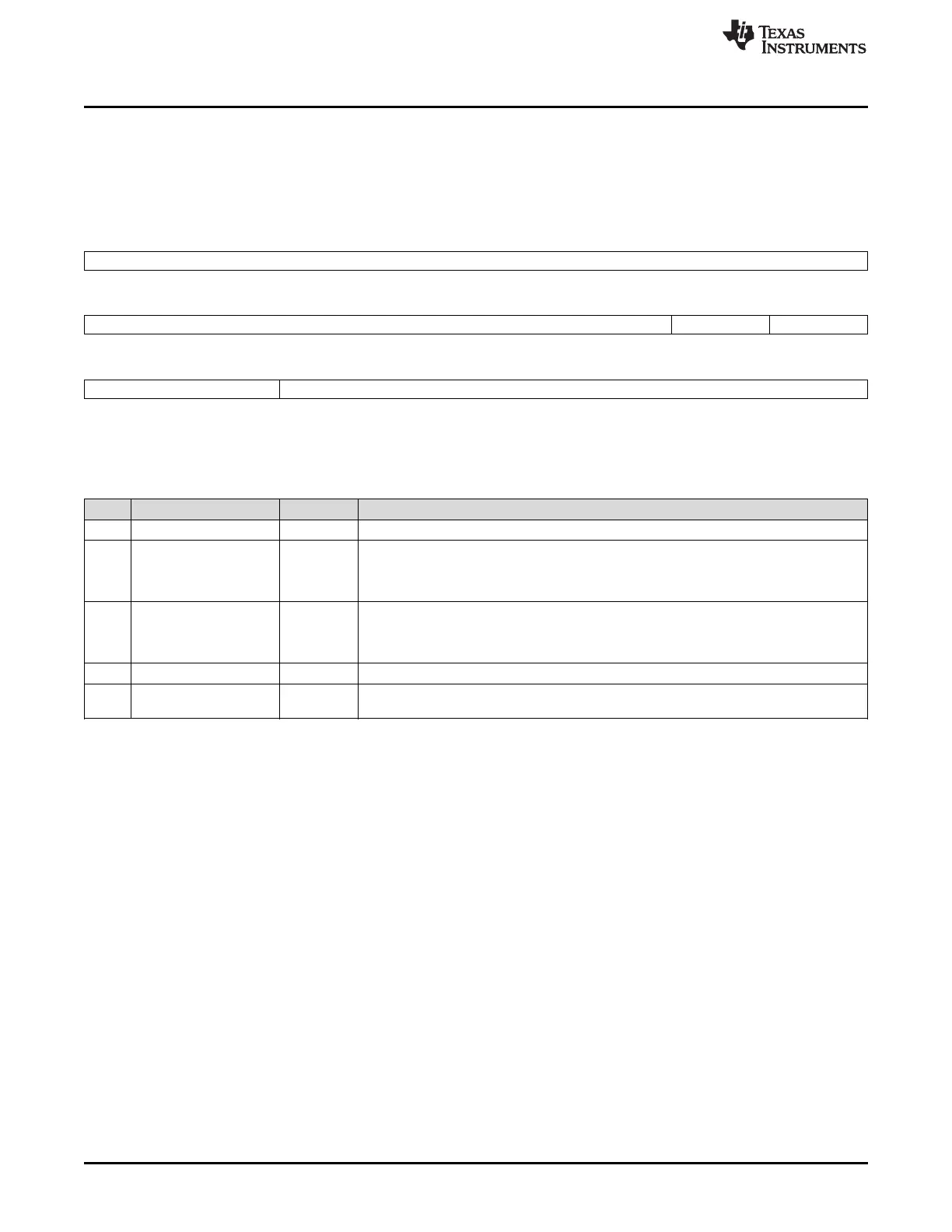

Table 32-13. EMAC Control Module Interrupt Control Register (INTCONTROL)

Bit Field Value Description

31-18 Reserved 0 Reserved

17 C0TXPACEEN Enable pacing for TX interrupt pulse generation.

0 Pacing for TX interrupts is disabled.

1 Pacing for TX interrupts is enabled.

16 C0RXPACEEN Enable pacing for RX interrupt pulse generation.

0 Pacing for RX interrupts is disabled.

1 Pacing for RX interrupts is enabled.

15-12 Reserved 0 Reserved

11-0 INTPRESCALE 0-7FFh Number of internal EMAC module reference clock periods within a 4 μs time window (see

your device-specific data manual for information).

Loading...

Loading...