System and Peripheral Control Registers

www.ti.com

240

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Architecture

2.5.3.30 Peripheral Frame 0 MasterID Protection Register_L (PS0MSTID_L)

There is one bit for each quadrant for PS0 to PS31.

NOTE: If a module occupies two quadrants, then only the lower quadrant register is used to enable

or disable the masterID. The upper quadrant register remains zeros.

The following are the ways that quadrants are used within a PS frame:

a. The slave uses all the four quadrants.

Only the bit corresponding to the quadrant 0 of PSn is implemented. It protects the whole 1K-byte

frame. The remaining three bits are not implemented.

b. The slave uses two quadrants.

Each quadrant has to be in one of these groups: (Quad 0 and Quad 1) or (Quad 2 and Quad 3).

For the group Quad0/Quad1, the bit quadrant 0 protects both quadrants 0 and 1. The bit quadrant 1 is

not implemented.

For the group Quad2/Quad3, the bit quadrant 2 protects both quadrants 2 and 3. The bit quadrant 3 is

not implemented

c. The slave uses only one quadrant.

In this case, the bit, as specified in Table 2-115, protects the slave.

The above arrangement is true for all the peripheral selects (PS0 to PS31), presented in Section 2.5.3.31 -

Section 2.5.3.32. This register holds bits for PS0 and is shown in Figure 2-101 and described in Table 2-

115.

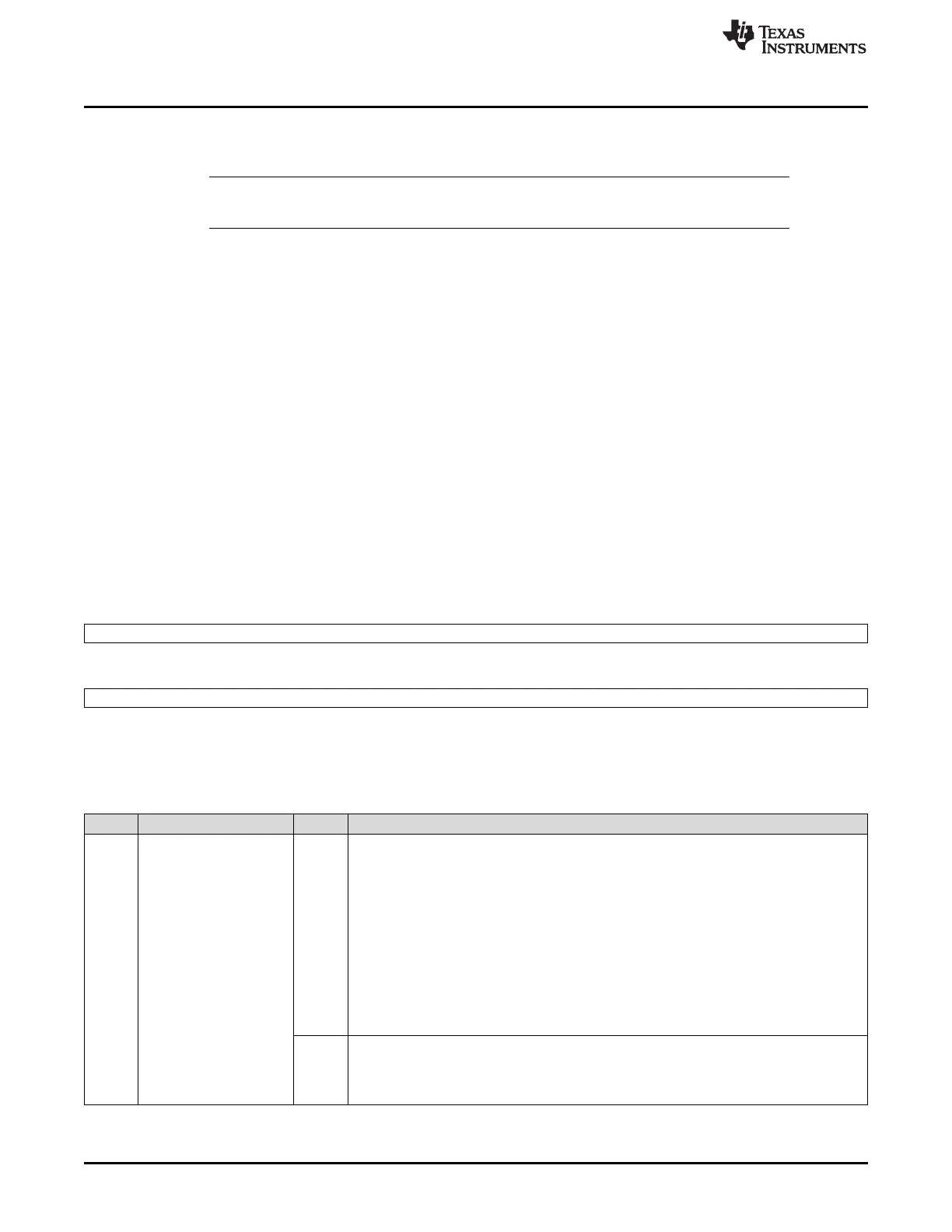

Figure 2-101. Peripheral Frame 0 MasterID Protection Register_L (PS0MSTID_L)

(offset = 300h)

31 16

PS0_QUAD1_MSTID

R/WP-FFFFh

15 0

PS0_QUAD0_MSTID

R/WP-FFFFh

LEGEND: R/W = Read/Write; WP = Write in privileged mode only; -n = value after reset

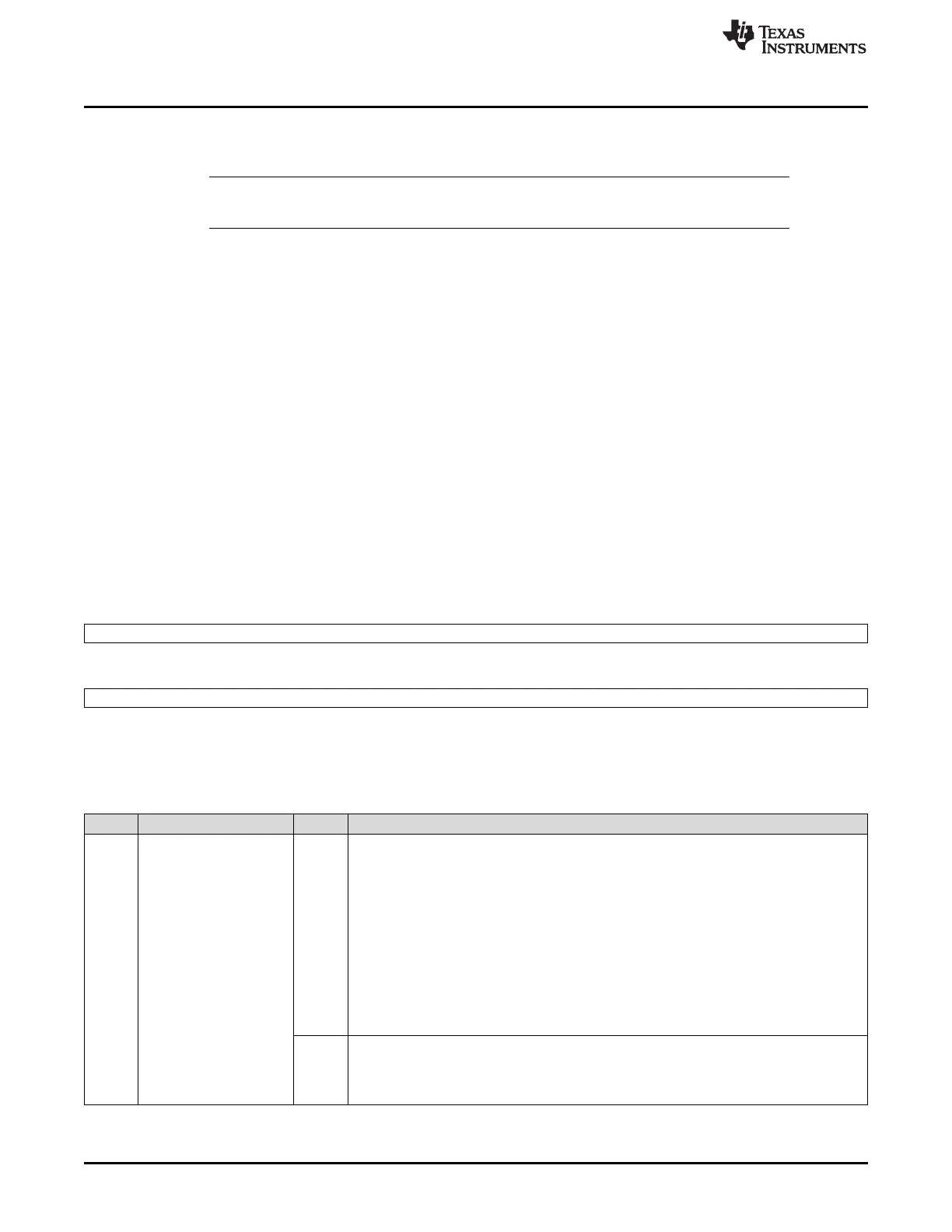

Table 2-115. Peripheral Frame 0 MasterID Protection Register_L (PS0MSTID_L)

Field Descriptions

Bit Field Value Description

31-16 PS0_QUAD1_MSTID MasterID filtering for Quadrant 1 of PS[0]. There are 16 bits for each quadrant in PS frame.

Each bit corresponds to a master-ID value. For example, bit 0 corresponds to master-ID 0

and bit 15 corresponds to master-ID 15. These bits set the permission for maximum of 16

masters to address the peripheral mapped in each of the quadrant.

The following examples shows the usage of these register bits.

(a) If bits 15:0 are 1010_1010_1010_1010, then the peripheral that is mapped to Quadrant

0 of PS[0] can be addressed by Masters with Master-ID equals to 1,3,5,7,9,11,13,15.

(b) if bits 15:0 are 0000_0000_0000_0001, then the peripheral that is mapped to Quadrant

0 of PS[0] can only addressed by the master with the Master-ID equal to 0.

0 Read: The corresponding master-ID is not permitted to access the peripheral mapped to

this quadrant.

Write: Disable the permission of the corresponding master to access the peripheral mapped

to this quadrant.

1 Read: The corresponding master-ID is permitted to access the peripheral mapped to this

quadrant.

Write: Enable the permission of the corresponding master to access the peripheral mapped

to this quadrant.

Loading...

Loading...