www.ti.com

ADC Registers

933

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Analog To Digital Converter (ADC) Module

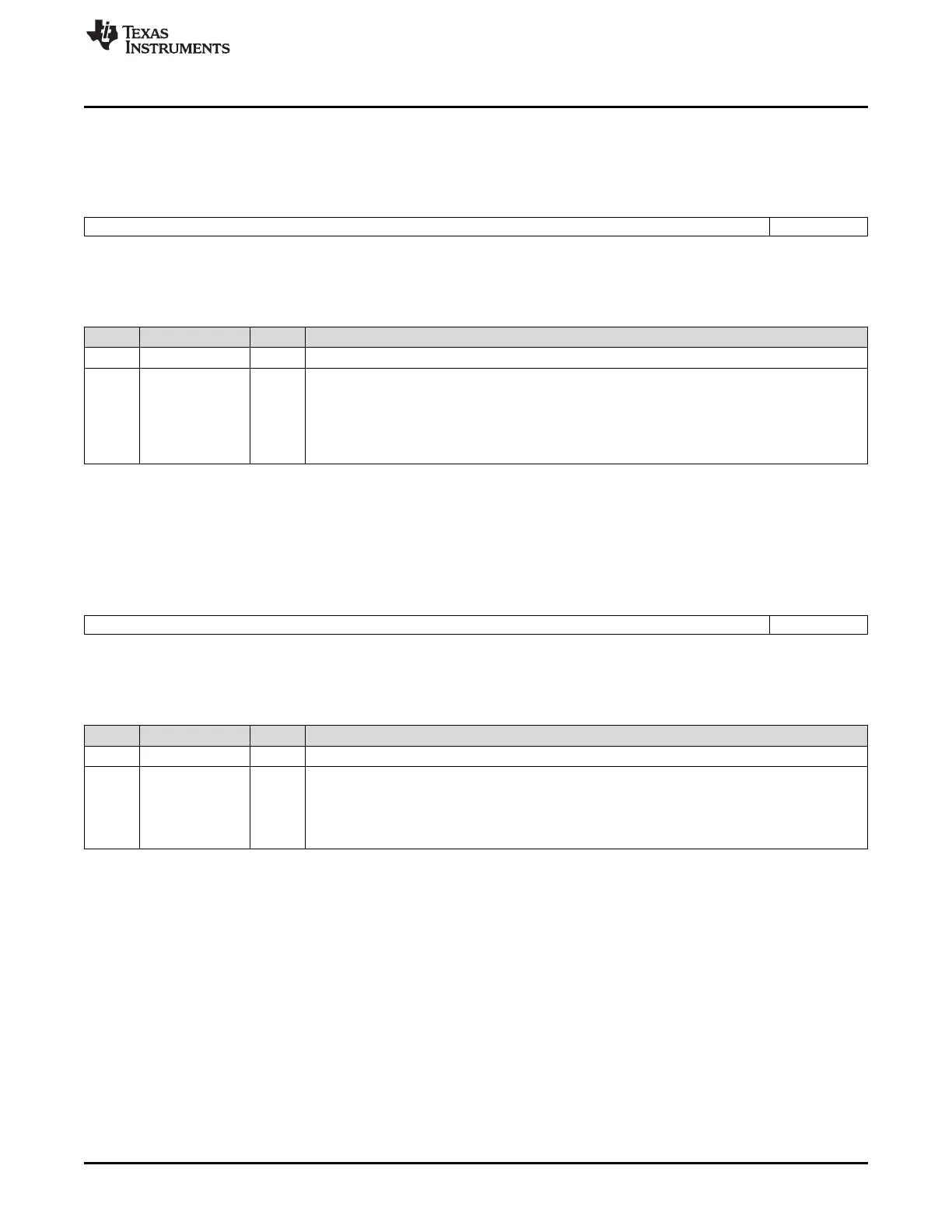

22.3.46 ADC ADEVT Pin Set Register (ADEVTSET)

ADC ADEVT Pin Set Register (ADEVTSET) is shown in Figure 22-75 and described in Table 22-52.

Figure 22-75. ADC ADEVT Pin Set Register (ADEVTSET) [offset = 108h]

31 1 0

Reserved ADEVT_SET

R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 22-52. ADC ADEVT Pin Set Register (ADEVTSET) Field Descriptions

Bit Field Value Description

31-1 Reserved 0 Reads return 0. Writes have no effect.

0 ADEVT_SET ADEVT Pin Set. This bit drives the output of the ADEVT pin high. A read from this bit always

returns the current state of the ADEVT pin.

Any operating mode read/write:

0 Output value on the ADEVT pin is unchanged.

1 Output logic HIGH on the ADEVT pin, if the pin is configured to be an output pin.

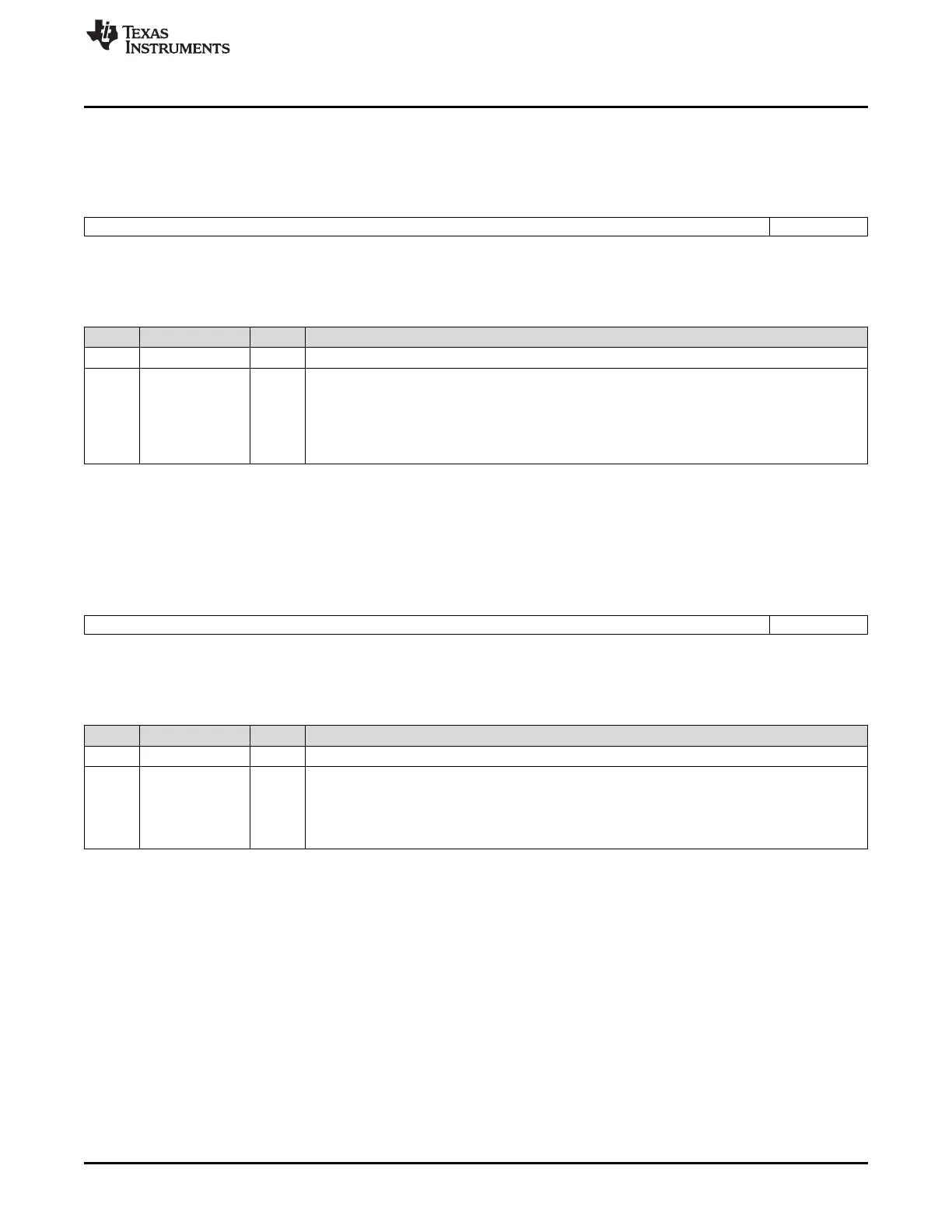

22.3.47 ADC ADEVT Pin Clear Register (ADEVTCLR)

ADC ADEVT Pin Clear Register (ADEVTCLR) is shown in Figure 22-76 and described in Table 22-53.

Figure 22-76. ADC ADEVT Pin Clear Register (ADEVTCLR) [offset = 10Ch]

31 1 0

Reserved ADEVT_CLR

R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 22-53. ADC ADEVT Pin Clear Register (ADEVTCLR) Field Descriptions

Bit Field Value Description

31-1 Reserved 0 Reads return 0. Writes have no effect.

0 ADEVT_CLR ADEVT Pin Clear. A read from this bit always returns the current state of the ADEVT pin.

Any operating mode read/write:

0 Output value on the ADEVT pin is unchanged.

1 Output logic LOW on the ADEVT pin, if the pin is configured to be an output pin.

Loading...

Loading...